## LM193-N, LM2903-N, LM293-N, LM393-N

SNOSBJ6G-OCTOBER 1999-REVISED OCTOBER 2018

# LMx93-N, LM2903-N Low-Power, Low-Offset Voltage, Dual Comparators

#### **Features**

Wide Supply

Voltage Range: 2.0 V to 36 V

Single or Dual Supplies: ±1.0 V to ±18 V

Very Low Supply Current Drain (0.4 mA) — Independent of Supply Voltage

Low Input Biasing Current: 25 nA

Low Input Offset Current: ±5 nA

Maximum Offset voltage: ±3 mV

Input Common-Mode Voltage Range Includes Ground

Differential Input Voltage Range Equal to the Power Supply Voltage

Low Output Saturation Voltage: 250 mV at 4 mA

Output Voltage Compatible with TTL, DTL, ECL, MOS and CMOS logic systems

Available in the 8-Bump (12 mil) DSBGA Package

See AN-1112 (SNVA009) for DSBGA Considerations

Advantages

**High Precision Comparators**

Reduced V<sub>OS</sub> Drift Over Temperature

Eliminates Need for Dual Supplies

Allows Sensing Near Ground

Compatible with All Forms of Logic

Power Drain Suitable for Battery Operation

## Applications

- **Battery Powered Applications**

- **Industrial Applications**

## 3 Description

The LM193-N series consists of two independent precision voltage comparators with an offset voltage specification as low as 2.0 mV max for two comparators which were designed specifically to operate from a single power supply over a wide range of voltages. Operation from split power supplies is also possible and the low power supply current drain is independent of the magnitude of the power supply voltage. These comparators also have a unique characteristic in that the input common-mode voltage range includes ground, even though operated from a single power supply voltage.

Application areas include limit comparators, simple analog to digital converters; pulse, squarewave and time delay generators; wide range VCO; MOS clock timers: multivibrators and high voltage digital logic gates. The LM193-N series was designed to directly interface with TTL and CMOS. When operated from both plus and minus power supplies, the LM19-N series will directly interface with MOS logic where their low power drain is a distinct advantage over standard comparators.

The LM393 and LM2903 parts are available in TI's innovative thin DSBGA package with 8 (12 mil) large bumps.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |

|-------------|-----------|-------------------|--|--|--|--|

| LM193-N     | TO 00 (8) | 0.00 mm v.0.00 mm |  |  |  |  |

| LM293-N     | TO-99 (8) | 9.08 mm x 9.08 mm |  |  |  |  |

| LM202 N     | SOIC (8)  | 4.90 mm x 3.91 mm |  |  |  |  |

| LM393-N     | DSBGA (8) | 1.54 mm x 1.54 mm |  |  |  |  |

| L M2002 N   | SOIC (8)  | 4.90 mm x 3.91 mm |  |  |  |  |

| LM2903-N    | DSBGA (8) | 1.54 mm x 1.54 mm |  |  |  |  |

<sup>(1)</sup> For all available packages, see the orderable addendum at the end of the datasheet.

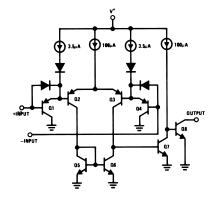

#### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                                                    |    | 7.1 Overview                                         | 10   |

|---|-------------------------------------------------------------------------------|----|------------------------------------------------------|------|

| 2 | Applications 1                                                                |    | 7.2 Functional Block Diagram                         | . 10 |

| 3 | Description 1                                                                 |    | 7.3 Feature Description                              | 10   |

| 4 | Revision History2                                                             |    | 7.4 Device Functional Modes                          | . 10 |

| 5 | Pin Configuration and Functions                                               | 8  | Application and Implementation                       | 11   |

| 6 | Specifications                                                                |    | 8.1 Application Information                          | . 11 |

| U | 6.1 Absolute Maximum Ratings                                                  |    | 8.2 Typical Applications                             | 11   |

|   | 6.2 ESD Ratings                                                               | 9  | Power Supply Recommendations                         | 18   |

|   | 6.3 Recommended Operating Conditions                                          | 10 | Layout                                               | 18   |

|   | 6.4 Thermal Information                                                       |    | 10.1 Layout Guidelines                               | 18   |

|   | 6.5 Electrical Characteristics: LM193A V <sup>+</sup> = 5 V, T <sub>A</sub> = |    | 10.2 Layout Example                                  | 18   |

|   | 25°C                                                                          | 11 | Device and Documentation Support                     | 19   |

|   | 6.6 Electrical Characteristics: LM193A (V+ = 5 V) 5                           |    | 11.1 Related Links                                   |      |

|   | 6.7 Electrical Characteristics: LMx93 and LM2903 V+= 5                        |    | 11.2 Receiving Notification of Documentation Updates | 19   |

|   | V, T <sub>A</sub> = 25°C6                                                     |    | 11.3 Trademarks                                      | 19   |

|   | 6.8 Electrical Characteristics: LMx93 and LM2903 (V+ =                        |    | 11.4 Electrostatic Discharge Caution                 | . 19 |

|   | 5 V) <sup>(1)</sup>                                                           |    | 11.5 Glossary                                        | 19   |

|   | 6.9 Typical Characteristics: LMx93 and LM193A 8                               | 12 | Mechanical, Packaging, and Orderable                 |      |

| _ | 6.10 Typical Characteristics: LM29039                                         |    | Information                                          | 19   |

| 7 | Detailed Description 10                                                       |    |                                                      |      |

|   |                                                                               |    |                                                      |      |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| •  | Added DSBGA packages inadvertantly omitted from Device Info table during format conversion                                                                                                                                                                                                                                   | 1    |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CI | nanges from Revision E (March 2013) to Revision F                                                                                                                                                                                                                                                                            | Page |

| •  | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |      |

| CI | nanges from Revision D (March 2013) to Revision E                                                                                                                                                                                                                                                                            | Page |

| _  | Changed layout of National Data Sheet to TI format                                                                                                                                                                                                                                                                           |      |

Submit Documentation Feedback

Copyright © 1999–2018, Texas Instruments Incorporated

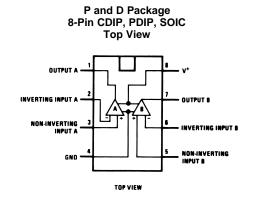

# 5 Pin Configuration and Functions

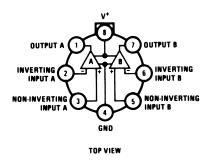

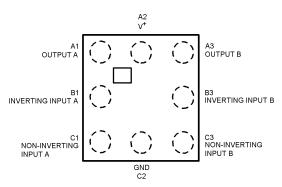

LMC Package 8-Pin TO-99 Top View

YZR Package 8-Pin DSBGA Top View

#### **Pin Functions**

|      | PIN                           |    |     |                               |  |  |  |  |

|------|-------------------------------|----|-----|-------------------------------|--|--|--|--|

|      | NO. PDIP/SOIC/<br>TO-99 DSBGA |    | 1/0 | DESCRIPTION                   |  |  |  |  |

| NAME |                               |    | .,, |                               |  |  |  |  |

| OUTA | 1                             | A1 | 0   | Output, Channel A             |  |  |  |  |

| -INA | 2                             | B1 | I   | Inverting Input, Channel A    |  |  |  |  |

| +INA | 3                             | C1 | I   | Noninverting Input, Channel A |  |  |  |  |

| GND  | 4                             | C2 | Р   | Ground                        |  |  |  |  |

| +INB | 5                             | C3 | I   | Noninverting Input, Channel B |  |  |  |  |

| -INB | 6                             | В3 | I   | Inverting Input, Channel B    |  |  |  |  |

| OUTB | 7                             | A3 | 0   | Output, Channel B             |  |  |  |  |

| V+   | 8                             | A2 | Р   | Positive power supply         |  |  |  |  |

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                   |                                                       |                          | MIN  | MAX            | UNIT |

|-------------------|-------------------------------------------------------|--------------------------|------|----------------|------|

| Differential Inpu | ıt Voltage <sup>(4)</sup>                             |                          |      | 36             | V    |

| Input Voltage     |                                                       |                          | -0.3 | 36             | V    |

| Input Current (\  | nput Current (V <sub>IN</sub> <-0.3 V) <sup>(5)</sup> |                          |      |                | mA   |

| Power             | PDIP                                                  |                          |      | 780            | mW   |

| Dissipation (6)   | TO-99                                                 |                          |      | 660            | mW   |

| ·<br>             | SOIC                                                  |                          |      | 510            | mW   |

|                   | DSBGA                                                 |                          |      | 568            | mW   |

| Output Short-Ci   | ircuit to Ground (7)                                  |                          |      | Continu<br>ous |      |

| Lead Temperat     | ure (Soldering, 10 sec                                | onds)                    |      | 260            | °C   |

| Soldering         | PDIP Package Solo                                     | lering (10 seconds)      |      | 260            | °C   |

| Information       | SOIC Package                                          | Vapor Phase (60 seconds) |      | 215            | °C   |

|                   |                                                       | Infrared (15 seconds)    |      | 220            | °C   |

| Storage temper    | ature, T <sub>stg</sub>                               | -65                      | 150  | °C             |      |

- (1) Absolute Maximum Ratings indicate limits beyond which damage may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

- (2) Refer to RETS193AX for LM193AH military specifications and to RETS193X for LM193H military specifications.

- (3) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

- (4) Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than -0.3V (or 0.3V below the magnitude of the negative power supply, if used).

- (5) This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V<sup>+</sup> voltage level (or to ground for a large overdrive) for the time duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns to a value greater than -0.3V.

- (6) For operating at high temperatures, the LM393 and LM2903 must be derated based on a 125°C maximum junction temperature and a thermal resistance of 170°C/W which applies for the device soldered in a printed circuit board, operating in a still air ambient. The LM193/LM193A/LM293 must be derated based on a 150°C maximum junction temperature. The low bias dissipation and the "ON-OFF" characteristic of the outputs keeps the chip dissipation very small (P<sub>D</sub>≤100 mW), provided the output transistors are allowed to saturate.

- (7) Short circuits from the output to V<sup>+</sup> can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output current is approximately 20 mA independent of the magnitude of V<sup>+</sup>.

#### 6.2 ESD Ratings

|                    |                         |                                                        | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±1300 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                               | MIN  | NOM MAX    | UNIT |

|---------------------------------------------------------------|------|------------|------|

| Supply Voltage (V+) - Single Supply                           | 2.0  | 36         | V    |

| Supply Voltage (V+) - Dual Supply                             | ±1.0 | ±18        | V    |

| Operating Input Voltage on (VIN pin)                          | 0    | (V+) -1.5V | V    |

| Operating junction temperature, T <sub>J</sub> : LM193/LM193A | -55  | 125        | °C   |

| Operating junction temperature, T <sub>J</sub> : LM2903       | -40  | 85         | °C   |

| Operating junction temperature, T <sub>J</sub> : LM293        | -25  | 85         | °C   |

| Operating junction temperature, T <sub>J</sub> : LM393        | 0    | 70         | °C   |

Submit Documentation Feedback

Copyright © 1999–2018, Texas Instruments Incorporated

#### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> | LMx93                           |        |      |  |  |

|-------------------------------|---------------------------------|--------|------|--|--|

|                               | THERMAL METRIC <sup>(1)</sup>   |        |      |  |  |

|                               |                                 | 8 PINS |      |  |  |

| R <sub>θJA</sub> Junction     | n-to-ambient thermal resistance | 170    | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics: LM193A V<sup>+</sup>= 5 V, T<sub>A</sub> = 25°C

Unless otherwise stated.

| DADAMETED                       |                                                                | TEST CONDITIONS                                       |     | LINUT |                     |      |

|---------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-----|-------|---------------------|------|

| PARAMETER                       |                                                                | TEST CONDITIONS                                       | MIN | TYP   | MAX                 | UNIT |

| Input Offset Voltage            | See <sup>(1)</sup> .                                           |                                                       |     | 1.0   | 2.0                 | mV   |

| Input Bias Current              | I <sub>IN</sub> (+) or I <sub>IN</sub>                         | (-) with Output In Linear Range, $V_{CM} = 0 V^{(2)}$ |     | 25    | 100                 | nA   |

| Input Offset Current            | I <sub>IN</sub> (+)-I <sub>IN</sub> (-)                        | $V_{CM} = 0 V$                                        |     | 3.0   | 25                  | nA   |

| Input Common Mode Voltage Range | V+ = 30 V                                                      | (3)                                                   | 0   |       | V <sup>+</sup> −1.5 | ٧    |

| Supply Current                  | R <sub>L</sub> =∞                                              | R <sub>L</sub> =∞ V <sup>+</sup> =5 V                 |     | 0.4   | 1                   | mA   |

|                                 |                                                                | V+=36 V                                               |     | 1     | 2.5                 | mA   |

| Voltage Gain                    | R <sub>L</sub> ≥15 kΩ,<br>V <sub>O</sub> = 1 V to              |                                                       | 50  | 200   |                     | V/mV |

| Large Signal Response Time      | V <sub>IN</sub> =TTL Lo<br>V <sub>RL</sub> =5V, R <sub>L</sub> | ogic Swing, V <sub>REF</sub> =1.4 V<br>=5.1 kΩ        |     | 300   |                     | ns   |

| Response Time                   | V <sub>RL</sub> =5V, R <sub>L</sub>                            | =5.1 kΩ <sup>(4)</sup>                                |     | 1.3   |                     | μS   |

| Output Sink Current             | V <sub>IN</sub> (−)=1V,                                        | V <sub>IN</sub> (+)=0, V <sub>O</sub> ≈1.5 V          | 6.0 | 16    |                     | mA   |

| Saturation Voltage              | V <sub>IN</sub> (−)=1V,                                        | V <sub>IN</sub> (+)=0, I <sub>SINK</sub> ≤4 mA        |     | 250   | 400                 | mV   |

| Output Leakage Current          | V <sub>IN</sub> (-)=0, V                                       | <sub>IN</sub> (+)=1V, V <sub>O</sub> =5 V             |     | 0.1   |                     | nA   |

- (1) At output switch point, V<sub>Ω</sub>≃1.4V, R<sub>S</sub>= 0 Ω with V<sup>+</sup> from 5V to 30V; and over the full input common-mode range (0V to V<sup>+</sup>−1.5V), at 25°C.

- (2) The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines.

- (3) The input common-mode voltage or either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is V<sup>+</sup>-1.5 V at 25°C, but either or both inputs can go to 36 V without damage, independent of the magnitude of V<sup>+</sup>.

- (4) The response time specified is for a 100 mV input step with 5 mV overdrive. For larger overdrive signals 300 ns can be obtained, see LMx93 and LM193A Typical Characteristics.

# 6.6 Electrical Characteristics: LM193A (V+ = 5 V)<sup>(1)</sup>

| PARAMETER                       | TEST CONDITIONS                                                               |     | UNIT |        |      |

|---------------------------------|-------------------------------------------------------------------------------|-----|------|--------|------|

| PARAMETER                       | TEST CONDITIONS                                                               | MIN | TYP  | MAX    | UNIT |

| Input Offset Voltage            | See (2)                                                                       |     |      | 4.0    | mV   |

| Input Offset Current            | I <sub>IN(+)</sub> -I <sub>IN(-)</sub> , V <sub>CM</sub> =0 V                 |     |      | 100    | nA   |

| Input Bias Current              | $I_{IN}(+)$ or $I_{IN}(-)$ with Output in Linear Range, $V_{CM}=0$ V $^{(3)}$ |     |      | 300    | nA   |

| Input Common Mode Voltage Range | V+=30 V (4)                                                                   | 0   |      | V+-2.0 | V    |

| Saturation Voltage              | $V_{IN}(-)=1V, V_{IN}(+)=0, I_{SINK} \le 4 \text{ mA}$                        |     |      | 700    | mV   |

| Output Leakage Current          | V <sub>IN</sub> (-)=0, V <sub>IN(+)</sub> =1V, V <sub>O</sub> =30 V           |     |      | 1.0    | μΑ   |

| Differential Input Voltage      | Keep All V <sub>IN</sub> 's≥0 V (or V <sup>-</sup> , if Used), <sup>(5)</sup> |     |      | 36     | V    |

- (1) These specifications are limited to -55°C≤T<sub>A</sub>≤+125°C, for the LM193/LM193A. With the LM293 all temperature specifications are limited to -25°C≤T<sub>A</sub>≤+85°C and the LM393 temperature specifications are limited to 0°C≤T<sub>A</sub>≤+70°C. The LM2903 is limited to -40°C≤T<sub>A</sub>≤+85°C.

- (2) At output switch point,  $V_0$ =1.4V,  $R_S$ = 0  $\Omega$  with V<sup>+</sup> from 5V to 30V; and over the full input common-mode range (0V to V<sup>+</sup>-1.5V), at 25°C.

- (3) The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines.

- (4) The input common-mode voltage or either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is V<sup>+</sup>-1.5 V at 25°C, but either or both inputs can go to 36 V without damage, independent of the magnitude of V<sup>+</sup>.

- (5) Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than −0.3V (or 0.3V below the magnitude of the negative power supply, if used).

Copyright © 1999–2018, Texas Instruments Incorporated

Submit Documentation Feedback

# 6.7 Electrical Characteristics: LMx93 and LM2903 $V^+$ = 5 V, $T_A$ = 25°C

Unless otherwise stated.

|                                    |                                                  |                                                              | L   | M193-N |            | LM293 | 3-N, LN | 1393-N     | L       | M2903 | B-N        |      |

|------------------------------------|--------------------------------------------------|--------------------------------------------------------------|-----|--------|------------|-------|---------|------------|---------|-------|------------|------|

| PARAMETER                          | TES                                              | ST CONDITIONS                                                | MIN | TYP    | MAX        | MIN   | TYP     | MAX        | MI<br>N | TYP   | MAX        | UNIT |

| Input Offset Voltage               | See (1)                                          |                                                              |     | 1.0    | 5.0        |       | 1.0     | 5.0        |         | 2.0   | 7.0        | mV   |

| Input Bias Current                 |                                                  | $V_{\rm C}(-)$ with Output In nge, $V_{\rm CM}=0$ V $^{(2)}$ |     | 25     | 100        |       | 25      | 250        |         | 25    | 250        | nA   |

| Input Offset Current               | $I_{IN}(+)-I_{IN}(-$                             | -) V <sub>CM</sub> = 0 V                                     |     | 3.0    | 25         |       | 5.0     | 50         |         | 5.0   | 50         | nA   |

| Input Common Mode<br>Voltage Range | V+ = 30 V <sup>(3)</sup>                         |                                                              | 0   |        | V+−1.<br>5 | 0     |         | V+−1.<br>5 | 0       |       | V+−1.<br>5 | ٧    |

| Supply Current                     | R <sub>L</sub> =∞                                | V+=5 V                                                       |     | 0.4    | 1          |       | 0.4     | 1          |         | 0.4   | 1.0        | mA   |

|                                    |                                                  | V+=36 V                                                      |     | 1      | 2.5        |       | 1       | 2.5        |         | 1     | 2.5        | mA   |

| Voltage Gain                       | R <sub>L</sub> ≥15 kΩ,<br>V <sub>O</sub> = 1 V t |                                                              | 50  | 200    |            | 50    | 200     |            | 25      | 100   |            | V/mV |

| Large Signal Response<br>Time      | V                                                | ogic Swing, $V_{REF}$ =1.4<br>$R_L$ =5.1 k $\Omega$          |     | 300    |            |       | 300     |            |         | 300   |            | ns   |

| Response Time                      | V <sub>RL</sub> =5 V, I                          | $R_L = 5.1 \text{ k}\Omega^{-(4)}$                           |     | 1.3    |            |       | 1.3     |            |         | 1.5   |            | μS   |

| Output Sink Current                | V <sub>IN</sub> (−)=1 \                          | /, V <sub>IN</sub> (+)=0, V <sub>O</sub> ≤1.5 V              | 6.0 | 16     |            | 6.0   | 16      |            | 6.0     | 16    |            | mA   |

| Saturation Voltage                 | V <sub>IN</sub> (−)=1 \                          | /, V <sub>IN</sub> (+)=0, I <sub>SINK</sub> ≤4 mA            |     | 250    | 400        |       | 250     | 400        |         | 250   | 400        | mV   |

| Output Leakage Current             | V <sub>IN</sub> (-)=0, '                         | V <sub>IN</sub> (+)=1V, V <sub>O</sub> =5 V                  |     | 0.1    |            |       | 0.1     |            |         | 0.1   |            | nA   |

Submit Documentation Feedback

At output switch point,  $V_0 \approx 1.4 \text{V}$ ,  $R_S = 0~\Omega$  with V<sup>+</sup> from 5V to 30V; and over the full input common-mode range (0V to V<sup>+</sup>-1.5V), at 25°C. The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines.

The input common-mode voltage or either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is V+-1.5 V at 25°C, but either or both inputs can go to 36 V without damage, independent of the magnitude of V+.

The response time specified is for a 100 mV input step with 5 mV overdrive. For larger overdrive signals 300 ns can be obtained, see LMx93 and LM193A Typical Characteristics .

# 6.8 Electrical Characteristics: LMx93 and LM2903 (V+ = 5 V)<sup>(1)</sup>

| DADAMETED                          | TEST COMPITIONS                                                                             | LI  | M193-N | 1                 | LM293-N, LM393-N |     |                    | L   | 1   | LINUT                   |      |

|------------------------------------|---------------------------------------------------------------------------------------------|-----|--------|-------------------|------------------|-----|--------------------|-----|-----|-------------------------|------|

| PARAMETER                          | TEST CONDITIONS                                                                             | MIN | TYP    | MAX               | MIN              | TYP | MAX                | MIN | TYP | MAX                     | UNIT |

| Input Offset Voltage               | See (2)                                                                                     |     |        | 9                 |                  |     | 9                  |     | 9   | 15                      | mV   |

| Input Offset Current               | $I_{IN(+)} - I_{IN(-)}, V_{CM} = 0 V$                                                       |     |        | 100               |                  |     | 150                |     | 50  | 200                     | nA   |

| Input Bias Current                 | $I_{\rm IN}(+)$ or $I_{\rm IN}(-)$ with Output in Linear Range, $V_{\rm CM}{=}0$ V $^{(3)}$ |     |        | 300               |                  |     | 400                |     | 200 | 500                     | nA   |

| Input Common Mode<br>Voltage Range | V <sup>+</sup> =30V <sup>(4)</sup>                                                          | 0   |        | V <sup>+</sup> -2 | 0                |     | V <sup>+</sup> -2. | 0   |     | V <sup>+</sup> -2<br>.0 | V    |

| Saturation Voltage                 | $V_{IN}(-)=1V, V_{IN}(+)=0, I_{SINK} \le 4 \text{ mA}$                                      |     |        | 700               |                  |     | 700                |     | 400 | 700                     | mV   |

| Output Leakage Current             | $V_{IN}(-)=0, V_{IN(+)}=1V, V_{O}=30 V$                                                     |     |        | 1.0               |                  |     | 1.0                |     |     | 1.0                     | μΑ   |

| Differential Input Voltage         | Keep All V <sub>IN</sub> 's≥0 V (or V <sup>-</sup> , if Used), <sup>(5)</sup>               |     |        | 36                |                  |     | 36                 |     |     | 36                      | V    |

- (1) These specifications are limited to -55°C≤T<sub>A</sub>≤+125°C, for the LM193/LM193A. With the LM293 all temperature specifications are limited to -25°C≤T<sub>A</sub>≤+85°C and the LM393 temperature specifications are limited to 0°C≤T<sub>A</sub>≤+70°C. The LM2903 is limited to -40°C≤T<sub>A</sub>≤+85°C.

- (2) At output switch point, V<sub>O</sub>≃1.4V, R<sub>S</sub>= 0 Ω with V<sup>+</sup> from 5V to 30V; and over the full input common-mode range (0V to V<sup>+</sup>−1.5V), at 25°C.

- (3) The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines.

- (4) The input common-mode voltage or either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is V<sup>+</sup>-1.5 V at 25°C, but either or both inputs can go to 36 V without damage, independent of the magnitude of V<sup>+</sup>.

- (5) Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than −0.3V (or 0.3V below the magnitude of the negative power supply, if used).

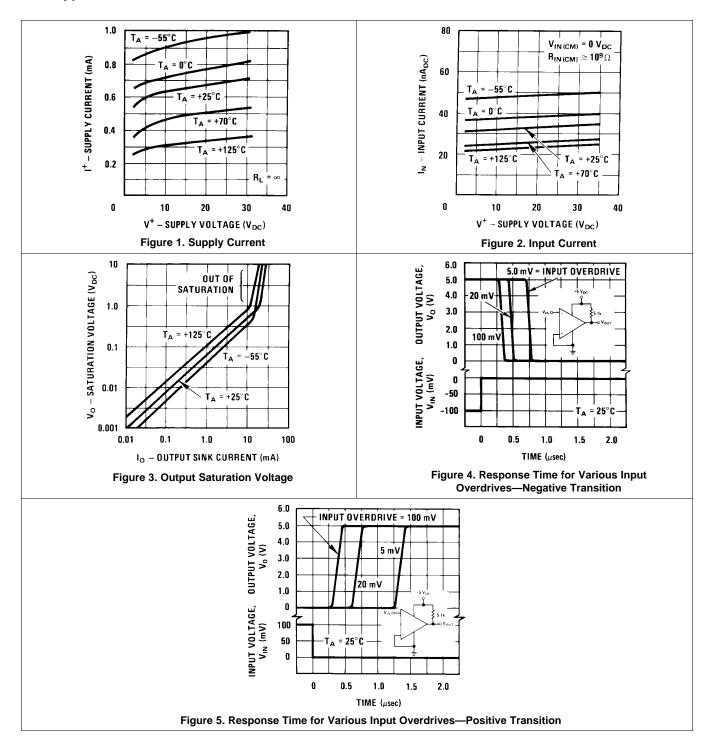

## 6.9 Typical Characteristics: LMx93 and LM193A

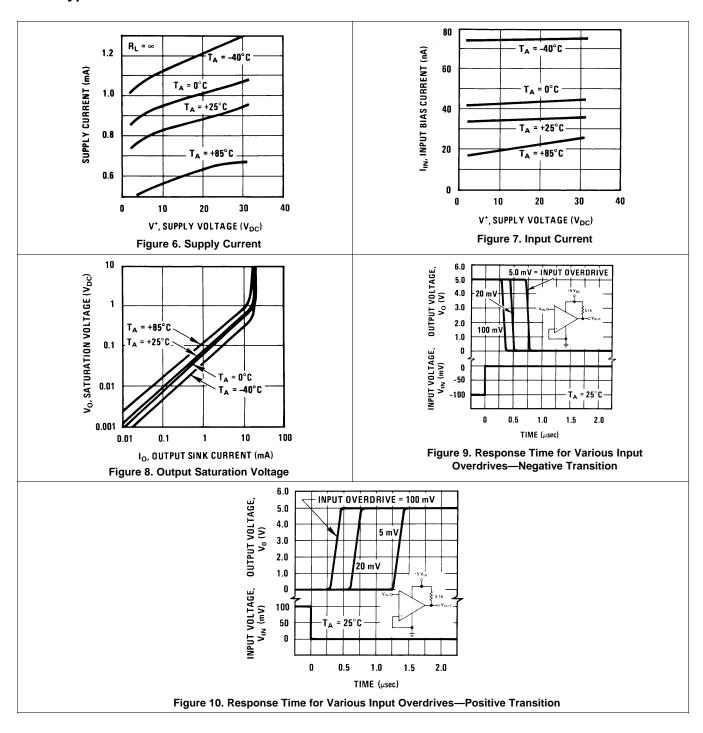

### 6.10 Typical Characteristics: LM2903

## 7 Detailed Description

#### 7.1 Overview

The LM139 provides two independently functioning, high-precision, low  $V_{OS}$  drift, low input bias current comparators in a single package. The low power consumption of 0.4 mA at 5 V and the 2.0 V supply operation makes the LM139 suitable for battery powered applications.

#### 7.2 Functional Block Diagram

Figure 11. Basic Comparator

### 7.3 Feature Description

The input bias current of 25 nA enables the LM193 to use even very high impedance nodes as inputs. The differential voltage input range equals the supply voltage range.

The LM193 can be operated with a single supply, where V+ can be from 2.0 V to 36 V, or in a dual supply voltage configuration, where GND pin is used as a V- supply. The supply current draws only 0.4 mA for both comparators.

The output of each comparator in the LM193 is the open collector of a grounded-emitter NPN output transistor which can typically draw up to 16 mA.

#### 7.4 Device Functional Modes

A basic comparator circuit is used for converting analog signals to a digital output. The output is HIGH when the voltage on the non-inverting (+IN) input is greater than the inverting (-IN) input. The output is LOW when the voltage on the non-inverting (+IN) input is less than the inverting (-IN) input. The inverting input (-IN) is also commonly referred to as the "reference" or "VREF" input. All pins of any unused comparators should be tied to the negative supply.

0 Submit Documentation Feedback

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LM193 series are high gain, wide bandwidth devices which, like most comparators, can easily oscillate if the output lead is inadvertently allowed to capacitively couple to the inputs via stray capacitance. This shows up only during the output voltage transition intervals as the comparator change states. Power supply bypassing is not required to solve this problem. Standard PC board layout is helpful as it reduces stray input-output coupling. Reducing the input resistors to < 10 k $\Omega$  reduces the feedback signal levels and finally, adding even a small amount (1.0 to 10 mV) of positive feedback (hysteresis) causes such a rapid transition that oscillations due to stray feedback are not possible. Simply socketing the IC and attaching resistors to the pins will cause input-output oscillations during the small transition intervals unless hysteresis is used. If the input signal is a pulse waveform, with relatively fast rise and fall times, hysteresis is not required.

All input pins of any unused comparators should be tied to the negative supply.

The bias network of the LM193 series establishes a drain current which is independent of the magnitude of the power supply voltage over the range of from 2.0  $V_{DC}$  to 30  $V_{DC}$ .

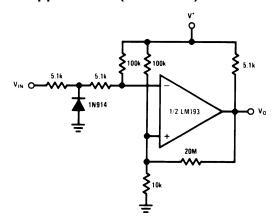

The differential input voltage may be larger than  $V^+$  without damaging the device *Typical Applications*. Protection should be provided to prevent the input voltages from going negative more than  $-0.3~V_{DC}$  (at 25°C). An input clamp diode can be used as shown in *Typical Applications*.

The output of the LM193 series is the uncommitted collector of a grounded-emitter NPN output transistor. Many collectors can be tied together to provide an output OR'ing function. An output pullup resistor can be connected to any available power supply voltage within the permitted supply voltage range and there is no restriction on this voltage due to the magnitude of the voltage which is applied to the V<sup>+</sup> terminal of the LM193 package. The output can also be used as a simple SPST switch to ground (when a pullup resistor is not used). The amount of current which the output device can sink is limited by the drive available (which is independent of V<sup>+</sup>) and the  $\beta$  of this device. When the maximum current limit is reached (approximately 16 mA), the output transistor will come out of saturation and the output voltage will rise very rapidly. The output saturation voltage is limited by the approximately 60  $\Omega$  r<sub>SAT</sub> of the output transistor. The low offset voltage of the output transistor (1.0 mV) allows the output to clamp essentially to ground level for small load currents.

#### 8.2 Typical Applications

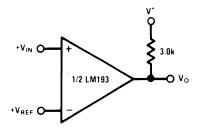

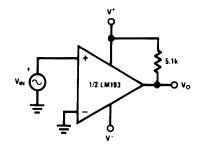

#### 8.2.1 Basic Comparator

Figure 12. Basic Comparator

#### 8.2.1.1 Design Requirements

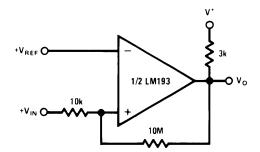

The basic usage of a comparator is to indicate when a specific analog signal has exceeded some predefined threshold. In this application, the negative input (IN–) is tied to a reference voltage, and the positive input (IN+) is connected to the input signal. The output is pulled up with a resistor to the logic supply voltage, V+ with a pullup resistor.

For an example application, the supply voltage is 5V. The input signal varies between 1 V and 3 V, and we want to know when the input exceeds  $2.5 \text{ V} \pm 1\%$ . The supply current draw should not exceed 1 mA.

#### 8.2.1.2 Detailed Design Procedure

First, we determine the biasing for the 2.5-V reference. With the 5-V supply voltage, we would use a voltage divider consisting of one resistor from the supply to IN- and an second resistor from IN-. The 25 nA of input current bias should be < 1% of the bias current for Vref. With a 100-k $\Omega$  resistor from IN- to V+ and an additional 100-K $\Omega$  resistor from IN- to ground, there would be 25  $\mu$ A of current through the two resistors. The 3-k $\Omega$  pullup shown will need 5 V/3 k $\Omega$   $\rightarrow$  1.67 mA, which exceeds our current budget.

With the 400- $\mu$ A supply current and 25  $\mu$ A of VREF bias current, there is 575  $\mu$ A remaining for output pullup resistor; with 5-V supply, we need a pullup larger than 8.7 k $\Omega$ . A 10-k $\Omega$  pullup is a value that is commonly available and can be used here.

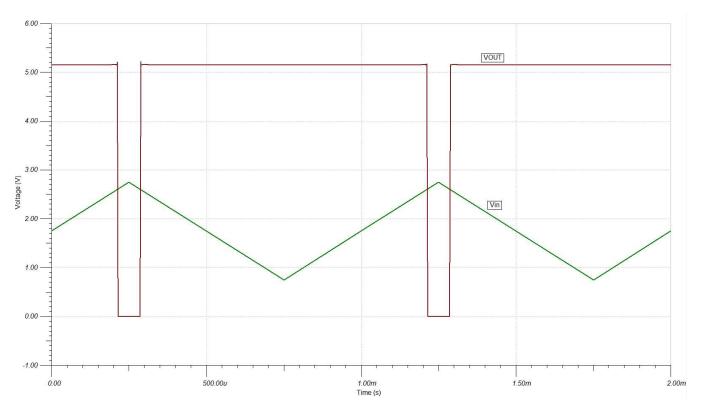

#### 8.2.1.3 Application Curve

Figure 13. Basic Comparator Response

2 Submit Documentation Feedback

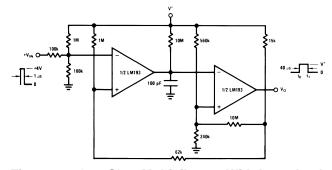

## 8.2.2 System Examples

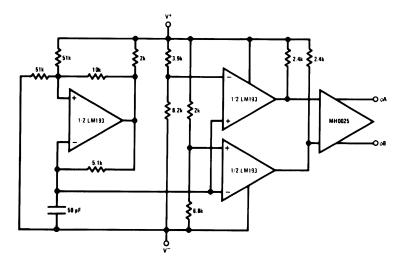

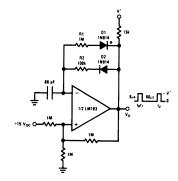

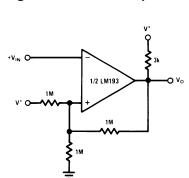

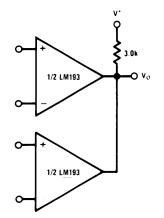

### 8.2.2.1 Split-Supply Application

(V+=-15  $V_{DC}$  and V-=-15  $V_{DC}$ )

Figure 14. MOS Clock Driver

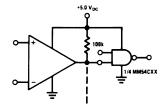

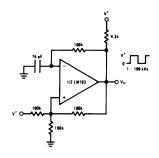

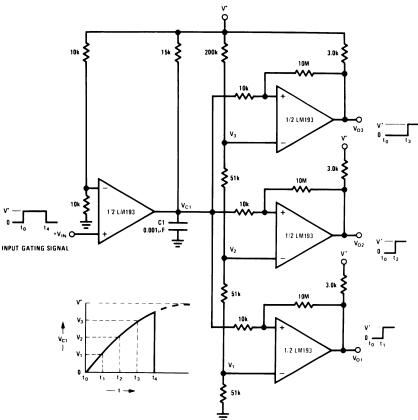

## 8.2.2.2 $V+ = 5.0 V_{DC}$ Application Circuits

Figure 15. Driving CMOS

10k OMSAXX

Figure 16. Driving TTL

\* For large ratios of R1/R2,

D1 can be omitted.

Figure 17. Squarewave Oscillator

Figure 18. Pulse Generator

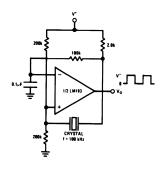

Figure 19. Crystal Controlled Oscillator

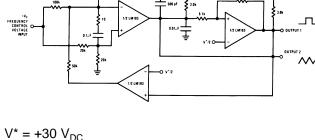

$V^* = +30 \text{ V}_{DC}$ +250 mV<sub>DC</sub>  $\leq$  V<sub>C</sub>  $\leq$  +50 V<sub>DC</sub> 700Hz  $\leq$  f<sub>o</sub>  $\leq$  100kHz

Figure 20. Two-Decade High Frequency VCO

Figure 21. Basic Comparator

Figure 23. Inverting Comparator With Hysteresis

Figure 22. Non-Inverting Comparator With Hysteresis

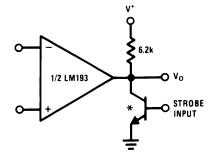

\* OR LOGIC GATE

WITHOUT PULL-UP RESISTOR

Figure 24. Output Strobing

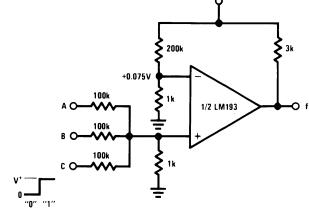

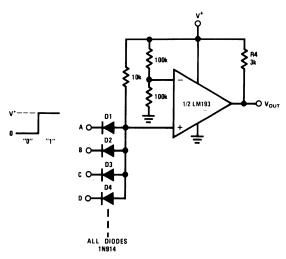

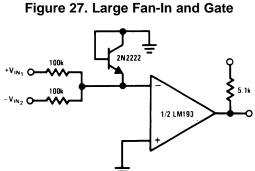

Figure 25. And Gate

Figure 26. Or Gate

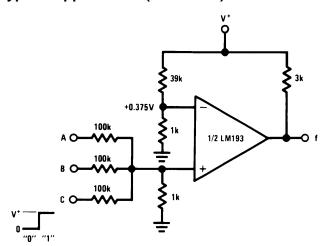

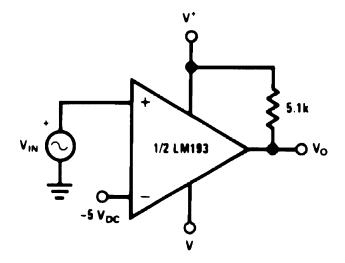

Figure 29. Comparing Input Voltages of Opposite Polarity

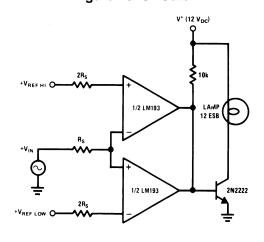

Figure 28. Limit Comparator

Figure 30. Oring the Outputs

Figure 31. Zero Crossing Detector (Single Power Supply)

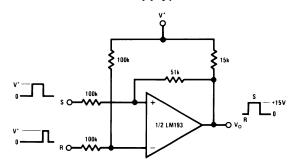

Figure 33. Bi-Stable Multivibrator

Figure 35. Zero Crossing Detector

Figure 32. One-Shot Multivibrator

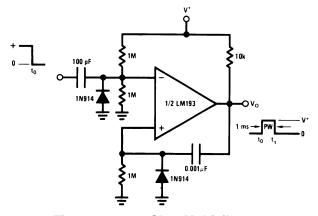

Figure 34. One-Shot Multivibrator With Input Lock Out

Figure 36. Comparator With a Negative Reference

Figure 37. Time Delay Generator

## 9 Power Supply Recommendations

Even in low frequency applications, the LM139-N can have internal transients which are extremely quick. For this reason, bypassing the power supply with 1.0  $\mu$ F to ground will provide improved performance; the supply bypass capacitor should be placed as close as possible to the supply pin and have a solid connection to ground. The bypass capacitor should have a low ESR and also a SRF greater than 50MHz.

#### 10 Layout

#### 10.1 Layout Guidelines

Try to minimize parasitic impedances on the inputs to avoid oscillation. Any positive feedback used as hysteresis should place the feedback components as close as possible to the input pins. Care should be taken to ensure that the output pins do not couple to the inputs. This can occur through capacitive coupling if the traces are too close and lead to oscillations on the output. The optimum placement for the bypass capacitor is closest to the V+ and ground pins. Take care to minimize the loop area formed by the bypass capacitor connection between V+ and ground. The ground pin should be connected to the PCB ground plane at the pin of the device. The feedback components should be placed as close to the device as possible minimizing strays.

#### 10.2 Layout Example

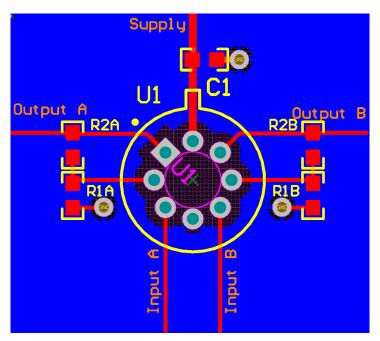

Figure 38. Layout Example

Submit Documentation Feedback

## 11 Device and Documentation Support

#### 11.1 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to order now.

Table 1. Related Links

| PARTS    | PRODUCT FOLDER | ORDER NOW  | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|----------|----------------|------------|---------------------|---------------------|---------------------|

| LM193-N  | Click here     | Click here | Click here          | Click here          | Click here          |

| LM2903-N | Click here     | Click here | Click here          | Click here          | Click here          |

| LM293-N  | Click here     | Click here | Click here          | Click here          | Click here          |

| LM393-N  | Click here     | Click here | Click here          | Click here          | Click here          |

#### 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.3 Trademarks

All trademarks are the property of their respective owners.

#### 11.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 1999–2018, Texas Instruments Incorporated

14-Jan-2019

### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | _    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking          | Samples |

|------------------|--------|--------------|--------------------|------|------|----------------------------|------------------|--------------------|--------------|-------------------------|---------|

|                  | (1)    |              |                    | _    | Qty  | (2)                        | (6)              | (3)                |              | (4/5)                   |         |

| LM193AH          | ACTIVE | TO-99        | LMC                | 8    | 500  | TBD                        | Call TI          | Call TI            | -55 to 125   | ( LM193AH, LM193AH<br>) | Samples |

| LM193AH/NOPB     | ACTIVE | TO-99        | LMC                | 8    | 500  | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-1-NA-UNLIM   | -55 to 125   | ( LM193AH, LM193AH<br>) | Samples |

| LM193H           | ACTIVE | TO-99        | LMC                | 8    | 500  | TBD                        | Call TI          | Call TI            | -55 to 125   | ( LM193H, LM193H)       | Samples |

| LM193H/NOPB      | ACTIVE | TO-99        | LMC                | 8    | 500  | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-1-NA-UNLIM   | -55 to 125   | ( LM193H, LM193H)       | Samples |

| LM2903ITL/NOPB   | ACTIVE | DSBGA        | YZR                | 8    | 250  | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | C<br>03                 | Samples |

| LM2903ITLX/NOPB  | ACTIVE | DSBGA        | YZR                | 8    | 3000 | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | C<br>03                 | Samples |

| LM2903M          | ACTIVE | SOIC         | D                  | 8    | 95   | TBD                        | Call TI          | Call TI            | -40 to 85    | LM<br>2903M             | Samples |

| LM2903M/NOPB     | ACTIVE | SOIC         | D                  | 8    | 95   | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LM<br>2903M             | Samples |

| LM2903MX/NOPB    | ACTIVE | SOIC         | D                  | 8    | 2500 | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LM<br>2903M             | Samples |

| LM2903N/NOPB     | ACTIVE | PDIP         | Р                  | 8    | 40   | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-NA-UNLIM   | -40 to 85    | LM<br>2903N             | Samples |

| LM293H           | ACTIVE | TO-99        | LMC                | 8    | 500  | TBD                        | Call TI          | Call TI            | -25 to 85    | ( LM293H, LM293H)       | Samples |

| LM293H/NOPB      | ACTIVE | TO-99        | LMC                | 8    | 500  | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-1-NA-UNLIM   | -25 to 85    | ( LM293H, LM293H)       | Samples |

| LM393M           | NRND   | SOIC         | D                  | 8    | 95   | TBD                        | Call TI          | Call TI            | 0 to 70      | LM<br>393M              |         |

| LM393M/NOPB      | ACTIVE | SOIC         | D                  | 8    | 95   | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | 0 to 70      | LM<br>393M              | Samples |

| LM393MX          | NRND   | SOIC         | D                  | 8    | 2500 | TBD                        | Call TI          | Call TI            | 0 to 70      | LM<br>393M              |         |

| LM393MX/NOPB     | ACTIVE | SOIC         | D                  | 8    | 2500 | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | 0 to 70      | LM<br>393M              | Samples |

| LM393N/NOPB      | ACTIVE | PDIP         | Р                  | 8    | 40   | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-NA-UNLIM   | 0 to 70      | LM<br>393N              | Samples |

# **PACKAGE OPTION ADDENDUM**

14-Jan-2019

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|----------------------|---------|

| LM393TL/NOPB     | ACTIVE | DSBGA        | YZR                | 8    | 250            | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | 0 to 70      | C<br>02              | Samples |

| LM393TLX/NOPB    | ACTIVE | DSBGA        | YZR                | 8    | 3000           | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | 0 to 70      | C<br>02              | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LM2903-N, LM293-N:

# **PACKAGE OPTION ADDENDUM**

14-Jan-2019

• Automotive: LM2903-Q1

www.ti.com

● Enhanced Product: LM293-EP

#### NOTE: Qualified Version Definitions:

- Automotive Q100 devices qualified for high-reliability automotive applications targeting zero defects

- Enhanced Product Supports Defense, Aerospace and Medical Applications

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 17-Nov-2018

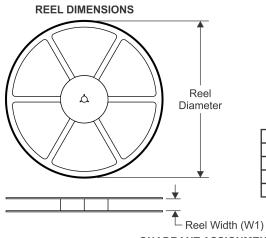

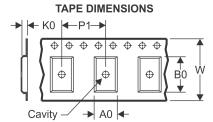

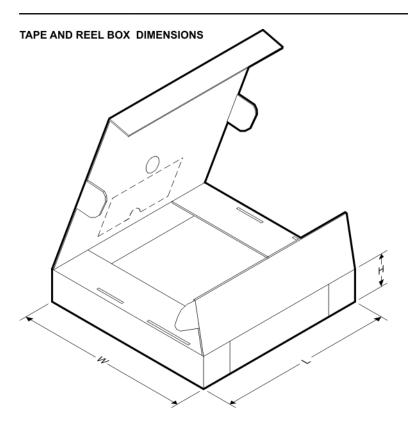

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

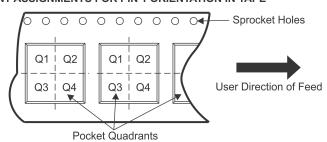

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM2903ITL/NOPB  | DSBGA           | YZR                | 8 | 250  | 178.0                    | 8.4                      | 1.7        | 1.7        | 0.76       | 4.0        | 8.0       | Q1               |

| LM2903ITLX/NOPB | DSBGA           | YZR                | 8 | 3000 | 178.0                    | 8.4                      | 1.7        | 1.7        | 0.76       | 4.0        | 8.0       | Q1               |

| LM2903MX/NOPB   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM393MX         | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM393MX/NOPB    | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM393TL/NOPB    | DSBGA           | YZR                | 8 | 250  | 178.0                    | 8.4                      | 1.7        | 1.7        | 0.76       | 4.0        | 8.0       | Q1               |

| LM393TLX/NOPB   | DSBGA           | YZR                | 8 | 3000 | 178.0                    | 8.4                      | 1.7        | 1.7        | 0.76       | 4.0        | 8.0       | Q1               |

www.ti.com 17-Nov-2018

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM2903ITL/NOPB  | DSBGA        | YZR             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| LM2903ITLX/NOPB | DSBGA        | YZR             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| LM2903MX/NOPB   | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LM393MX         | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LM393MX/NOPB    | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LM393TL/NOPB    | DSBGA        | YZR             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| LM393TLX/NOPB   | DSBGA        | YZR             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

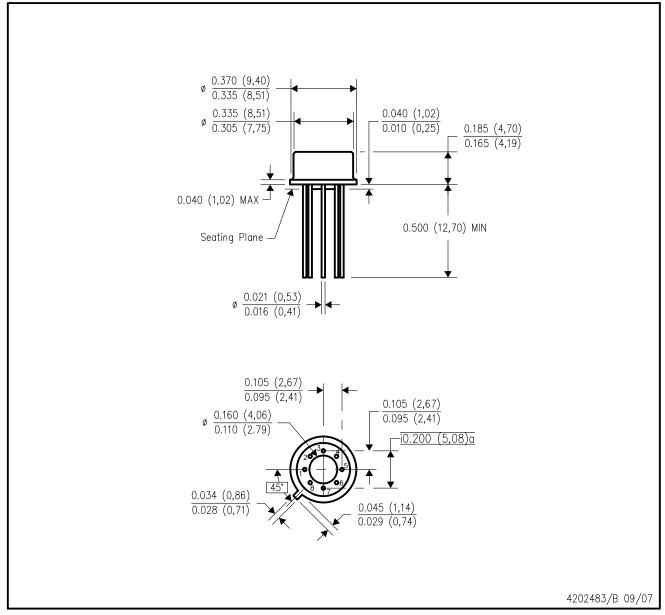

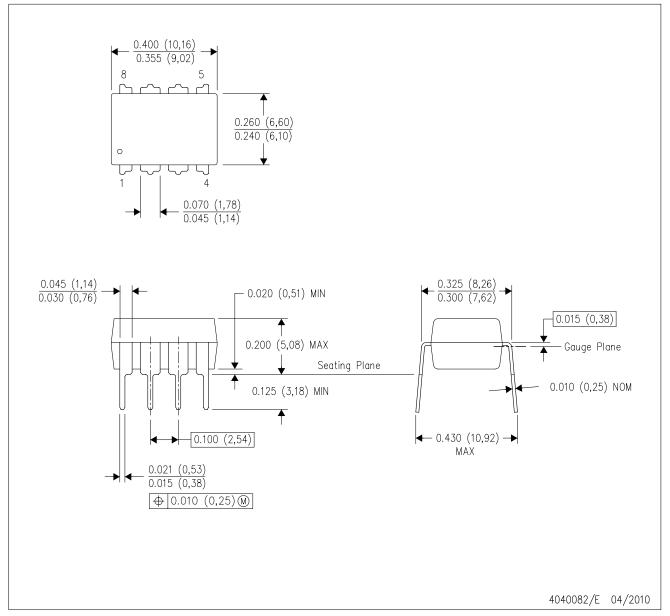

# LMC (O-MBCY-W8)

# METAL CYLINDRICAL PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Leads in true position within 0.010 (0,25) R @ MMC at seating plane.

- D. Pin numbers shown for reference only. Numbers may not be marked on package.

- E. Falls within JEDEC MO-002/TO-99.

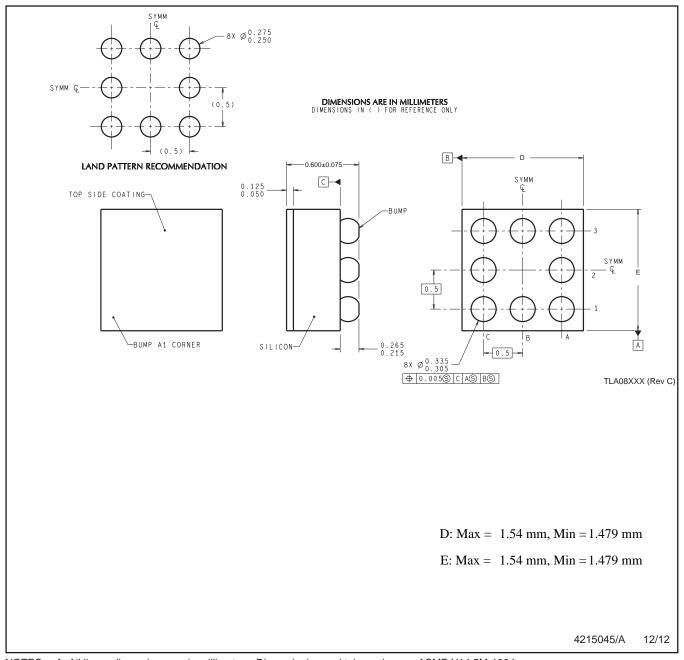

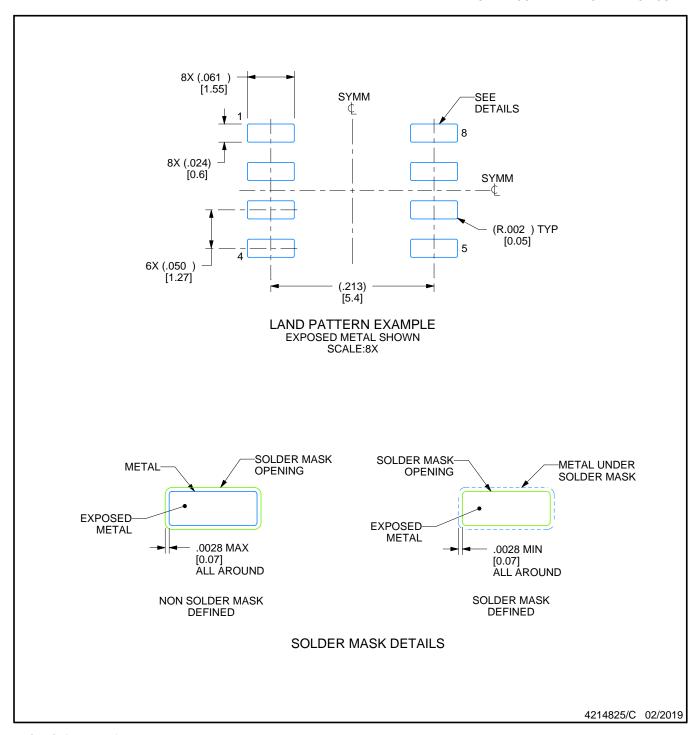

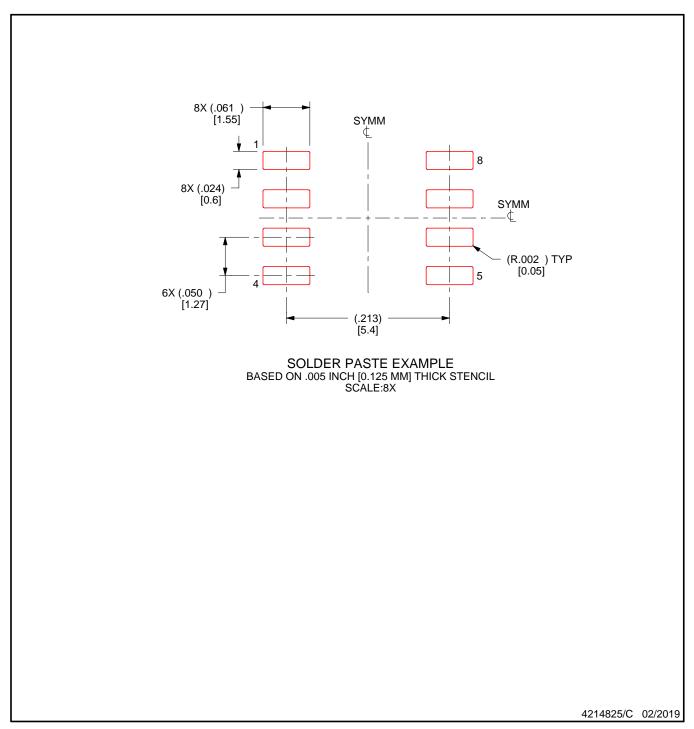

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994. B. This drawing is subject to change without notice.

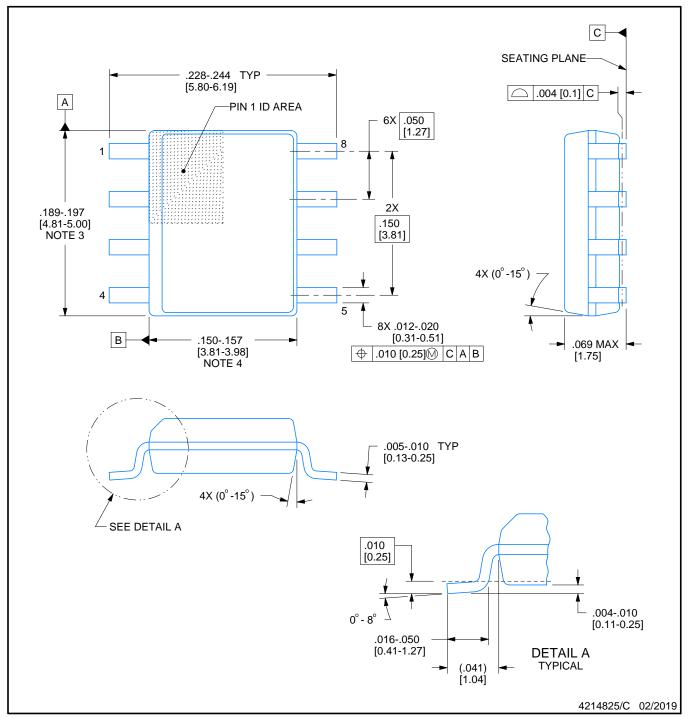

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# P (R-PDIP-T8)

# PLASTIC DUAL-IN-LINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated