# Monolithic and Wafer Level Packaged Three-Axis Accelerometer

# MXC400xXC

# **FEATURES**

- Ultra Low Cost

- Most Advantaged Technology in Industry

- Monolithically-Integrated Single Chip MEMS Sensor with On-Chip Signal Processing

- MEMSIC Proprietary Technology with No Moving Parts

- >200,000g Shock Survival Rating of Sensing Structure

- 12-bit Signal Output for X, Y and Z Axes

- Full Scale Range ±2g, ±4g and ±8g

- 8-bit Temperature Output (-50°C to +100°C)

- Smallest Wafer Level Package (WLP) Footprint 1.18mm×1.70mm×0.85mm

- 6-Position Orientation Detection

- Shake Detection with Interrupt

- Programmable Shake Detection Threshold

- I<sup>2</sup>C Slave, FAST (≤400 KHz) Mode Interface

- 1.8~3.6V Single Supply Continuous Operation

- 1.8V Compatible I/O

- Embedded Power Up/Down Mode

- Eight I<sup>2</sup>C Addresses Pre-settable by User

- RoHS Compliant

# **APPLICATIONS**

- Information Appliances Cell Phones, Tablets, PDA's, Computer Peripherals

- Consumer LCD Projectors, Pedometers, DSC/DVC, MP3/MP4

- Gaming Joystick, Toys

- Household Safety Heating Fan, Iron, Cooling Fan

# **DESCRIPTION**

The MEMSIC Three-Axis Thermal Accelerometer is based on MEMSIC's Proprietary thermal technology that is built with 0.18µm standard CMOS process and the most advanced Wafer Level Packaging. This device contains no moving sensor parts and thus eliminates field reliability and repeatability issues associated with competitive products. For example,

Information furnished by MEMSIC is believed to be accurate and reliable. However, no responsibility is assumed by MEMSIC for its use, nor for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of MEMSIC.

there is no measurable resonance (immunity to vibration), no stiction, and no detectable hysteresis. It also eliminates the "click" sounds typically heard in ball based orientation sensors. Shock survival of the MEMS sensing structure is greater than 200,000g. This sensor provides X/Y/Z axis acceleration signals with very low 0g offset, and temperature signal with high accuracy. In addition, it detects six orientation positions, X/Y shake and shake directions.

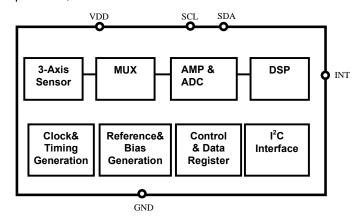

Figure 1: MXC400xXC Functional block diagram

The MXC400xXC is the World's only monolithic and WLP three-axis accelerometer with smallest profile of 1.18mm×1.70mm×0.85mm that is perfectly suitable for mobile applications. It is available in operating temperature range of -40°C to +85°C.

The MXC400xXC provides I<sup>2</sup>C digital output with 400 KHz fast mode operation. And an interrupt pin (INT) is provided for orientation and X/Y shake detections. The device also has a power-down mode enabled through the I<sup>2</sup>C interface.

©MEMSIC, Inc.

One Technology Drive, Suite 325, Andover, MA01810, USA

Tel: +1 978 738 0900 Fax: +1 978 738 0196

www MFMSIC com

$\textbf{SPECIFICATIONS} \text{ (Measurements @ 25°C, $\pm 2g$ full scale range, acceleration = 0 g unless otherwise noted; VDD=1.8V unless oth$ otherwise specified)

**Table 1: Parameter specification**

| PARAMETER                            | Conditions             | MIN  | TYP   | MAX   | UNITS  |

|--------------------------------------|------------------------|------|-------|-------|--------|

|                                      | FSR[1:0] set to 0      | -2   |       | +2    |        |

| Full Scale Ranges (FSR) <sup>1</sup> | FSR[1:0] set to 1      | -4   |       | +4    | g      |

|                                      | FSR[1:0] set to 2      | -8   |       | +8    | ]      |

| Nonlinearity                         | Best fit straight line |      | ±0.5  |       | % FSR  |

| Alignment Error <sup>2</sup>         |                        |      |       | ±0.01 | degree |

| Cross Axis Sensitivity 3             |                        |      | ±2.0  |       | %      |

|                                      | ±2g FSR                |      | 1024  |       |        |

| Sensitivity                          | ±4g FSR                |      | 512   |       | LSB/g  |

|                                      | ±8g FSR                |      | 256   |       |        |

| Sensitivity Accuracy                 |                        |      | ±2    |       | %      |

| Sensitivity TC <sup>4</sup>          | ∆ from 25°C            |      | ±0.1  |       | %/°C   |

| Zero g Offset Bias Level 4           |                        |      | ±80   |       | mg     |

| Zero g Offset TC <sup>4</sup>        | ∆ from 25°C            |      | ±0.8  |       | mg/°C  |

| Frequency Response                   | @ -3dB                 |      | 10    |       | Hz     |

| Output Data Rates (ODR)              |                        |      | 100   |       | Hz     |

| Operating Voltage (VDD)              |                        | 1.62 | 1.8   | 3.6   | V      |

| Operating Voltage Rise Time          |                        |      |       | 8     | mS     |

| I <sup>2</sup> C Bus Voltage (VIO)   |                        | 1.2  |       | VDD   | V      |

| Temperature Sensor Sensitivity       |                        |      | 0.586 |       | °C/LSB |

| Temperature Sensor Offset            |                        |      | 0     |       | LSB    |

| Supply Current                       |                        |      | 1.6   |       | mA     |

| Power Down Current                   |                        |      | 0.8   | 1.0   | μΑ     |

| Operating Temperature Range          |                        | -40  |       | +85   | °C     |

Note:<sup>1</sup>: Guaranteed by measurement of initial offset and sensitivity

<sup>2</sup>: Alignment error is specified as the angle between the true and indicated axis of sensitivity

<sup>3</sup>: Relative contribution between any two of the three axis

<sup>4</sup>: With MEMSIC's software driver (included)

#### **ABSOLUTE MAXIMUM RATINGS\***

$\begin{array}{lll} \text{Supply Voltage (VDD)} & -0.5 \text{ V to } +5.0 \text{V} \\ \text{Storage Temperature} & -40^{\circ}\text{C to } +150^{\circ}\text{C} \\ \text{Acceleration} & 200,000\text{g} \\ \text{ESD} & 2\text{kV (HBM)} \end{array}$

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ORDERING GUIDE**

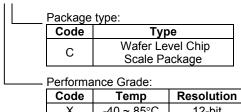

#### MXC400xXC

|   | ^       |    | 40 ~ 65°C                | 12-010 |  |

|---|---------|----|--------------------------|--------|--|

|   | Address | СО | de: 0 ~ 7                |        |  |

| • | Numbe   | r  | 7-bit I <sup>2</sup> C A | ddress |  |

|   | 0       |    | 10H                      |        |  |

|   | 1       |    | 111                      | 1      |  |

|   | 2       |    | 12H                      | 1      |  |

|   | 3       |    | 13F                      | 1      |  |

| _ |     |

|---|-----|

| 1 | 11H |

| 2 | 12H |

| 3 | 13H |

| 4 | 14H |

| 5 | 15H |

| 6 | 16H |

| 7 | 17H |

Figure 2: Ordering guide

#### PIN DESCRIPTION: WLP PACKAGE

Table 2: Pin description

| Pin | Name | Description                                | I/O |

|-----|------|--------------------------------------------|-----|

| 1   | SCL  | Serial Clock Line for I <sup>2</sup> C bus | 1   |

| 2   | NC   | No Connection                              | ı   |

| 3   | GND  | Connected to Ground                        | I   |

| 4   | INT  | Interrupt Output                           | 0   |

| 5   | SDA  | Serial Data Line for I <sup>2</sup> C bus  | I/O |

| 6   | VDD  | 1.62 V to 3.6 V                            | I   |

**Caution:** Electro Static Discharge (ESD) sensitive device.

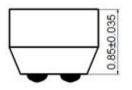

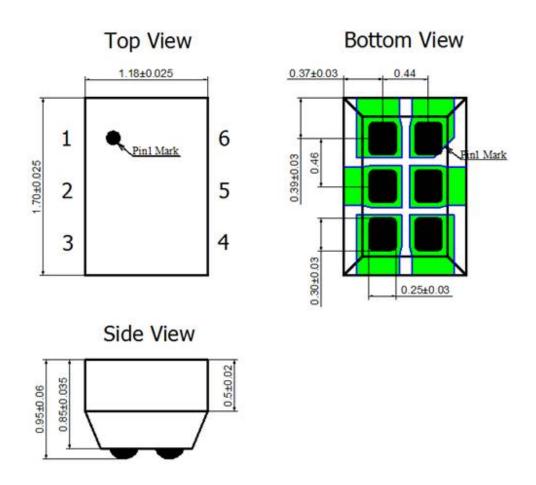

# **PACKAGE ILLUSTRATION**

Side View

Bottom View Figure 3: Package illustration

# THEORY OF OPERATION

This device is a complete three-axis acceleration measurement system fabricated on a monolithic CMOS process. The device operation is based on MEMSIC's proprietary sensor design gas convection.

A heat source, surrounded by thermopiles in the silicon chip, is suspended across a cavity. This heat source creates a field of heated gas around it, commonly referred as hot air bubble. The thermopiles capable of detecting changes in the temperature field around the heater. Applied acceleration disturbs the temperature profile. The temperature, and hence voltage output of thermopiles will then be different. The differential voltage at the thermopile outputs is directly proportional to the acceleration.

<sup>\*</sup> Parts are shipped in tape and reel packaging.

A signal path on the MXC400xXC measures accelerations at three directions and temperature sequentially.

For more details visit the MEMSIC website at www.MEMSIC.com for a picture/graphic description of the free convection heat transfer principle.

# **PIN DESCRIPTIONS**

**VDD** – Supply input for the circuits and the sensor heater in the accelerometer. The DC voltage should be between 1.62 and 3.6 volts.

**GND** – Accelerometer ground pin.

NC - Should be left open.

**INT** – Interrupt output. The logic level on this pin reflects the state of the INT bit in the STATUS register. INT is set when the orientation differs from the last orientation read by the processor or an X/Y shake event is detected. INT needs to be pulled up to VIO. INT output is active low, and is cleared upon register INT\_CLRx was written 1 by the I<sup>2</sup>C master. Refer to the description of user register 0x01 in the "MXC400xXC USER REGISTERS" section.

VIO - I<sup>2</sup>C bus line.

**SDA** – I<sup>2</sup>C serial data line that operates in FAST mode.

$SCL - I^2C$  serial clock line that operates in FAST mode.

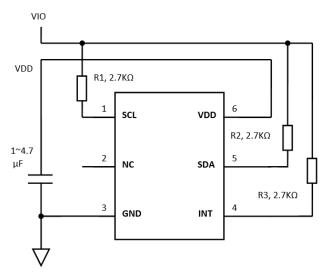

#### HARDWARE DESIGN CONSIDERATION

- R1, R2, and R3 are pull-up resistors. The value can be determined by user according to the requirement of the host device; recommend using 2.7Kohm.

- 2. If INT is not used, it can be kept disconnected.

- 3. It is necessary to keep VDD voltage clean for best noise performance; suggested to keep VDD noise ≤ 1mV RMS. A low-ESR bypass cap is required and recommended value is 1~4.7µF. It should be placed close to the device as much as possible.

Figure 4: Connection diagram

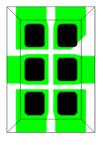

# **LAND PATTERN**

- The device should be put into the center area of the PCB. Edge area is not recommended.

- 2. The device routing should be symmetric.

- 3. Solder mask defined PCB is preferred.

- 4. Recommended land pattern of PCB is shown in Figure 5 and recommended stencil opening size is shown in Figure 6.

- MXC400xXC land pattern is compatible with the 2D version accelerometers MXC6255XC and MXC6225XC.

- 6. Thickness of stencil should be 0.08mm ~ 0.1mm.

- 7. For ultra-small packages such as the MXC400xXC, the bond pads and the amount of solder are relatively small. Therefore, strength of solder joints are not as high as compared with standard conventional SMT devices. For applications that require more robustness to mechanical shock (such as experienced in drop tests >1m), MEMSIC recommends the use of underfill material (e.g., Namics 1589-1, Henkel-UF3810, or equivalent).

Figure 5: Recommended land pattern (unit: mm)

Figure 6: Recommended stencil opening size (unit: mm)

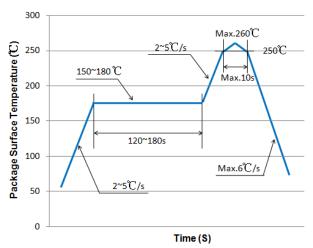

# **SOLDER REFLOW PROFILE**

- 1. Reflow is limited by 2 times. Second reflow should be applied after device has cooled down to room temperature (25°C).

- Recommended reflow profile for Pb free process is shown in Figure 7. The time duration of peak temperature (260°C) should be limited to 10 seconds.

- **3.** Type 4 solder paste is recommended for a better SMT quality.

Figure 7: Recommended solder reflow profile

# **MANUAL SOLDERING**

- When soldering/repairing MXC400xXC manually via solder iron or heater gun, the temperature on the device should not exceed 260°C and the time should be limited to 10 seconds.

- **2.** Avoid bending or torqueing the PCB after the sensor is assembled.

Formal release date: 2015/04/24

# **DIGITAL INTERFACE**

Table 3: Digital interface, I/V

| SYMBOL         | PARAMETER                   | CONDITIONS                       | MIN     | MAX     | UNITS |

|----------------|-----------------------------|----------------------------------|---------|---------|-------|

| $V_{IL}$       | Logic Input Low Level       |                                  |         | 0.3*VIO | V     |

| $V_{IH}$       | Logic Input High Level      |                                  | 0.7*VIO |         | V     |

| $V_{hys}$      | Hysteresis of Schmitt input |                                  | 0.1     |         | V     |

| $V_{OL}$       | Logic Output Low Level      |                                  |         | 0.2*VIO | V     |

| $V_{OH}$       | Logic Output High Level     |                                  | 0.8*VIO |         | V     |

| l <sub>i</sub> | Input Leakage Current       | $0.1V_{DD} < V_{in} < 0.9V_{DD}$ | -10     | 10      | μΑ    |

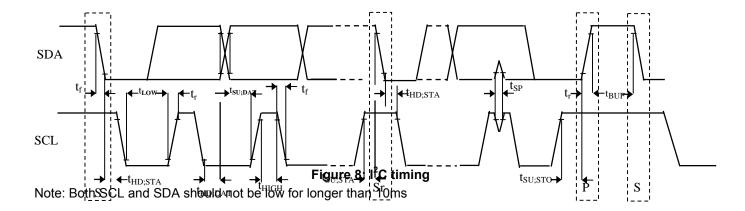

Table 4: Digital interface, timing

| SYMBOL              | PARAMETER                            | CONDITIONS                             | MIN | TYP | MAX | UNITS |

|---------------------|--------------------------------------|----------------------------------------|-----|-----|-----|-------|

| f <sub>SCL</sub>    | SCL Clock Frequency                  |                                        | 0   |     | 400 | kHz   |

| t <sub>HD;STA</sub> | START Hold Time                      |                                        | 0.6 |     |     | μS    |

| t <sub>SU;STA</sub> | START Setup Time                     |                                        | 0.6 |     |     | μS    |

| $t_{LOW}$           | LOW period of SCL                    |                                        | 1.3 |     |     | μS    |

| t <sub>HIGH</sub>   | HIGH period of SCL                   |                                        | 0.6 |     |     | μS    |

| t <sub>HD;DAT</sub> | Data Hold Time                       |                                        | 0   |     | 0.9 | μS    |

| t <sub>SU;DAT</sub> | Data Setup Time                      |                                        | 0.1 |     |     | μS    |

| t <sub>r</sub>      | Rise Time                            | From V <sub>IL</sub> toV <sub>IH</sub> |     |     | 0.3 | μS    |

| $t_f$               | Fall Time                            | From V <sub>IH</sub> toV <sub>IL</sub> |     |     | 0.3 | μS    |

| t <sub>BUF</sub>    | Bus Free Time Between STOP and START |                                        | 1.3 |     |     | μS    |

| t <sub>SU;STO</sub> | STOP Setup Time                      |                                        | 0.6 |     |     | μS    |

# I<sup>2</sup>C INTERFACE DESCRIPTION

A slave mode I<sup>2</sup>C interface, capable of operating in standard or fast mode, is implemented on the MXC400xXC. The interface uses a serial data line (SDA) and a serial clock line (SCL) to achieve bi-directional communication between master and slave devices. A master (typically a microprocessor) initiates all data transfers to and from the device, and generates the SCL clock that synchronizes the data transfer. The SDA pin on the MXC400xXC operates both as an input and an open drain output. Since the MXC400xXC only operates as a slave device, the SCL pin is always an input. There are external pull-up resistors on the I<sup>2</sup>C bus lines. Devices that drive the I<sup>2</sup>C bus lines do so through open-drain n-channel driver transistors, creating a wired NOR type arrangement.

Data on SDA is only allowed to change when SCL is low. A high to low transition on SDA when SCL is high is indicative of a START condition, whereas a low to high transition on SDA when SCL is high is indicative of a STOP condition. When the interface is not busy, both SCL and SDA are high. A data transmission is initiated by the master pulling SDA low while SCL is high, generating a START condition. The data transmission occurs serially in 8 bit bytes, with the MSB transmitted first. During each byte of transmitted data, the master will generate 9 clock pulses. The first 8 clock pulses are used to clock the data, the 9<sup>th</sup> clock pulse is for the acknowledge bit. After the 8 bits of data are clocked in, the transmitting device releases SDA, and the receiving device pulls it down so that it is stable low during the entire 9<sup>th</sup> clock pulse. By doing this, the receiving device "acknowledges" that it has received the transmitted byte. If the slave receiver does not generate an acknowledge, then the master device can generate a STOP condition and abort the transfer. If the master is the receiver in a data transfer, then it must signal the end of data to the slave by not generating an acknowledge on the last byte that was clocked out of the slave. The slave must release SDA to allow the master to generate a STOP or repeated START condition.

The master initiates a data transfer by generating a START condition. After a data transmission is complete, the master may terminate the data transfer by generating a STOP condition. The bus is considered to be free again a certain time after the STOP condition. Alternatively, the master can keep the bus busy by generating a repeated

START condition instead of a STOP condition. This repeated START condition is functionally identical to a START condition that follows a STOP. Each device that sits on the I<sup>2</sup>C bus has a unique 7-bit address.

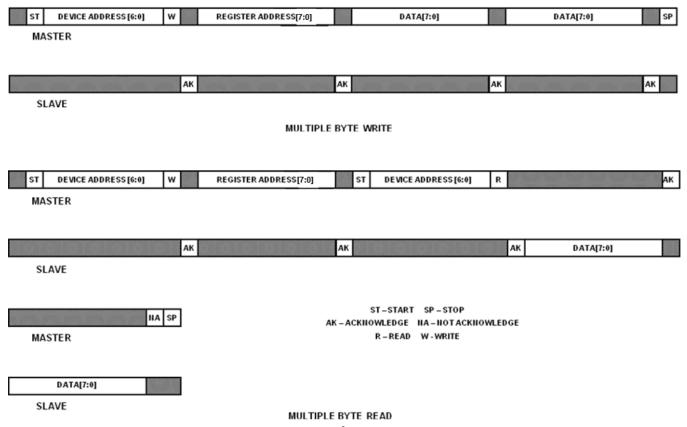

The first byte transmitted by the master following a START is used to address the slave device. The first 7 bits contain the address of the slave device, and the 8th bit is the R/W\* bit (read = 1, write = 0; the asterisk indicates active low, and is used instead of a bar). If the transmitted address matches up to that of the MXC400xXC, then the MXC400xXC will acknowledge receipt of the address, and prepare to receive or send data.

If the master is writing to the MXC400xXC, then the next byte that the MXC400xXC receives, following the address byte, is loaded into the address counter internal to the MXC400xXC. The contents of the address counter indicate which register on the MXC400xXC is being accessed. If the master now wants to write data to the MXC400xXC, it just continues to send 8-bit bytes. Each byte of data is latched into the register on the MXC400xXC that the address counter points to. The address counter is incremented after the transmission of each byte.

If the master wants to read data from the MXC400xXC, it first needs to write the address of the register it wants to begin reading data from to the MXC400xXC address counter. It does this by generating a START, followed by the address byte containing the MXC400xXC address, with  $R/W^* = 0$ . The next transmitted byte is then loaded into the MXC400xXC address counter. Then, the master repeats the START condition and re-transmits the MXC400xXC address, but this time with the  $R/W^*$  bit set to 1. During the next transmission period, a byte of data from the MXC400xXC register that is addressed by the contents of the address counter will be transmitted from the MXC400xXC to the master. As in the case of the master writing to the MXC400xXC, the contents of the address counter will be incremented after the transmission of each byte. The protocol for multiple byte reads and writes between a master and a slave device is depicted as follows.

Figure 9: I<sup>2</sup>C protocol

MXC400xXC  $I^2C$  interface allows  $I^2C$  interface voltage VIO to be lower than the supply voltage VDD. VIO can be as low as 1.2 Volts. In order to achieve reliable operation avoid the situation when both SCL and SDA pins are low for longer than 10ms. Please contact MEMSIC if you plan on using  $I^2C$  interface voltage VIO greater than VDD. MXC400xXC USER REGISTERS

MXC400xXC has 16 8-bit USER registers with addresses of  $0x00 \sim 0x0F$ .

0x00: INT SRC0 - Shake & change in orientation interrupt sources (read only)

Table 5: Shake & change in orientation interrupt sources, register 0x00 (read only)

| Table 5. Chake & change in orientation interrupt sources, register 6x00 (read only) |        |    |    |      |      |      |      |  |

|-------------------------------------------------------------------------------------|--------|----|----|------|------|------|------|--|

| D7                                                                                  | D6     | D5 | D4 | D3   | D2   | D1   | D0   |  |

| CHORZ                                                                               | CHORXY | 0  | 0  | SHYM | SHYP | SHXM | SHXP |  |

0x00: INT\_CLR0 - Shake & change in orientation interrupt clear (write only)

Table 6: Shake & change in orientation interrupt clear, register 0x00 (write only)

| rable of onlare & change in orientation interrupt clear, register oxoo (write only) |       |    |    |       |       |       |       |  |

|-------------------------------------------------------------------------------------|-------|----|----|-------|-------|-------|-------|--|

| D7                                                                                  | D6    | D5 | D4 | D3    | D2    | D1    | D0    |  |

| ORZC                                                                                | ORXYC | -  | -  | SHYMC | SHYPC | SHXMC | SHXPC |  |

0x01: INT SRC1 - Data ready interrupt sources, tilt & orientation status (read only)

Table 7: Data ready interrupt sources, tilt & orientation, register 0x01 (read only)

|      |     |         |         | -, | <u> </u> |    | <u> </u> |

|------|-----|---------|---------|----|----------|----|----------|

| D7   | D6  | D5      | D4      | D3 | D2       | D1 | D0       |

| TILT | ORZ | ORXY[1] | ORXY[0] | 0  | 0        | 0  | DRDY     |

0x01: INT\_CLR1 - Data ready, tilt & data ready interrupt clear (write only)

Table 8: Data ready, tilt & data ready interrupt clear, register 0x01 (write only)

| _ |    |    |    |        | ,  | ,  | (  | <b>j</b> j |

|---|----|----|----|--------|----|----|----|------------|

|   | D7 | D6 | D5 | D4     | D3 | D2 | D1 | D0         |

| Ī | -  | -  | -  | SW_RST | -  | -  | -  | DRDYC      |

The INT\_SRCx and INT\_CLRx are read-only and write-only registers, respectively, sharing the same respective I<sup>2</sup>C addresses (0x00, 0x01). The INT\_SRCx registers contain information indicating the source of interrupts produced on the INT output pin. When an event occurs which generates an interrupt output, the corresponding bit in the INT\_SRCx register is set to 1. The I<sup>2</sup>C master can poll the INT\_SRCx registers to determine the cause of the interrupt, then read the appropriate registers to determine status, read data, and perform any necessary actions to service the interrupt. When interrupt servicing for that interrupt source is completed, the master writes a 1 into the corresponding bit location of the INT\_CLRx register. MXC400xXC then clears that bit of the INT\_SRCx register, then automatically clears the same bit in the INT\_CLRx register. MXC400xXC does not clear any INT\_SRCx register bits whose corresponding bit in the INT\_CLRx register is set to 0.

The SHXP, SHXM, SHYP, or SHYM, bit in the INT\_SRC0 register is set to 1 whenever a shake event is detected in the +X, -X, +Y, or -Y direction, respectively. If a shake event is detected in any axis and the appropriate bit in the INT\_SRC0 register is set, any further detection of shake events in that axis is disabled until the shake bit for that axis is cleared by writing 1 to the corresponding bit in the INT\_CLR0 register. Refer to the description of the DETECTION register for more information on shake detection.

The CHORXY bit in the INT\_SRC0 register is set to 1 whenever a change in the X/Y plane orientation is detected. The CHORZ bit in the INT\_SRC0 register is set to 1 whenever a change in the Z axis orientation is detected. Refer to the description of the DETECTION register for more information on orientation detection.

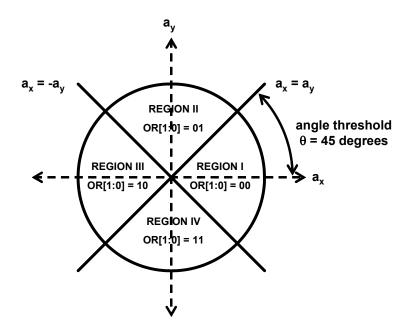

The ORXY[1:0] and ORZ[1:0] bits in INT\_SRC1 indicate the orientation of MXC400xXC. ORXY indicates orientation of the XY plane, and ORZ indicates direction of the Z axis. Mapping of the orientation bits is as follows:

Table 9: X and Y Orientation

| ORXY[1] | ORXY[0] | Orientation |

|---------|---------|-------------|

| 0       | 0       | +X (X=+1g)  |

| 0       | 1       | +Y (Y=+1g)  |

| 1       | 0       | -X (X=-1g)  |

| 1       | 1       | −Y (Y=−1g)  |

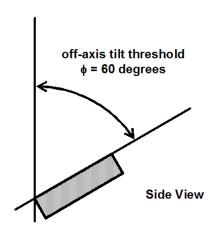

Orientation bits are determined by monitoring the magnitudes and signs of the X, Y, and Z acceleration outputs. The ORXY[1:0] bits are indicative of current orientation only if the off-axis tilt angle (angle between the XY plane and earth gravity vector) is small enough that there is sufficient acceleration amplitude on the X or Y axis to determine a valid XY orientation. For ORXY[1:0] to be updated, the larger of the X and Y axis acceleration magnitudes ( $a_x$ ,  $a_y$ )

must be greater than 0.375g. If this is not the case, the ORXY[1:0] bits retain their last values determined when there was sufficient acceleration amplitude to make a valid orientation decision.

Figure 10: Orientation map

**Table 10: Z Orientation**

| TILT/ORZ[1] | ORZ[0] | Orientation                   |

|-------------|--------|-------------------------------|

| 0           | 0      | positive Z, tilt not detected |

| 0           | 1      | negative Z, tilt not detected |

| 1           | 0      | positive Z, tilt detected     |

| 1           | 1      | negative Z, tilt detected     |

The ORZ[1:0] bits indicate the Z axis orientation as shown in the table above. The vertical/horizontal Z axis orientation is determined by the same criteria used to determine the XY-plane off-axis tilt angle. When the XY plane has a sufficiently small off-axis tilt angle, XY orientation detection is valid (and continues to be updated), and the Z axis is detected as horizontal. ORZ[1] is also the bit for this TILT condition. When off-axis tilt angle exceeds the threshold discussed above, the Z axis is detected as either vertical up or vertical down, depending on the sign of the Z axis acceleration output.

To prevent flickering of the ORXY[1:0] and ORZ[1:0] bits near the orientation region boundaries, a valid measurement of the new orientation must be measured a consecutive number of times determined by the setting of the ORC[1:0] (orientation count) bits in the DETECTION register. This provides a low-pass filtering and hysteresis effect which prevents the orientation bits from rapidly changing.

The DRDY (data ready) bit in the INT\_SRC1 register is set to 1 whenever a new measurement has been made, and new outputs are ready in the XOUT, YOUT, ZOUT and TOUT registers.

The TILT/ORZ[1] bit indicates the part is tilted too much in the X/Y plane, and the X/Y signal is too small to reliably determine orientation. In this case ORXY[1:0] updates are disabled, the orientation remains at its last value.

Figure 11: Off-axis tilt

Writing a 1 to the SW\_RST bit will reset the part as if it had just powered up. The reset remains active as long as the current I<sup>2</sup>C transfer is active. Accordingly, the I<sup>2</sup>C logic itself is excluded, or it would not properly acknowledge (ACK) the current command.

0x02: STATUS - Instantaneous orientation status (read only)

Table 11: Instantaneous orientation status, register 0x02 (read only)

|    |    |    |     |         | <u>,                                    </u> |          | ,        |

|----|----|----|-----|---------|----------------------------------------------|----------|----------|

| D7 | D6 | D5 | D4  | D3      | D2                                           | D1       | D0       |

| 0  | 0  | 0  | ORD | ORIZ[1] | ORIZ[0]                                      | ORIXY[1] | ORIXY[0] |

The ORIXY[1:0] and ORIZ[1:0] bits are identical to ORXY[1:0] and ORZ[1:0], respectively, except that they are not subject to the same low-pass filtering as ORXY[1:0] and ORZ[1:0]. ORIXY[1:0] and ORIZ[1:0] are not normally used in the end application but are provided as outputs for information purposes.

ORD indicates that the OTP memory has been read. If a controller were to read a device before the OTP memory was read in, the results would be inaccurate, since the calibration data has not yet been loaded. Afterward, this bit will be 1 and cannot be reset by the user.

0x03: XOUT Upper - X-axis acceleration output MSB

Table 12: XOUT Upper, register 0x03

|          |          |         | <u> </u> | · oppor, rog | iotoi oxoo |         |         |

|----------|----------|---------|----------|--------------|------------|---------|---------|

| D7       | D6       | D5      | D4       | D3           | D2         | D1      | D0      |

| XOUT[11] | XOUT[10] | XOUT[9] | XOUT[8]  | XOUT[7]      | XOUT[6]    | XOUT[5] | XOUT[4] |

0x04: XOUT Lower - X-axis acceleration output LSB

Table 13: XOUT Lower, register 0x04

| D7      | D6      | D5      | D4      | D3 | D2 | D1 | D0 |

|---------|---------|---------|---------|----|----|----|----|

| XOUT[3] | XOUT[2] | XOUT[1] | XOUT[0] | 0  | 0  | 0  | 0  |

XOUT[11:0] is the 12-bit X-axis acceleration output. The output is in 2's complement format, with a range of -2048 to +2047.

0x05: YOUT Upper - Y-axis acceleration output MSB

Table 14: YOUT Upper, register 0x05

|          |          |         | 451C 17. 1 CC | i opper, reg | ISTOI OXOO |         |         |

|----------|----------|---------|---------------|--------------|------------|---------|---------|

| D7       | D6       | D5      | D4            | D3           | D2         | D1      | D0      |

| YOUT[11] | YOUT[10] | YOUT[9] | YOUT[8]       | YOUT[7]      | YOUT[6]    | YOUT[5] | YOUT[4] |

0x06: YOUT Lower - Y-axis acceleration output LSB

Table 15: YOUT Lower, register 0x06

| D7      | D6      | D5      | D4      | D3 | D2 | D1 | D0 |

|---------|---------|---------|---------|----|----|----|----|

| YOUT[3] | YOUT[2] | YOUT[1] | YOUT[0] | 0  | 0  | 0  | 0  |

YOUT[11:0] is the 12-bit y-axis acceleration output. Format is identical to the XOUT[11:0] output.

0x07: ZOUT Upper - Z-axis acceleration output MSB

Table 16: ZOUT Upper, register 0x07

| D7       | D6       | D5      | D4      | D3      | D2      | D1      | D0      |

|----------|----------|---------|---------|---------|---------|---------|---------|

| ZOUT[11] | ZOUT[10] | ZOUT[9] | ZOUT[8] | ZOUT[7] | ZOUT[6] | ZOUT[5] | ZOUT[4] |

0x08: ZOUT Lower - Z-axis acceleration output LSB

Table 17: ZOUT Lower, register 0x08

| i dibio i i i = o o i = o i o o ji o o o o o |         |         |         |    |    |    |    |

|----------------------------------------------|---------|---------|---------|----|----|----|----|

| D7                                           | D6      | D5      | D4      | D3 | D2 | D1 | D0 |

| ZOUT[3]                                      | ZOUT[2] | ZOUT[1] | ZOUT[0] | 0  | 0  | 0  | 0  |

ZOUT[11:0] is the 12-bit z-axis acceleration output. Format is identical to the XOUT[7:0] output.

0x09: TOUT - Temperature output

Table 18: TOUT, register 0x09

| D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TOUT[7] | TOUT[6] | TOUT[5] | TOUT[4] | TOUT[3] | TOUT[2] | TOUT[1] | TOUT[0] |

MXC400xXC contains an on-chip temperature sensor whose output can be read through the  $I^2C$  interface. The output is in 2's complement format. The nominal value of TOUT[7:0] is 0 at a temperature of  $25^{\circ}C$ , and the sensitivity of the output is approximately  $0.586^{\circ}C/LSB$ .

0x0A: INT\_MASK0 - Shake & orientation detection interrupt mask (write only)

Table 19: Shake & orientation detection interrupt mask, register 0x0A (write only)

| rable to: Onake a crientation actobion interrupt mack, regioter exert (write only) |       |    |    |       |       |       |       |  |

|------------------------------------------------------------------------------------|-------|----|----|-------|-------|-------|-------|--|

| D7                                                                                 | D6    | D5 | D4 | D3    | D2    | D1    | D0    |  |

| ORZE                                                                               | ORXYE | -  | -  | SHYME | SHYPE | SHXME | SHXPE |  |

0x0B: INT\_MASK1 - Data ready, tilt & data ready interrupt mask (write only)

Table 20: Data ready interrupt mask, register 0x0B (write only)

|    |    |    |    | · · · · · · · · · · · · · · · · · · · |    |    |       |

|----|----|----|----|---------------------------------------|----|----|-------|

| D7 | D6 | D5 | D4 | D3                                    | D2 | D1 | D0    |

| 0  | -  | 0  | 0  | -                                     | -  | -  | DRDYE |

The INT\_MASKx registers are used to selectively enable or disable individual interrupts. When any bit in the INT\_MASKx register is set to 1, the corresponding interrupt in the INT\_SRCx register is enabled, allowing the event which set that bit in the INT\_SRCx register to produce an interrupt signal on the INT output pin. The INT output is the logical NOR of all bits in the INT\_SRC0 register and bits D2-D0 in the INT\_SRC1 register which are enabled by the corresponding bits in the INT\_MASKx register.

**Note**: The INT output is an active-low, open drain output. An external pull-up resistor is required on the INT pin when the INT output is used.

The bits in the INT\_SRCx registers are set when the events corresponding to those bits occur, regardless of the state of the corresponding bits in the INT\_MASKx register. This allows the I<sup>2</sup>C master to poll for occurrence of events, rather than to respond to interrupts created by the same events.

0x0C: DETECTION - Orientation and shake detection parameters (read/write)

Table 21: Orientation and shake detection parameters, register 0x0C (read/write)

| D7  | D6      | D5      | D4      | D3     | D2     | D1     | D0     |

|-----|---------|---------|---------|--------|--------|--------|--------|

| SHM | SHTH[2] | SHTH[1] | SHTH[0] | SHC[1] | SHC[0] | ORC[1] | ORC[0] |

ORC[1:0] sets the orientation count, which is the number of consecutive valid new orientation readings that must be made before a new orientation value is written into bits OR[1:0] in the STATUS register. The nominal rate at which readings are taken is 100 Hz. The number of consecutive valid orientation measurements required to effect a "long-term" orientation change is set by ORC[1:0] as follows: 00 - 16 readings, 01 - 32 readings, 10 - 64 readings, 11 - 128 readings.

SHC[1:0] sets the X/Y shake count, which determines the number of readings allowed between the first shake event (acceleration exceeding the threshold set by SHTH[2:0]) and the second shake event (acceleration breaking the threshold with opposite sign, if SHM = 0, or just reversing sign, if SHM = 1). The number of readings is set by SHC[1:0] as follows: 00 - 8 readings, 01 - 16 readings, 10 - 32 readings, 11 - 64 readings.

SHTH[2:0] sets the X/Y shake threshold that acceleration must exceed to trigger the first shake event. SHTH[2:0] sets the shake threshold for the X, Y, and Z axes to a value between 0.25g (for SHTH[2:0]=000) and 2.0g (for SHTH[2:0]=111); each increment of SHTH[2:0] by 1 LSB increases shake threshold by 0.25g.

SHM is the X/Y shake mode bit. If SHM = 0, then for a shake to be detected, the second shake event must exceed the threshold set by SHTH[2:0] with the opposite sign of the first shake event, within the number of readings set by SHC[1:0]. If SHM = 1, then the second shake event must just have the opposite sign of the first shake event within the number of readings set by SHC[1:0].

0x0D: CONTROL - Operating mode control and full-scale range (read/write)

Table 22: Operating mode control and full-scale range, register 0x0D (read/write)

|    |        | P - 1 - 1 - 1 - 1 - 1 - 1 |       |    |    |    |    |

|----|--------|---------------------------|-------|----|----|----|----|

| D7 | D6     | D5                        | D4    | D3 | D2 | D1 | D0 |

| -  | FSR[1] | FSR[0]                    | Cksel | -  | -  | 0  | PD |

PD is the power down bit. Setting PD = 1 places MXC400xXC into a low-power, non-functional power down state.

Cksel allows to operate MXC400xXC with external clock for test purposes. When this bit is high the SCL input is used to drive the clock generator instead of internal oscillator. This is a factory-only bit. Always write it a 0. The part may be damaged if this bit is set to a 1.

FSR[1:0] determine the full-scale input acceleration range of MXC400xXC. The following table summarizes the full scale input ranges and output sensitivities for the XOUT, YOUT, and ZOUT acceleration outputs for each setting. In order for the user to be able to set full-scale range, the FSRE (FSR enable) bit in register address 0x19 must be set to 1 by factory programming. If FSRE is 0, the FSR[1:0] bits are ignored, and MXC400xXC is set to the  $\pm 2g$  range.

Table 23: Full-scale Range and Sensitivity

| FSR[1] | FSR[0] | Range (g) | Sensitivity (LSB/g) |

|--------|--------|-----------|---------------------|

| 0      | 0      | ±2        | 1024                |

| 0      | 1      | ±4        | 512                 |

| 1      | 0      | ±8        | 256                 |

| 1      | 1      | Undefined | N/A                 |

0x0E: Device ID, currently has a value of 0x02.

0x0F: Who\_Am\_I - is a read-only register to identify the MXC400xXC.

Table 24: Who\_Am\_I, register 0x0F

| D7     | D6     | D5     | D4     | D3     | D2     | D1     | D0     |

|--------|--------|--------|--------|--------|--------|--------|--------|

| WAI[7] | WAI[6] | WAI[5] | WAI[4] | WAI[3] | WAI[2] | WAI[1] | WAI[0] |

WAI[7:0] is an 8-bit version code programmed by the factory into non-volatile memory on MXC400xXC.

# **PACKAGE OUTLINE DRAWING**

Figure 12: Mechanical package outline dimensions

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

MEMSIC: MXC4005XC