# **VPC3+ Evaluation Kit**

(Order No.: PA006300)

**Revision 2.00**

#### Liability Exclusion

We have tested the contents of this document regarding agreement with the hardware and software described. Nevertheless, there may be deviations and we do not guarantee complete agreement. The data in the document is tested periodically, however. Required corrections are included in subsequent versions. We gratefully accept suggestions for improvements.

#### Copyright

Copyright © profichip GmbH 2005. All Rights Reserved. Unless permission has been expressly granted, passing on this document or copying it, or using and sharing its content are not allowed. Offenders will be held liable. All rights reserved, in the event a patent is granted or a utility model or design is registered.

This document is subject to technical changes.

| VF | °C3+                         | Evaluation Kit                                                                                                                                                                                                                                                                                                                                                                                                                | i                                         |

|----|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1  | Intr                         | oduction                                                                                                                                                                                                                                                                                                                                                                                                                      | .1                                        |

|    | 1.1<br>1.2<br>1.3            | Overview<br>Document Conventions<br>Handling the Boards                                                                                                                                                                                                                                                                                                                                                                       | 2                                         |

| 2  | AT                           | 39C5132 Board                                                                                                                                                                                                                                                                                                                                                                                                                 | .3                                        |

|    | 2.13<br>2.14<br>2.15<br>2.16 | Overview<br>AT89C5132 board<br>AT89C5132<br>In System Programming<br>Address Map<br>Internal/External Clock (Jumper X6)<br>Display Elements<br>I/O Area<br>Reset Button S4<br>Reset Button S4<br>RS232 Interface<br>LCD<br>RTC<br>MMC<br>I2C<br>Connector<br>2.15.1 Users Board Connector ( X4 )<br>2.15.2 MPI Board ( Main Connector, X5 )<br>2.15.3 MPI Board ( Extension Connector, X9 )<br>Power Supply<br>Technical Data | 4<br>5<br>5<br>6<br>6<br>6<br>7<br>7<br>7 |

| 3  | VPO                          | C3+/C Extension Board                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                        |

|    | 3.1<br>3.2<br>3.3            | Overview<br>Board VPC3+/C<br>Jumpers<br>3.3.1 VPC3+/C microcontroller mode<br>3.3.2 VPC3+/C clock divider<br>3.3.3 Select PROFIBUS interface<br>3.3.4 Select Opto/ADuM Interface                                                                                                                                                                                                                                              | 14<br>15<br>15<br>15<br>16                |

|    | 3.4                          | Connectors                                                                                                                                                                                                                                                                                                                                                                                                                    | 17<br>17<br>17                            |

|    | 3.5                          | Display Elements                                                                                                                                                                                                                                                                                                                                                                                                              | 19                                        |

|    | 3.6                          | PROFIBUS Interfaces                                                                                                                                                                                                                                                                                                                                                                                                           | 19                                        |

|    | 3.7                          | 3.6.2 Fiber Optic Interface<br>Technical Data                                                                                                                                                                                                                                                                                                                                                                                 |                                           |

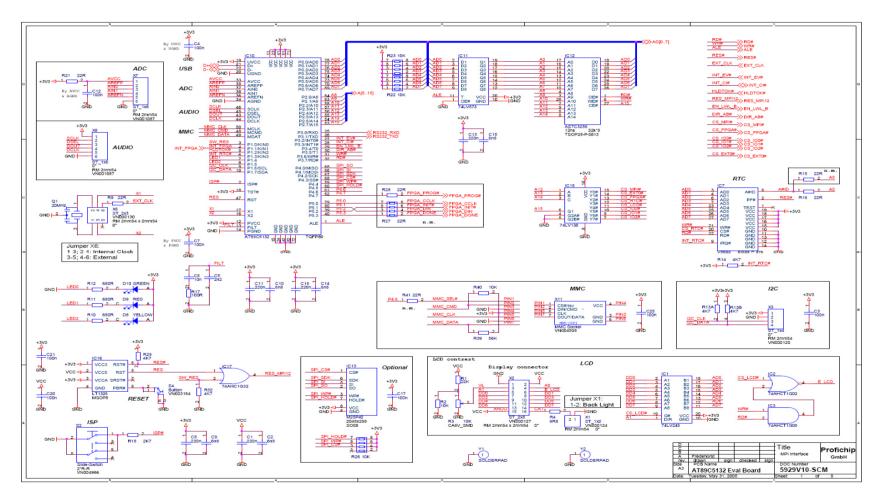

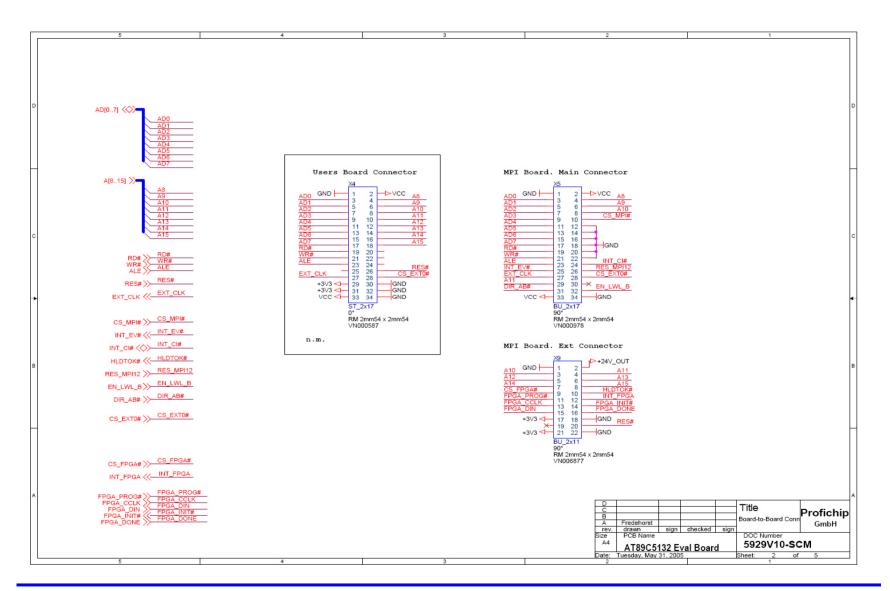

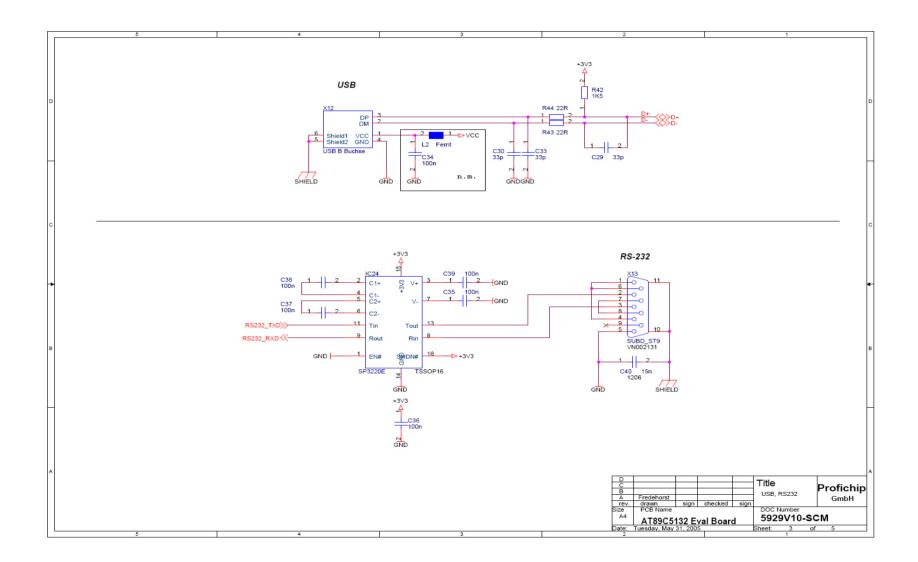

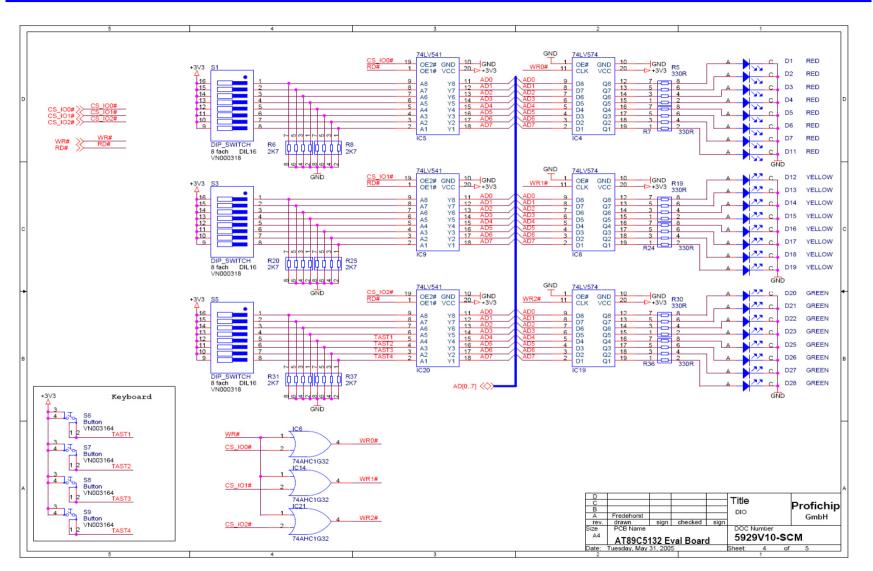

| 4  | -                            | nematics                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |

|   |     | AT89C5132<br>VPC3+/C Extension Board | -  |

|---|-----|--------------------------------------|----|

| 5 | ISP | (InSystemProgramming)                | 33 |

|   |     | ATMEL FLIP 2.4.4<br>How to use FLIP  |    |

# Introduction 1

## 1.1 Overview

Profichip's VPC3+ Evaluation Kit contains all the necessary hardware and software to easily connect to PROFIBUS-DP.

It consists of:

- Controller board with Atmel 89C5132 microcontroller

- 8-bit MCU C51 Core-based (FMAX = 20 MHz)

- 2304 Bytes of Internal RAM

- 64K Bytes of Code Memory (Flash)

- USB Rev 1.1 Device Controller

- 32kByte external RAM

- RS232 interface

- LCD-display

- Real Time Clock

- wide range of power supply (DC 7-24V)

- all relevant signals are applied to the plug connectors

- DIP-switches and LED's

- VPC3+/C extension board

- PROFIBUS link via RS485

- PROFIBUS link via fiber optic interface

- VPC3+ configurations are done with jumpers

- all relevant signals are applied to the plug connectors

- PROFIBUS software driver

- DPV0 software driver

- DPV1 software driver

- PROFIBUS demo program

- DPV1AFFE: demo program for DPV1

- DPV0AFFE: demo program for DPV0

- Documentation

# **1** Introduction

# **1.2 Document Conventions**

In this User Description signal names appear in italic.

Low active signals are denoted by a "#" after the signal name (i.e.: *RD*#).

A '0' indicates a logic-zero or low-level signal, while a '1' represents a logic-one or high-level signal.

# **1.3 Handling the Boards**

Handle the VPC3+ evaluation boards with care in respect to ESD requirements. Take precautions to use the boards only at an ESD-safe workplace.

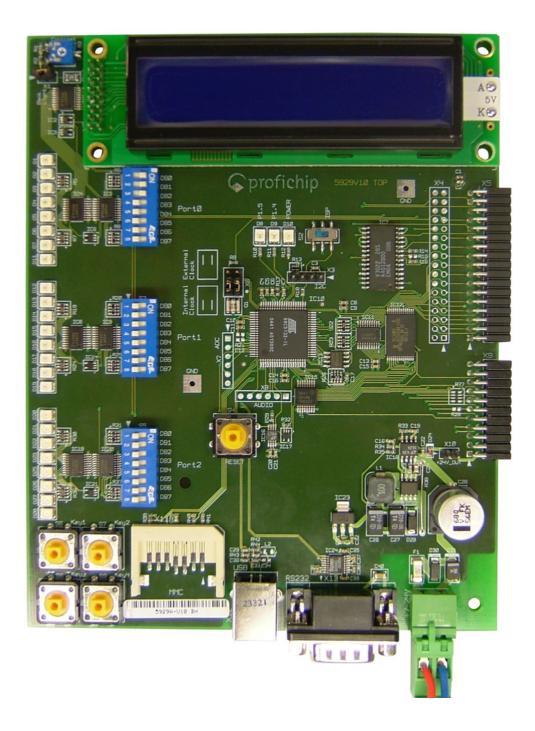

#### 2.1 Overview

The AT89C5132 board consist of:

- Atmel 89C5132 microcontroller (USB C51-based Microcontroller with 64K Bytes Flash, 2304 bytes RAM, 4 USB Endpoints, SPI, UART, IDE, TWI, MultiMediaCard, DataFlash, I2S, 10-bit ADC)

- 32kByte external RAM

- RS232 interface

- LCD-display

- Real Time Clock

- wide range of power supply (DC 7-24V)

- all relevant signals are applied to the plug connectors

- DIP-switches and LED's

# 2 AT89C5132 Board

# 2.2 AT89C5132 board

Figure 2-1: AT89C5132

# 2.3 AT89C5132

USB C51-based Microcontroller with 64K Bytes Flash, 2304 bytes RAM, 4 USB Endpoints, SPI, UART, IDE, TWI, MultiMediaCard, DataFlash, I2S, 10-bit ADC. The functionality of AT89C5132 is described more detailed in the document 4173.pdf.

# 2.4 In System Programming

The ISP area contains a switch that allows the user to select the AT89C5132 hardware condition and thus execute the embedded bootloader or to run the client application.

| ISP | Position | Execute            |

|-----|----------|--------------------|

|     |          | Client Application |

|     | ISP      | Bootloader         |

Figure 2-2: Switch S2, ISP

#### 2.5 Address Map

Fehler! Verweisquelle konnte nicht gefunden werden. shows the address mapping of the AT89C5132 controller board.

| Address      | Description                |

|--------------|----------------------------|

| 0000 – 7FFFH | External RAM               |

| 8000 – 8FFFH | VPC3+/C                    |

| 9000 – 9FFFH | Reserved                   |

| A000 – AFFFH | FPGA on VPC3+/C Base Board |

| B000 – BFFFH | RTC                        |

| C000 – CFFFH | LCD                        |

| D000 – DFFFH | I/O Port 0                 |

| E000 – EFFFH | I/O Port 1                 |

| F000 – FFFFH | I/O Port 2                 |

| Figure | 2-3: | Address | Мар |

|--------|------|---------|-----|

|--------|------|---------|-----|

# 2 AT89C5132 Board

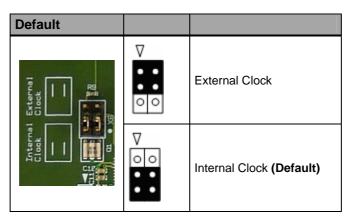

# 2.6 Internal/External Clock (Jumper X6)

The clock supply of the microcontroller can be determined by setting the jumper X6. There are two possibilities for the controller's clock supply: The controller can either get it's clock from the 20 MHz crystal oscillator on the AT89C5132 board (Internal Clock) or from the CLKOUT2/4 pin of the VPC 3+ on the Extension board (External Clock):

Figure 2-4: Settings of Jumper X6

## 2.7 Display Elements

The Extension Board has three LEDs: The green LED D10 indicates correct power supply. The red LED D9 and the yellow LED D8 are connected to the ports P1.4 and P1.5 of the controller.

#### 2.8 I/O Area

The I/O area consist of 3 DIP switches (Port0, Port1, Port2) and 3 LED lines.

The data bus lines to the DIP switches are connected via pulldown resistors to GND. If a DIP switch is OFF, the corresponding input port of the controller is connected via pulldown resistor to GND and the controller therefore reads a logical '0' from this DIP-switch. If the DIP-switch is ON, the controller's input is connected to VCC via the DIP-switch and the controller therefore reads a logical '1' on this port.

#### 2.9 Reset Button S4

The entire application can be reseted by pressing the Reset Button S4.The microcontroller goes into a defined state and starts up the application program.

# 2.10 RS232 Interface

|   | Pin | Assignment |

|---|-----|------------|

|   | 1   | n.c.       |

|   | 2   | TxD        |

|   | 3   | RxD        |

|   | 4   | n.c.       |

|   | 5   | GND        |

|   | 6   | n.c.       |

| 9 | 7   | RTS        |

|   | 8   | CTS        |

| • | 9   | n.c.       |

|   |     |            |

Figure 2-5: Assignment of the RS232 Connector

# 2.11 LCD

The display area consist of a 2-line 20 characters LCD-display. The contrast is adjustable using R3 variable resistor. The LCD is described more detailed in the document

# 2.12 RTC

The V3022 is a low power CMOS real time clock with a built-in crystal. The interface is 8 bits with multiplexed address and data bus. Multiplexing of address and data is handled by the input line /D. The RTC is described more detailed in the document V3022\_DS.pdf.

# 2.13 MMC

Multi Media Card is not supported.

#### 2.14 I2C

I2C is not supported

# 2 AT89C5132 Board

# 2.15 Connector

# 2.15.1 Users Board Connector (X4)

| Pin | Signal name | In/Out | Description           |

|-----|-------------|--------|-----------------------|

| 1   | GND         | Out    | GND                   |

| 30  | GND         | Out    | GND                   |

| 32  | GND         | Out    | GND                   |

| 34  | GND         | Out    | GND                   |

| 2   | VCC         | Out    | +5V                   |

| 33  | VCC         | Out    | +5V                   |

| 29  | VCC_3.3V    | Out    | +3.3V                 |

| 31  | VCC_3.3V    | Out    | +3.3V                 |

| 3   | AD0         | In/Out | Address / Data line 0 |

| 5   | AD1         | In/Out | Address / Data line 1 |

| 7   | AD2         | In/Out | Address / Data line 2 |

| 9   | AD3         | In/Out | Address / Data line 3 |

| 11  | AD4         | In/Out | Address / Data line 4 |

| 13  | AD5         | In/Out | Address / Data line 5 |

| 15  | AD6         | In/Out | Address / Data line 6 |

| 17  | AD7         | In/Out | Address / Data line 7 |

| 4   | A8          | Out    | Address line 8        |

| 6   | A9          | Out    | Address line 9        |

| 8   | A10         | Out    | Address line 10       |

| 10  | A11         | Out    | Address line 11       |

| 12  | A12         |        | Address line 12       |

| 14  | A13         |        | Address line 13       |

| 16  | A14         |        | Address line 14       |

| 18  | A15         |        | Address line 15       |

| 19  | RD#         | Out    | Read select           |

| 21  | WR#         | Out    | Write select          |

| 23  | ALE         | Out    | Address latch enable  |

| 26  | RES         | Out    | Reset                 |

| 27  | EXT_CLK     | In     | External clock        |

| 28  | CS_EXT0#    | Out    | Chip select           |

| 20  |             |        | Not connected         |

| 22  |             |        | Not connected         |

| 24  |             |        | Not connected         |

| 25  |             |        | Not connected         |

Figure 2-6: Assignment of Connector X5

| Pin | Signal name | In/Out | Description                                      |

|-----|-------------|--------|--------------------------------------------------|

| 1   | GND         | Out    | GND                                              |

| 12  | GND         | Out    | GND                                              |

| 14  | GND         | Out    | GND                                              |

| 16  | GND         | Out    | GND                                              |

| 18  | GND         | Out    | GND                                              |

| 20  | GND         | Out    | GND                                              |

| 22  | GND         | Out    | GND                                              |

| 34  | GND         | Out    | GND                                              |

| 2   | VCC         | Out    | +5V                                              |

| 33  | VCC         | Out    | +5V                                              |

| 3   | AD0         | In/Out | Address / Data line 0                            |

| 5   | AD1         | In/Out | Address / Data line 1                            |

| 7   | AD2         | In/Out | Address / Data line 2                            |

| 9   | AD3         | In/Out | Address / Data line 3                            |

| 11  | AD4         | In/Out | Address / Data line 4                            |

| 13  | AD5         | In/Out | Address / Data line 5                            |

| 15  | AD6         | In/Out | Address / Data line 6                            |

| 17  | AD7         | In/Out | Address / Data line 7                            |

| 4   | A8          | Out    | Address line 8                                   |

| 6   | A9          | Out    | Address line 9                                   |

| 8   | A10         | Out    | Address line 10                                  |

| 10  | CS#         | Out    | Chip select for the VPC3+                        |

| 19  | RD#         | Out    | Read select                                      |

| 21  | WR#         | Out    | Write select                                     |

| 23  | ALE         | Out    | Address latch enable                             |

| 24  | INT_CI#     | In     | Interrupt output                                 |

| 25  | INT_EV#     | In     | Interrupt output                                 |

| 26  | RES_MPI12x  | Out    | Reset for VPC3+                                  |

| 27  | EXT_CLK     | In     | VPC3+ clock output, 12 MHz or 24 MHz             |

| 28  | CS_EXT0#    | Out    | Chip select for DIP-switches and LEDs            |

| 31  | DIR_AB#     | Out    | Direction reverser for the fibre optic interface |

| 32  | EN_LWL_B    | Out    | Enable signal for fibre optic interface B        |

| 29  | A11         | Out    | Address line 11                                  |

| 30  |             |        | Not connected                                    |

# 2.15.2 MPI Board (Main Connector, X5)

Figure 2-7: Assignment of Connector X5

# 2 AT89C5132 Board

| Pin | Signal name | In/Out | Description      |

|-----|-------------|--------|------------------|

| 1   | GND         | Out    | GND              |

| 18  | GND         | Out    | GND              |

| 22  | GND         | Out    | GND              |

| 2   | 24V_OUT     | Out    | +24V             |

| 17  | VCC_3.3V    | Out    | +3.3V            |

| 21  | VCC_3.3V    | Out    | +3.3V            |

| 3   | A10         | Out    | Address line 10  |

| 4   | A11         | Out    | Address line 11  |

| 5   | A12         | Out    | Address line 12  |

| 6   | A13         | Out    | Address line 13  |

| 7   | A14         | Out    | Address line 14  |

| 8   | A15         | Out    | Address line 15  |

| 10  | HLDTOK#     | In     | Hold Token       |

| 12  | INT_FPGA    | In     | Interrupt FPGA   |

| 9   | CS_FPGA'    | Out    | Chip select FPGA |

| 11  | FPGA_PROG#  | Out    |                  |

| 13  | FPGA_CCLK   | Out    |                  |

| 15  | FPGA_DIN    | Out    | FPGA             |

| 14  | FPGA_INIT#  | In     |                  |

| 16  | FPGA_DONE   | Out    |                  |

| 20  | RES#        | Out    | Reset            |

| 19  |             |        | Not connected    |

# 2.15.3 MPI Board (Extension Connector, X9)

Figure 2-8: Assignment of Connector X9

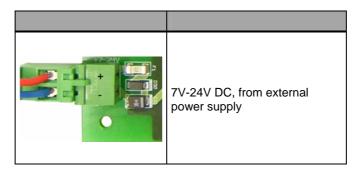

# 2.16 Power Supply

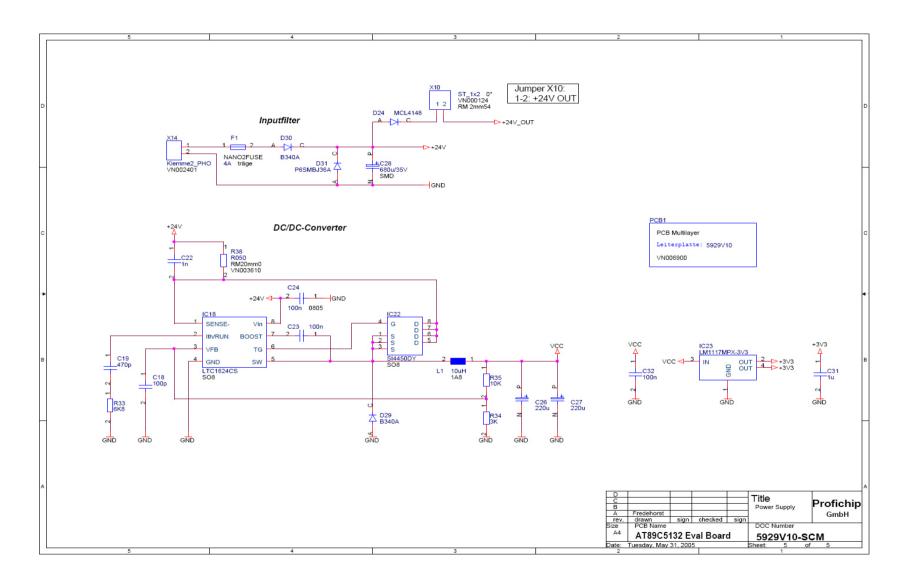

Figure 2-9: Power Supply

# 2 AT89C5132 Board

# 2.17 Technical Data

| Electrical data       | C501 Extension Board                |

|-----------------------|-------------------------------------|

| Power supply          | 7V – 24V DC, from ext. power supply |

| Current consumption   |                                     |

| Operating temperature | 0°C to +70°C                        |

| Dimensions and Weight |                                     |

| Dimensions (LxWxH)    | 89mm x 180mm x 16mm                 |

| Weight                |                                     |

Figure 2-10 : Technical data

## 3.1 Overview

The extension board contains all necessary hardware to connect to PROFIBUS:

- VPC3+/C slave ASIC

- 48 MHz clock generator

- RS485 interface

- realized with opto coupler

- realized with ADuM

- electrical isolation

- fiber optic interface

- FPGA (for internal use)

# 3 VPC3+/C Extension Board

# 3.2 Board VPC3+/C

Figure 3-1: Extension Board VPC3+/C

# 3.3 Jumpers

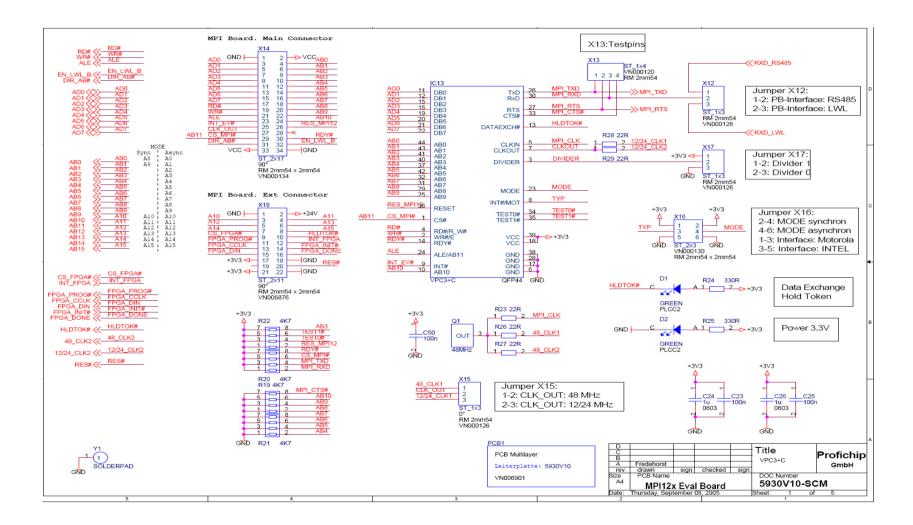

#### 3.3.1 VPC3+/C microcontroller mode

Jumper X16 selects the VPC3+ microcontroller mode:

| Mode      | Default setting      | Interface |

|-----------|----------------------|-----------|

| asynchron | ADDER X15 Thterfaces | Intel     |

| synchron  | s synce atorola      | Motorola  |

Figure 3-2: VPC3+/C microcontroller mode

#### 3.3.2 VPC3+/C clock divider

Jumper X17 selects the VPC3+/C CLK to CLKOUT2/4 divider:

| Default                              | Default setting                                            |

|--------------------------------------|------------------------------------------------------------|

| DividerØ<br>Divider1<br>async<br>ync | Divider 0: CLK divided by 4<br>Divider 1: CLK divided by 2 |

Figure 3-3: VPC3+/C clock divider

# 3 VPC3+/C Extension Board

#### 3.3.3 Select PROFIBUS interface

Jumper X12 selects the PROFIBUS interface to be used (the print on the PCB is wrong):

| Default (RS485)        | Interface                              |                                    |

|------------------------|----------------------------------------|------------------------------------|

| PB_Internapti<br>PSHIG | $\triangleright \bullet \bullet \circ$ | Fiber optic interface              |

| X12                    |                                        | RS485 PROFIBUS interface (DEFAULT) |

Figure 3-4: PROFIBUS interface

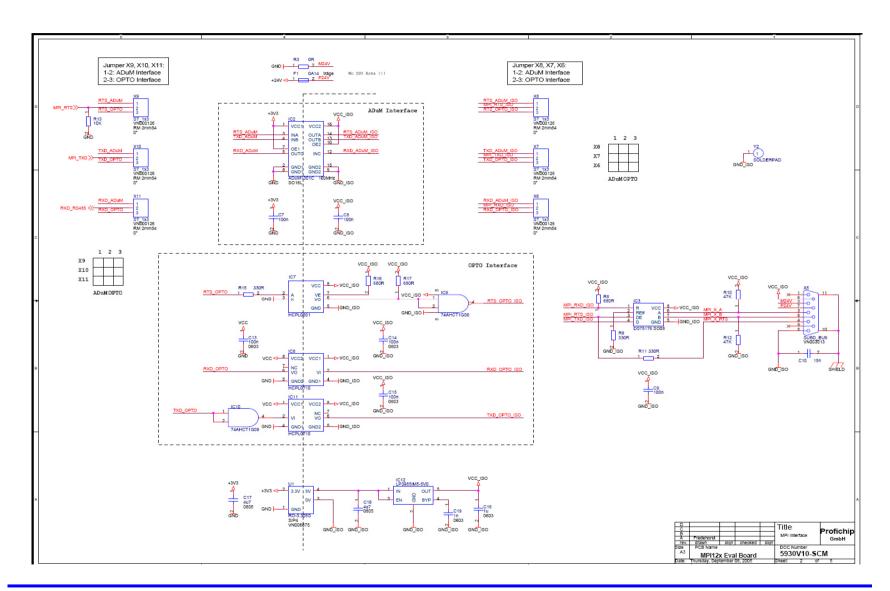

#### 3.3.4 Select Opto/ADuM Interface

Jumper X6..X11 selects the Opto/ADuM interface:

| Default (RS485)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interface |                          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------|--|

| Strain and a strai |           | ADuM interface           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OPTO      | OPTO interface (DEFAULT) |  |

Figure 3-5: PROFIBUS interface

# 3.4 Connectors

#### 3.4.1 Testpins X13

| Pin | Signal name | In/Out Description |               |

|-----|-------------|--------------------|---------------|

| 1   | TXD         | Out                | Transmit Data |

| 2   | RTS         | Out                | Ready to send |

| 3   | RXD         | In                 | Receive Data  |

| 4   | CTS         | In                 | Clear to send |

Figure 3-6: Assignment of Connector X13

#### 3.4.2 Main Connector X14

| Pin | Signal name | In/Out Description |                 |

|-----|-------------|--------------------|-----------------|

| 1   | GND         | In GND             |                 |

| 34  | GND         | In                 | GND             |

| 2   | VCC         | In                 | +5V             |

| 33  | VCC         | In                 | +5V             |

| 3   | AD0         | In/Out             | Data line 0     |

| 5   | AD1         | In/Out             | Data line 1     |

| 7   | AD2         | In/Out             | Data line 2     |

| 9   | AD3         | In/Out             | Data line 3     |

| 11  | AD4         | In/Out             | Data line 4     |

| 13  | AD5         | In/Out             | Data line 5     |

| 15  | AD6         | In/Out Data line 6 |                 |

| 17  | AD7         | In/Out Data line 7 |                 |

| 4   | AB0         | In Address line 0  |                 |

| 6   | AB1         | In                 | Address line 1  |

| 8   | AB2         | In                 | Address line 2  |

| 10  | AB3*        | In                 | Address line 3  |

| 12  | AB4         | In Address line 4  |                 |

| 14  | AB5         | In Address line 5  |                 |

| 16  | AB6         | In Address line 6  |                 |

| 18  | AB7         | In Address line 7  |                 |

| 20  | AB8         | In Address line 8  |                 |

| 22  | AB9         | In                 | Address line 9  |

| 24  | AB10        | In                 | Address line 10 |

| 29  | AB11        | In                 | Address line 10 |

| 19  | RD#         | In Read select     |                 |

# 3 VPC3+/C Extension Board

| 21 | WR#      | In  | Write select                                     |

|----|----------|-----|--------------------------------------------------|

| 23 | ALE      | In  | Address latch enable                             |

| 25 | INT#     | Out | VPC3+ interrupt output                           |

| 26 | RESET    | In  | Reset from microcontroller                       |

| 27 | CLKOUT   | Out | VPC3+ clock output, 12 MHz or 24 MHz             |

| 30 | RDY#     | Out | Ready from VPC3+                                 |

| 31 | DIR_AB#  | In  | Direction reverser for the fibre optic interface |

| 32 | EN_LWL_B | In  | Enable signal for fibre optic interface B        |

| 28 |          |     | Not Connected                                    |

Figure 3-7: Assignment of Connector X14

#### 3.4.3 Extension Connector X14

| Pin | Signal name | In/Out             | Description      |

|-----|-------------|--------------------|------------------|

| 1   | GND         | In                 | GND              |

| 18  | GND         | In                 | GND              |

| 22  | GND         | In                 | GND              |

| 2   | 24V_OUT     | In                 | +24V             |

| 17  | VCC_3.3V    | In                 | +3.3V            |

| 21  | VCC_3.3V    | In                 | +3.3V            |

| 3   | A10         | In                 | Address line 10  |

| 4   | A11         | In                 | Address line 11  |

| 5   | A12         | In                 | Address line 12  |

| 6   | A13         | In                 | Address line 13  |

| 7   | A14         | In Address line 14 |                  |

| 8   | A15         | In                 | Address line 15  |

| 10  | HLDTOK#     | Out                | Hold Token       |

| 12  | INT_FPGA    | Out                | Interrupt FPGA   |

| 9   | CS_FPGA'    | In                 | Chip select FPGA |

| 11  | FPGA_PROG#  | In                 |                  |

| 13  | FPGA_CCLK   | In                 |                  |

| 15  | FPGA_DIN    | In                 | FPGA             |

| 14  | FPGA_INIT#  | Out                |                  |

| 16  | FPGA_DONE   | In                 |                  |

| 20  | RES#        | In                 | Reset            |

| 19  |             |                    | Not connected    |

Figure 3-8: Assignment of Connector X9

# 3.5 **Display Elements**

The evaluation board has two LEDs on board. The green LED D2 indicates correct power supply. The green LED D2 is connected to the *DATA\_EX*-output of the VPC3+ and lights up each time the VPC3+/C is in data exchange mode.

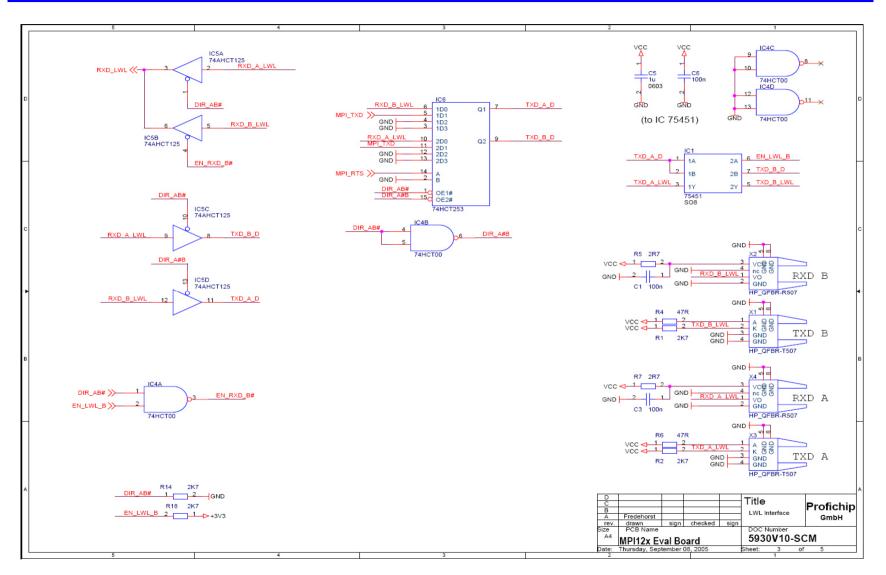

#### 3.6 **PROFIBUS** Interfaces

PROFIBUS uses a screened twisted pair cable connected to an RS485 interface or a full-duplex fiber-optic link as communication medium. The Evaluation Board offers both possibilities.

#### 3.6.1 RS485 Interface

The RS485 interface uses differential voltages. It is for this reason that this interface is less susceptible to interference than a plain voltage or current based interface. The network may be configured as a daisy-chain or in a tree configuration.

The VPC3+ evaluation board PROFIBUS coupler carries a 9-pin socket. This socket is used to connect the PROFIBUS coupler to the PROFIBUS network as a slave.

Each segment can support a maximum of 32 devices. Individual segments are linked by means of repeaters. The maximum length for a segment is determined by the transmission rate. In a PROFIBUS-DP network the transmission rate is adjusted automatically and ranges from 9.6 Kbit/s to 12 Mbit/s. Slaves adapt their communication rate automatically. All devices connected to the network communicate at the same transmission rate (baudrate).

Due to the bus structure of the network any station may be connected or disconnected without interruptions and a system can be commissioned in different stages. Extensions to the system do not affect stations that have already been commissioned. Any failures of stations or new devices are detected automatically.

|              | Pin | Assignment |

|--------------|-----|------------|

|              | 1   | n.c.       |

|              | 2   | M24V       |

|              | 3   | RxD/TxD-P  |

|              | 4   | CNTR-P     |

| ⊖″ <u></u> 3 | 5   | GND        |

| 08           | 6   | 5V         |

| O9<br>○5     | 7   | P24V       |

|              | 8   | RxD/TxD-N  |

| ~            | 9   | n.c.       |

Figure 3-9: Assignment of the RS485 PROFIBUS Connector

To prevent reflections and associated communication problems the bus cable must always be terminated with its characteristic impedance

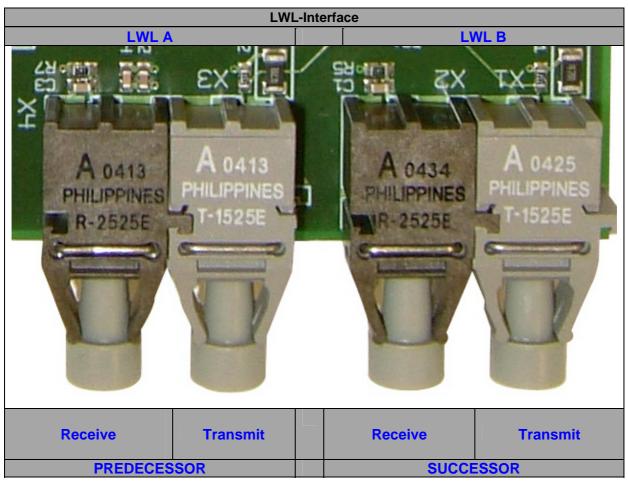

#### 3.6.2 Fiber Optic Interface

The fiber optic (FO) cable transfers signals by means of electromagnetic waves at optical frequencies. Total reflection will occur because the refractive index of the coating of the fiber optic cable is lower than that of the kernel. Due to the total reflection the ray of light cannot escape from the fiber optic conductor and it will be conducted to the end of the fiber optic cable.

The fiber optic system employs pulses of monochromatic light at a wavelength of 650nm. The fiber optic cable can be used in the same manner as any normal cable and it is not susceptible to external electrical interference. Fiber optic systems have a linear structure. Each device requires two lines, a transmit and a receive line (two-core). It is not necessary to provide a terminator at the last device.

The FO PPROFIBUS interface of the VPC3+/C extension board has four sockets. These sockets are used to connect the PROFIBUS slave directly to the PROFIBUS system. The PROFIBUS FO network supports a maximum of 126 devices (including the master). The maximum distance between two devices is limited to 50 m, the maximum baud rate is 12 Mbit/s.

Advantages of FO over copper cables:

- wide bandwidth

- low attenuation

- no crosstalk between cores

- immunity to external electrical interference

- no potential difference

- lightning protection

- may be installed in explosive environments

- low weight and more flexible

- corrosion resistant

- cannot be tapped easily

Figure 3-10: Postition of the Fiber Optic Interface

The signal lines *DIR\_AB#* and *EN\_LWL\_B* control the fiber optic interface. *EN\_LWL\_B* enables or disables the fiber optic interface B. This is only useful if no successor is behind the evaluation board in the PROFIBUS network. Signal *DIR\_AB#* controls the transmit and receive direction between the fiber optic sockets A and B:

| EN_LWL_B | Description                                                             |

|----------|-------------------------------------------------------------------------|

| '0'      | fiber optic interface B disabled                                        |

| '1'      | fiber optic interface B enabled <b>(DEFAULT)</b>                        |

| DIR_AB#  | Description                                                             |

| '0'      | Received data from A will be transmitted by B, and vice versa (default) |

| '1'      | Received data from B will be transmitted by A, and vice versa           |

Figure 3-11: Coding of EN\_LWL\_B and DIR\_AB

# 3.7 Technical Data

| Electrical data          | VPC3+ Base Board                                                                                    |

|--------------------------|-----------------------------------------------------------------------------------------------------|

| Power supply             | 5V DC, from ext. power supply or via AT89C5132,<br>3.3V DC, from ext. power supply or via AT89C5132 |

| Current consumption      | 5VDC :<br>3.3V DC :                                                                                 |

| Isolation                | ≥ 500V AC                                                                                           |

| Operating temperature    | 0°C to +70°C                                                                                        |

| RS485 PROFIBUS interfac  | ce                                                                                                  |

| Connection               | 9-pin D-type socket                                                                                 |

| Network topology         | Linear bus, active bus terminator at both ends, radial lines are permitted                          |

| Medium                   | Screened twisted pair cable, under certain conditions unscreened lines are permitted                |

| Data transfer rate       | 9,6 kBaud to 12 MBaud (automatic adjustment                                                         |

| Total length             | 100 m without repeaters for 12 MBaud, 1000 m with repeaters                                         |

| Max. no. of stations     | 32 stations in any segment without repeaters. Extendable to 126 stations when using repeaters.      |

| Fiber Optic PROFIBUS Int | erface                                                                                              |

| Connection               | 4-pole socket for fiber optic cable                                                                 |

| Network topology         | Linear structure with two-core FO cable, no bus terminator required                                 |

| Medium                   | two-core fiber optic cable                                                                          |

| Data transfer rate       | 9,6 kBaud to 12 Mbaud (automatic adjustment)                                                        |

| Total length             | max. 50 m between stations                                                                          |

| Max. no. of stations     | 126 stations incl. Master.                                                                          |

| Dimensions and Weight    |                                                                                                     |

| Dimensions (LxWxH)       | 89mm x 180mm x 16mm                                                                                 |

| Weight                   |                                                                                                     |

Figure 3-12: Base Board, Technical Data

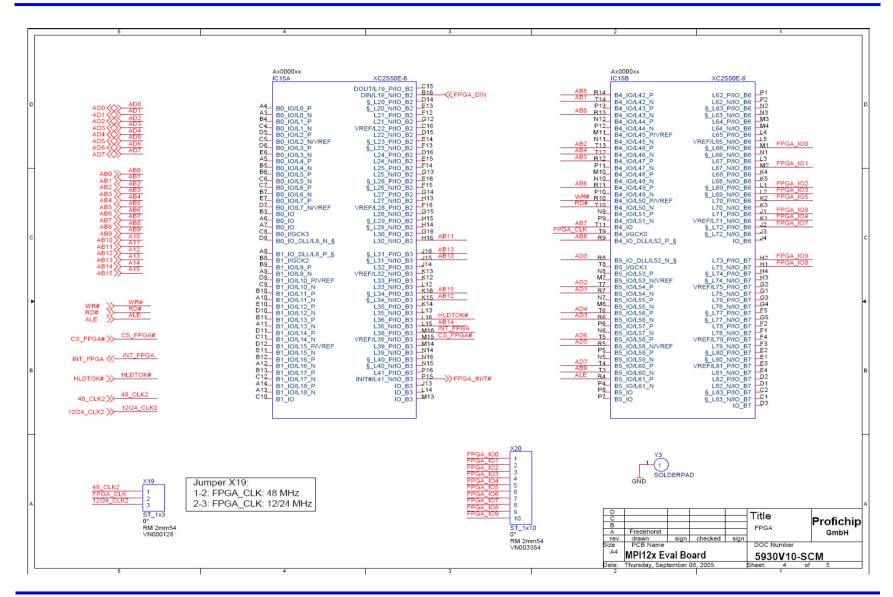

# 4.1 AT89C5132

VPC3+ Evaluation Kit

# 4.2 VPC3+/C Extension Board

VPC3+ Evaluation Kit

VPC3+ Evaluation Kit

# ISP (InSystemProgramming) 5

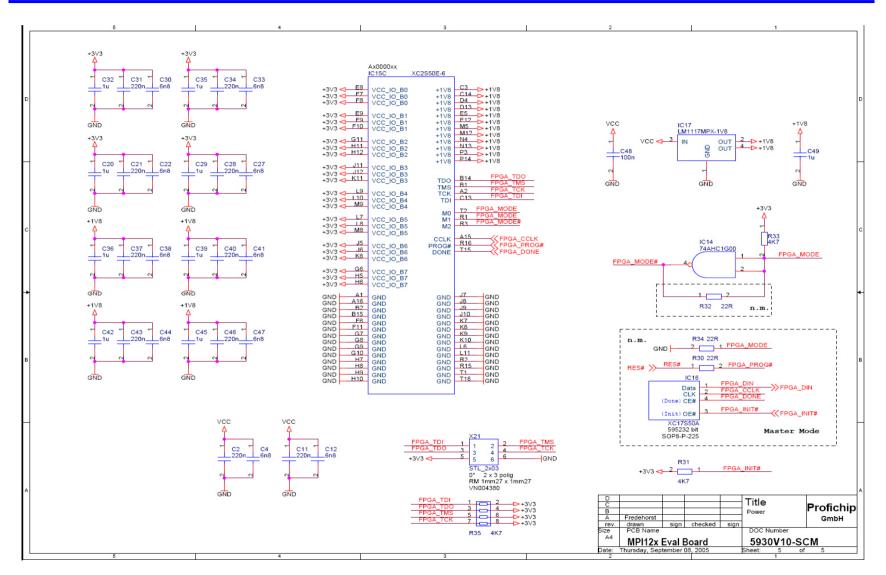

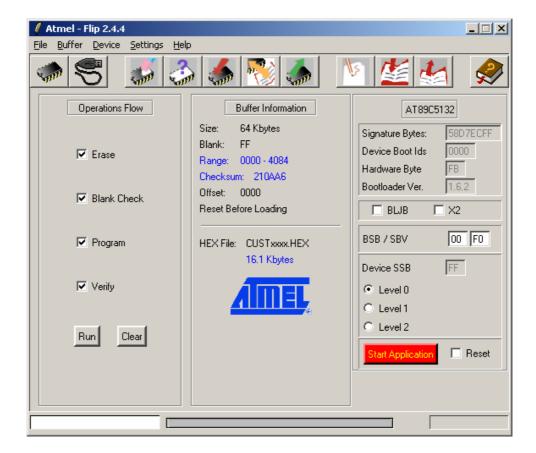

## 5.1 ATMEL FLIP 2.4.4

FLIP is a free PC-based software tool that supports the In-System Programming (ISP) of Atmel's Flash C51 microcontrollers through various communication interfaces, including RS232, USB and CAN links, both in Windows $_{\odot}$ 9x/Me/2000/XP, Windows NT $_{\odot}$  and Linux $_{\odot}$  environments.

FLIP can be used through a Graphical User Interface or launched from a DOS command window. FLIP is a powerful toolset which enables the user to easily embed Atmel's ISP function libraries (DLL) within their applications without having to know the details of Atmel's ISP protocols.

FLIP adds flexibility, power and user-friendliness to Atmel Flash C51 devices In-System Programming.

Figure 5-1: FLIP 2.4.4

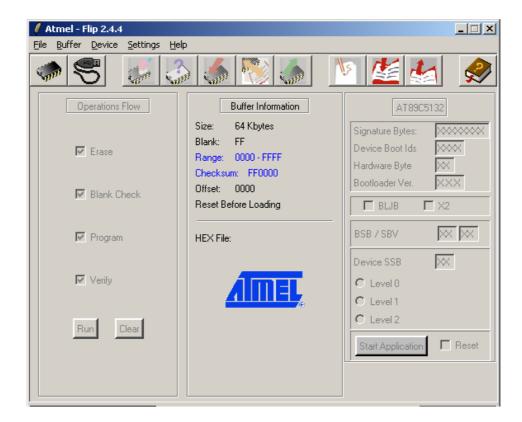

## 5.2 How to use FLIP

After the program FLIP is installed ( ..\ATMEL\FLIP\flip\_xyz.zip, setup.exe) the user has to select the type of microcontroller (FLIP Menu: Device/Select).

Figure 5-2: Device Selection

Set on Evaluation board switch S2 to ISP and connect USB cable:

| ISP                                   | Position | Execute            |

|---------------------------------------|----------|--------------------|

| S S S S S S S S S S S S S S S S S S S |          | Client Application |

|                                       | ISP      | Bootloader         |

Figure 5-3: Switch S2, ISP

#### Open USP Port

| 🦸 USB Por | t Connecti |        |

|-----------|------------|--------|

| Open      | Close      | Cancel |

Figure 5-4: Open USB Port

Load Firmware, start programming over the button RUN and press the button Start Application.

Figure 5-5: FLIP 2.4.4

5 ISP (InSystemProgramming)

Notes:

# **Revision History**

| Version | Date       | Page | Remarks |

|---------|------------|------|---------|

| V1.00   | 15.09.2005 |      |         |

profichip GmbH Einsteinstrasse 6 91074 Herzogenaurach Germany

Phone : +49.9132.744-200 Fax: +49.9132.744-204

www.profichip.com