# Date : Jan. 11, 2018

# SPECIFICATIONS

**Product Name**

# LPM035M407B

# Approval Signature

<u>To:</u>

| Approved by | Date | Proposed by | Date |

|-------------|------|-------------|------|

|             |      |             |      |

|             |      |             |      |

|             |      |             |      |

Please return 1 copy with your signature on this page for approval.

# Japan Display Inc.

Japan Display Inc.

Sh. No.

1

| No.   | <u>CONTENTS</u><br>Item                             | Page      |

|-------|-----------------------------------------------------|-----------|

| 1     | COVER                                               | 1 /35     |

|       | CONTENTS                                            | 2 /35     |

| 2     | RECORD OF REVISIONS                                 | 3 /35     |

| 3     | GENERAL DATA                                        | 4 /35     |

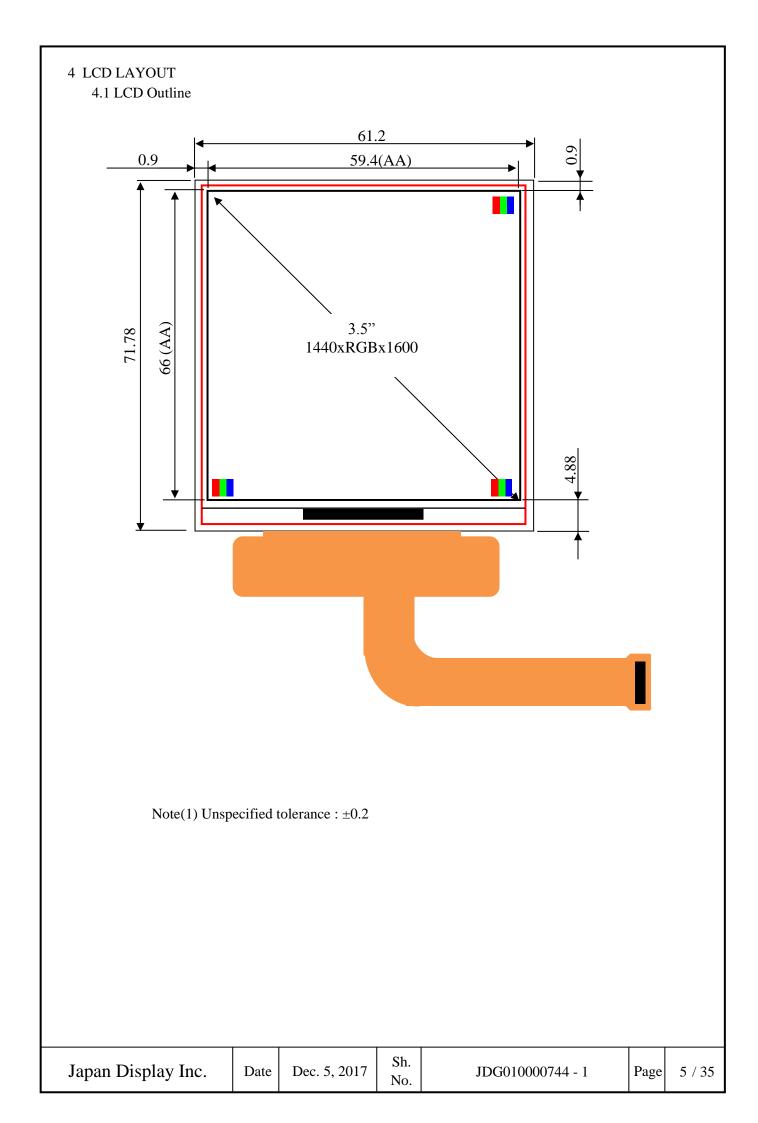

| 4     | LCD LAYOUT                                          | 5 /35     |

| 4.1   | LCD OUTLINE                                         | 5 /35     |

|       |                                                     |           |

| 5     | ABSOLUTE MAXIMUM RATINGS                            | 6 /35     |

| 5.1   | ELECTRICAL ABSOLUTE MAXIMUM RATINGS OF LCD          | 6 /35     |

| 5.2   | ENVIRONMENTAL ABSOLUTE MAXIMUM RATINGS              | 7 /35     |

| 6     | ELECTRICAL CHARACTERISTICS                          | 8 /35     |

| 7     | OPTICAL CHARACTERISTICS                             | 9~10 /35  |

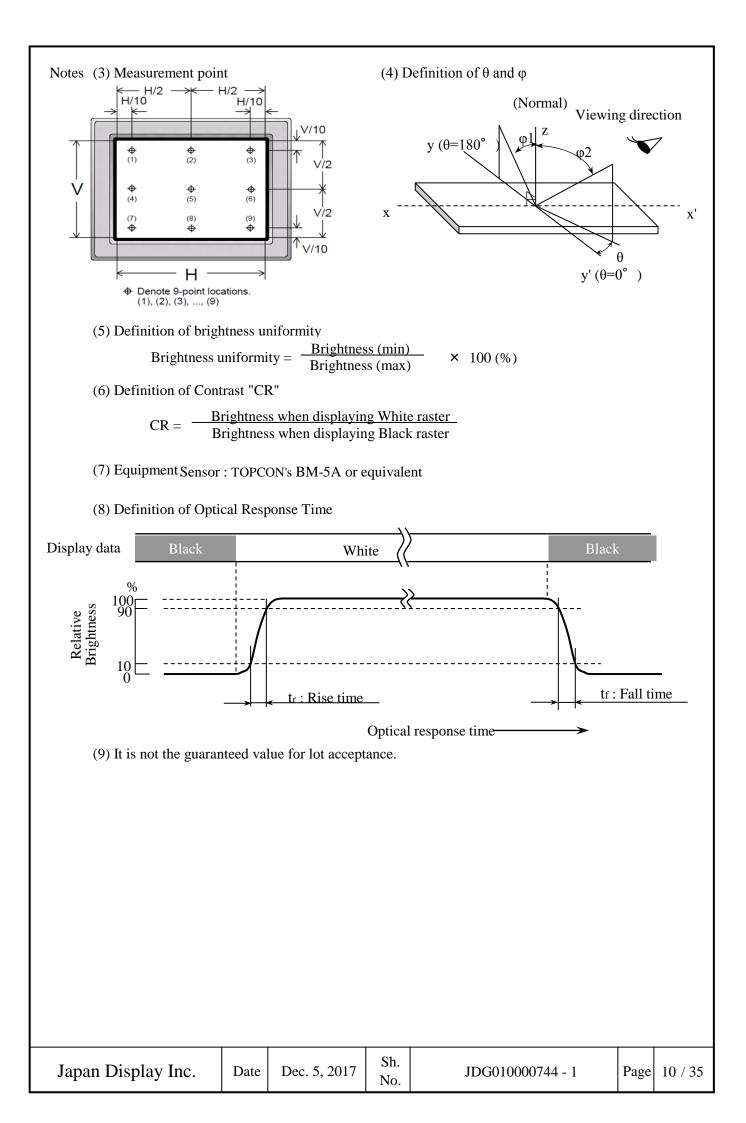

| 8     | BLOCK DIAGRAM                                       | 11 /35    |

| 9     | INTERFACE                                           | 12 /35    |

| 9.1   | INTERNAL PIN CONNECTION                             | 12 /35    |

| 9.2   | TIMING CHARACTERISTICS                              | 13~17 /35 |

| 9.3   | POWER ON/OFF SEQUENCE                               | 18 /35    |

| 9.4   | SEQUENCE                                            | 19~21 /35 |

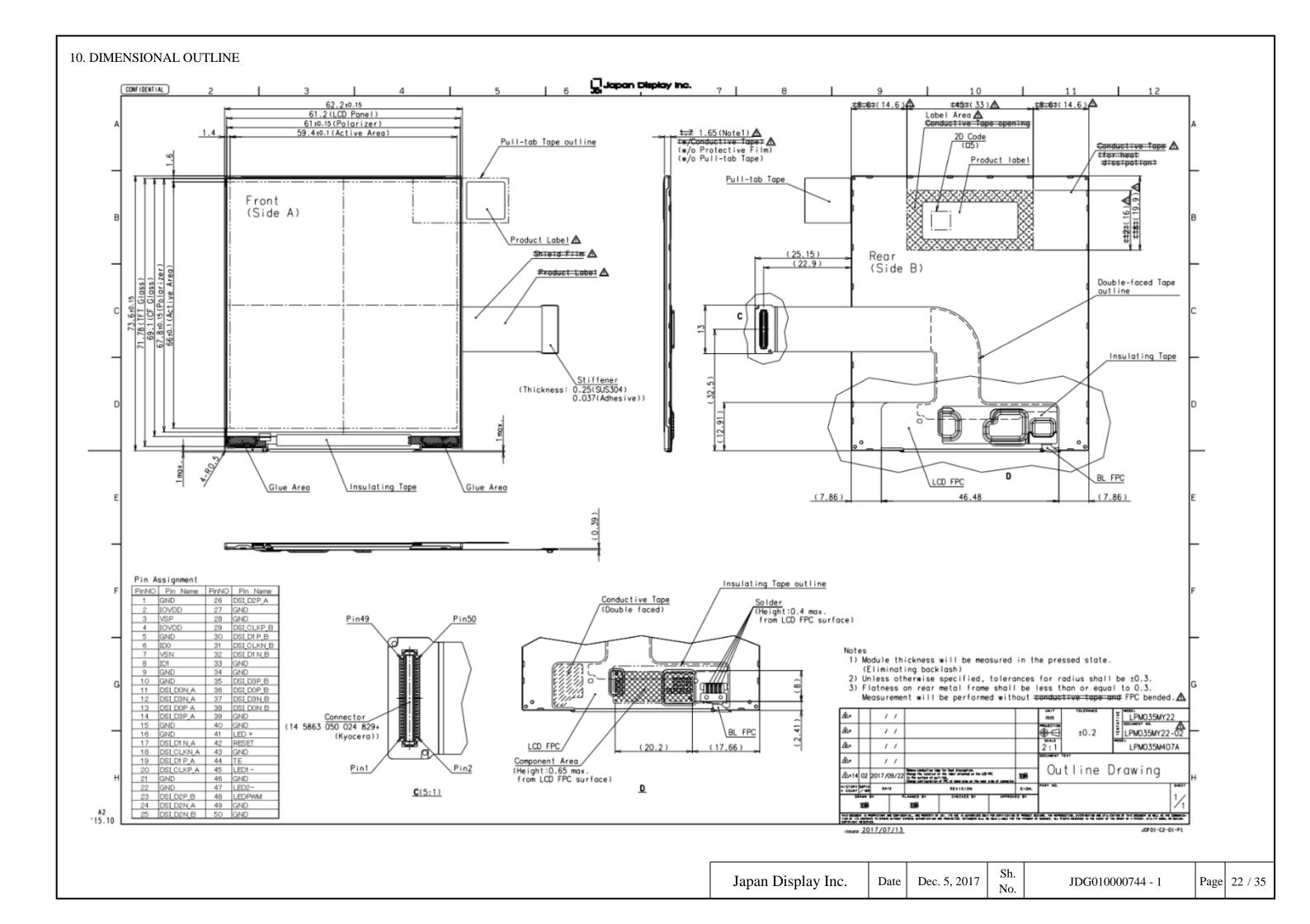

| 10    | DIMENSIONAL OUTLINE (LCD)                           | 22 /35    |

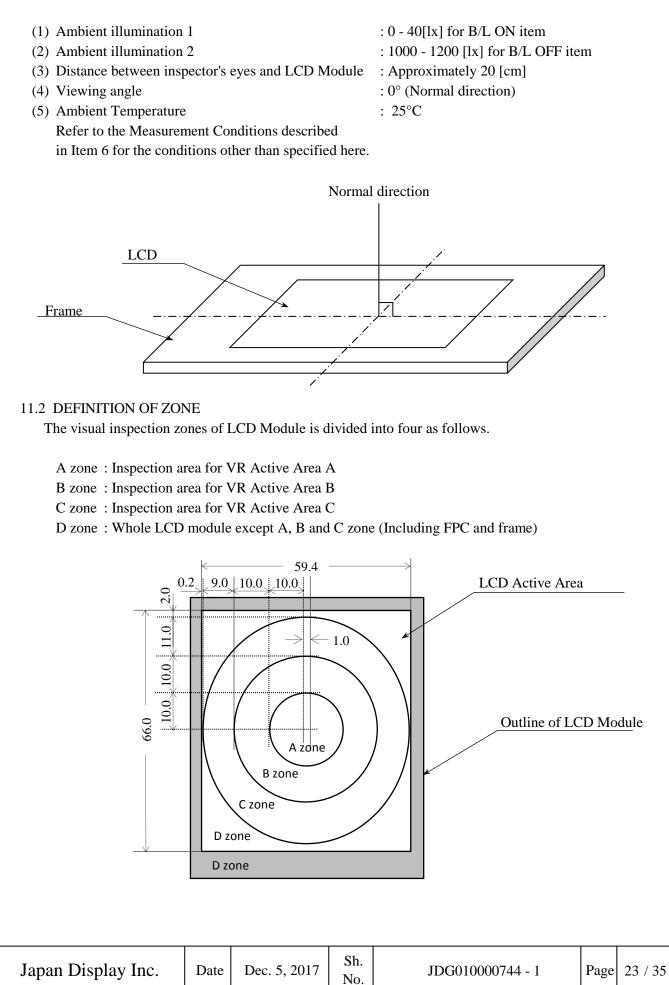

| 11    | VISUAL INSPECTION                                   | 23 /35    |

| 11.1  | INSPECTION CONDITION                                | 23 /35    |

| 11.2  | DEFINITION OF ZONE                                  | 23 /35    |

| 11.3  | COSMETIC SPECIFICATION                              | 24~26 /35 |

| 11.4  | RELIABILITY TEST                                    | 27 /35    |

| 12    | PRECAUTIONS IN DESIGN                               | 28 /35    |

| 12.1  | GENERAL ATTENTION                                   | 28 /35    |

| 12.2  | PRECAUTIONS AGAINST ELECTROSTATIC DISCHARGE         | 28 /35    |

| 12.3  | HANDLING PRECAUTIONS                                | 28~29 /35 |

| 12.4  | OPERATION PRECAUTION                                | 29 /35    |

| 12.5  | STORAGE                                             | 30 /35    |

| 12.6  | SAFETY                                              | 30 /35    |

| 12.7  | MECHANICAL DESIGN                                   | 30 /35    |

| 12.8  | ENVIRONMENTAL PROTECTION                            | 30 /35    |

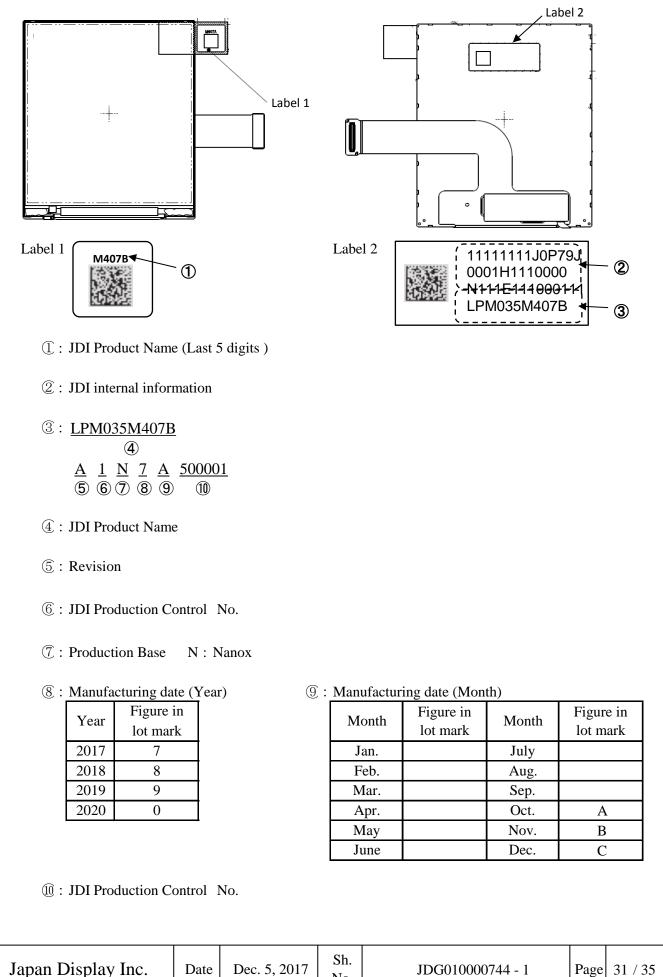

| 13    | LOT MARK                                            | 31 /35    |

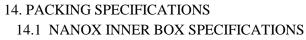

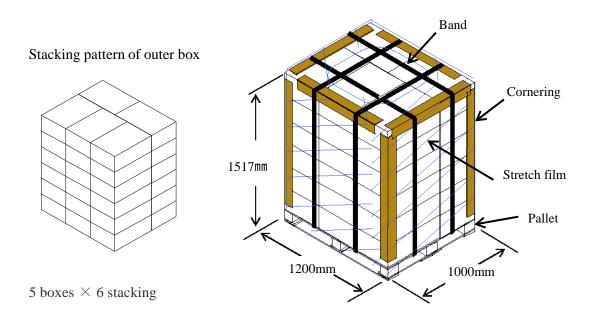

| 14    | PACKING SPECIFICATIONS                              | 32 /35    |

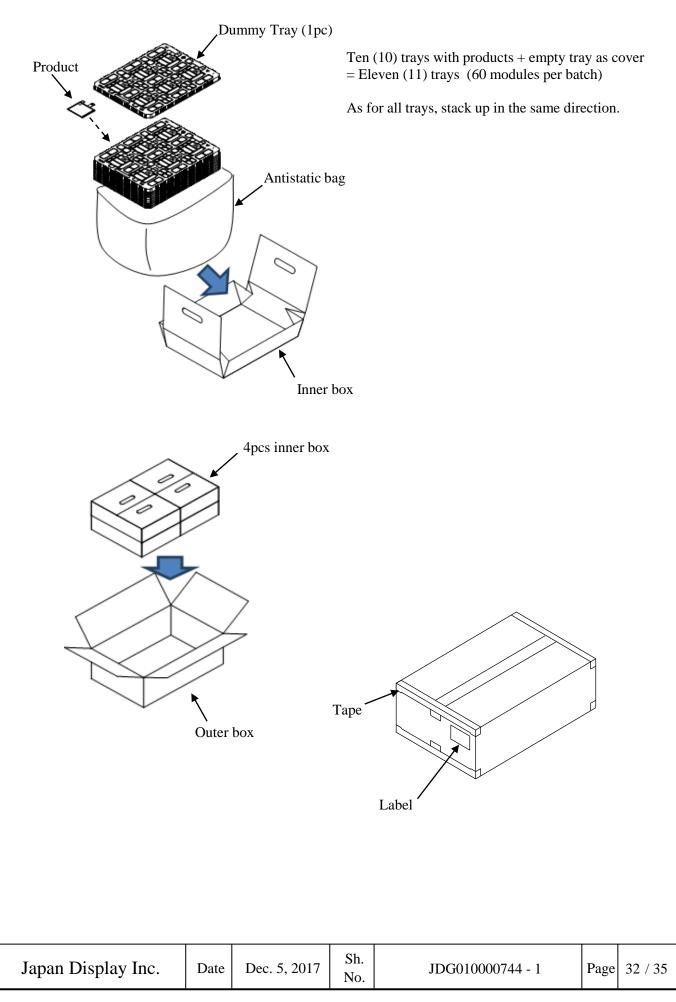

| 14.1  | NANOX INNER BOX SPECIFICATIONS                      | 32~33 /35 |

| 14.2  | PALLET SPECIFICATIONS                               | 34 /35    |

| 14.3  | Label detailed example                              | 34 /35    |

| 15    | PRECAUTIONS FOR USE                                 | 35        |

|       |                                                     |           |

| Ianan | Display Inc. Date Dec. 5, 2017 Sh. JDG010000744 - 1 | Page 2    |

|                    |      | RECORE    | O OF | REVI       | SIONS            |      |        |

|--------------------|------|-----------|------|------------|------------------|------|--------|

| Date Sheet M       | No.  | Page      |      |            | Summary          |      |        |

| Date Sheet N       | No.  | Page      |      |            | Summary          |      |        |

| Japan Display Inc. | Date | Dec. 5, 2 | 2017 | Sh.<br>No. | JDG010000744 - 1 | Page | 3 / 35 |

# 3. GENERAL DATA

| (1) Part Name                           |                                                               | LPM035M407H                                               | 3                                                                                                    |                                                                |         |        |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------|--------|--|--|--|--|

| (2) Module Dimensions                   |                                                               |                                                           | 62.2 (W) mm $\times$ 73.6 (H) mm $\times$ 1.65 (t) mm (Excluding FPC and adhesive on the metal case) |                                                                |         |        |  |  |  |  |

| (3) Active Area Dimensio                | ons                                                           | 59.4 (W) mm $\times$ 66.0 (H) mm                          |                                                                                                      |                                                                |         |        |  |  |  |  |

| (4) Pixel Pitch                         |                                                               | 0.04125 (W) m                                             | $m \times 0.0$                                                                                       | 4125 (H) mm (615ppi)                                           |         |        |  |  |  |  |

| (5) Resolution                          |                                                               | 1440 × 3 (R,G,I                                           | B) (W) :                                                                                             | × 1600 (H) dots                                                |         |        |  |  |  |  |

| (6) Color Pixel Arrangem                | lent                                                          | RGB Vertical S                                            | tripe                                                                                                |                                                                |         |        |  |  |  |  |

| (7) Display Mode                        |                                                               | Transmissive T                                            | ype, No                                                                                              | rmally Black Mode, In-Plane Swite                              | ching N | Aode   |  |  |  |  |

| (8) Number of Colors                    |                                                               | 16,777,216 Col                                            | ors                                                                                                  |                                                                |         |        |  |  |  |  |

| (9) Viewing Direction                   |                                                               | Perpendicular to                                          | o the dis                                                                                            | splay surface                                                  |         |        |  |  |  |  |

| (10) Backlight                          |                                                               | Light Emitting                                            | Diode (                                                                                              | LED), 10 LEDs (2in1) ; 5 series 2                              | strings |        |  |  |  |  |

| (11) Weight                             |                                                               | 17g (typ)                                                 |                                                                                                      |                                                                |         |        |  |  |  |  |

| (12) Power Supply Voltage               | Power Supply Voltage $AVDD = 5.7 + -0.1V AVEE = -5.7 + -0.1V$ |                                                           |                                                                                                      |                                                                |         |        |  |  |  |  |

| (13) Interface I/O power su<br>Note (1) | apply                                                         | VDDI = 1.8V +<br>The same voltag<br>must be supplied to V | ge as "H                                                                                             | I" level of a customer's interface sig                         | gnal    |        |  |  |  |  |

| (14) IC                                 |                                                               | JD36860 (Source and                                       | Power IC                                                                                             | : Novatek)                                                     |         |        |  |  |  |  |

| (15) Interface                          |                                                               | MIPI-DSI Vide                                             | o mode                                                                                               | with data compression (4-Lane x 1                              | -Port)  |        |  |  |  |  |

| (16) Methode of Inversion               |                                                               | Column Inversi                                            | on                                                                                                   |                                                                |         |        |  |  |  |  |

| (17) Surface Treatment                  |                                                               | НС                                                        |                                                                                                      |                                                                |         |        |  |  |  |  |

|                                         |                                                               | -                                                         | •                                                                                                    | ng the I/O signal level of JD36860 ing to a customer's system. |         |        |  |  |  |  |

|                                         |                                                               |                                                           |                                                                                                      |                                                                |         |        |  |  |  |  |

| Japan Display Inc.                      | Date                                                          | Dec. 5, 2017                                              | Sh.<br>No.                                                                                           | JDG010000744 - 1                                               | Page    | 4 / 35 |  |  |  |  |

|                                         |                                                               |                                                           |                                                                                                      |                                                                |         |        |  |  |  |  |

| 5. ABSOLUTE MAXIMUM RATINGS   |                                                |       |          |      |         |  |  |  |  |  |  |

|-------------------------------|------------------------------------------------|-------|----------|------|---------|--|--|--|--|--|--|

| 5.1 ELECTRICAL ABSOLUTE MAXIN | 5.1 ELECTRICAL ABSOLUTE MAXIMUM RATINGS OF LCD |       |          |      |         |  |  |  |  |  |  |

| Item                          | Symbol                                         | Min   | Max      | Unit | Note    |  |  |  |  |  |  |

| Supply voltage                | AVDD                                           | -0.3  | 6.0      | V    | (1)     |  |  |  |  |  |  |

| Supply Voltage                | AVEE                                           | -6.0  | 0.3      | V    | (2)     |  |  |  |  |  |  |

| Logic Input voltage range     | VDDI                                           | -0.3  | 2.0      | V    | (1)     |  |  |  |  |  |  |

| Supply current                | AVDD                                           | 150   | 200      | mA   |         |  |  |  |  |  |  |

| Supply current                | AVEE                                           | 150   | 200      | mA   |         |  |  |  |  |  |  |

| Logic Input current range     | VDDI                                           | 300   | 530      | mA   |         |  |  |  |  |  |  |

| MIPI line voltage range       |                                                | -0.05 | 1.35     | V    | (1)     |  |  |  |  |  |  |

| RESET voltage range           |                                                | -0.3  | VDDI+0.3 | V    | (1)     |  |  |  |  |  |  |

| LED Reverse Voltage           | V <sub>R</sub>                                 | -     | 5        | V    |         |  |  |  |  |  |  |

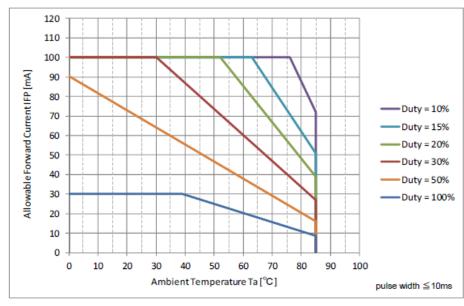

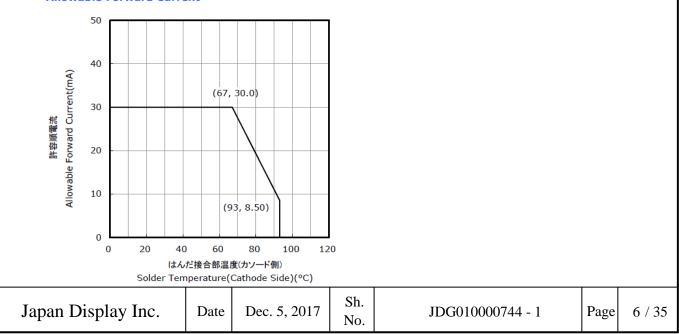

| LED Forward Current           | I <sub>LED</sub>                               | -     | Note (3) | mA   | per LED |  |  |  |  |  |  |

Notes (1) Keep AVDD, VDDI, MIPI line and RESET Voltages no lower than GND.

(2) Keep AVEE Voltages no Higher than GND.

(3) Ambient Temperatures vs. Allowable Forward Current.

|             | Ta [°C] | IFP [mA] |

|-------------|---------|----------|

| Duty = 10%  | 76      | 100      |

| Duty - 10%  | 85      | 72       |

| Duty = 15%  | 63      | 100      |

| Duty - 15%  | 85      | 51       |

| Duty = 20%  | 52      | 100      |

| Duty - 20%  | 85      | 39       |

| Duty = 30%  | 30      | 100      |

| Duty - 30%  | 85      | 27       |

| Duty = 50%  | -11     | 100      |

| Duty - 30%  | 85      | 16       |

| Duty = 100% | 39      | 30       |

| Ducy = 100% | 85      | 8.5      |

In case of "pulse width >10ms", please apply "Duty = 100%". パルス幅が10msを超える場合、Duty = 100%を適用下さい。

| Item                | Oper           | ating    | Non-Operat     | ing (Note3) | Remarks         |  |

|---------------------|----------------|----------|----------------|-------------|-----------------|--|

|                     | Min            | Max      | Min            | Max         |                 |  |

| Ambient Temperature | -10°C          | 55°C     | -20°C          | 70°C        | Note (2)        |  |

| Humidity            | Note           | Note (1) |                | e (1)       | No condensation |  |

| Corrosive Gas       | Not Acceptable |          | Not Acceptable |             |                 |  |

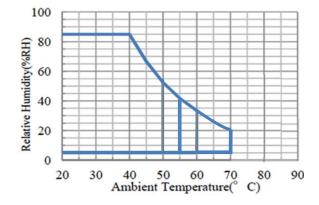

#### °C 85%RH max. Notes (1) I

$Ta > 40^{\circ}C$  Absolute humidity must be lower than the humidity of 85% RH at 40°C.

- (2) Background color slightly changes depending on ambient temperature and viewing angle. The temperature for operating in the table above apply to operation only. Visual qualities, such as contrast ratio and response time, to be evaluated at Ta=25°C Operating.

- (3) This is not for storing condition. When storing LCM for long term, please follow the condition mentioned in "12.5 STORAGE".

| Japan Display Inc. | Date | Dec. 5, 2017 | Sh.<br>No. | JDG010000744 - 1 | Page | 7 / 35 |

|--------------------|------|--------------|------------|------------------|------|--------|

| LCD Module                   |        |            |          |      |          |      | Ta=25°  |

|------------------------------|--------|------------|----------|------|----------|------|---------|

| Item                         | Symbol | Condition  | Min      | Тур  | Max      | Unit | Note    |

| Power Supply Voltage for LCD | VDDI   | -          | 1.7      | 1.8  | 1.9      | V    | -       |

| Power Supply Voltage for     | AVDD   | -          | 5.6      | 5.7  | 5.8      | V    | -       |

| Power Supply Voltage for     | AVEE   | -          | -5.8     | -5.7 | -5.6     | V    | -       |

| Input Voltage for Logic      | VIH    |            | 0.8×VDDI | -    | VDDI     | V    | (1),(2) |

| Circuits                     | VIL    |            | 0        | -    | 0.2×VDDI |      |         |

| Output Voltage for Logic     | VOH1   | IOH=-0.1mA | 0.8×VDDI | -    | -        | V    | (1),(3) |

| Circuits                     | VOL1   | IOL=0.1mA  | -        | -    | 0.2×VDDI |      |         |

| Power Supply Current         | I_VDDI | All White  | -        | 62.8 | 92       | mA   | (4)     |

|                              | I_AVDD | All White  | -        | 10.5 | 18       | mA   | (4)     |

|                              | I_AVEE | All White  | -16      | -9   | -        | mA   | (4)     |

| LED Forward Voltage          | VLED   | -          | -        | 6.14 | 6.44     | V    | (5)     |

| LED Forward Current          | ILED   | -          | -        | 52   | TBD      | mA   | (5)(6)  |

| LED Reverse Current          | IR     | -          | -        | -    | TBD      | μA   |         |

| Frame Frequency              | fFLM   | -          |          | 90   |          | Hz   |         |

Notes (1) VDDI = 1.7V to 1.9V

- (2) Input : RESET

- (3) Output : LEDPWM, TE

- (4) VDDI=1.8V, AVDD=5.7V, AVEE=-5.7V, fFLM=90Hz

- The current is time averaged value even for Maximum criteria.

- (5) Each value is the characteristics of one LED. @If=40mA Duty=10%

- (6) The operating current of LED and the duty ratio should be determined within the maximum rating of the temperature environmental condition.

| Japan Display Inc. | Date | Dec. 5, 2017 | Sh.<br>No. | JDG010000744 - 1 | Page | 8 / 35 |

|--------------------|------|--------------|------------|------------------|------|--------|

|--------------------|------|--------------|------------|------------------|------|--------|

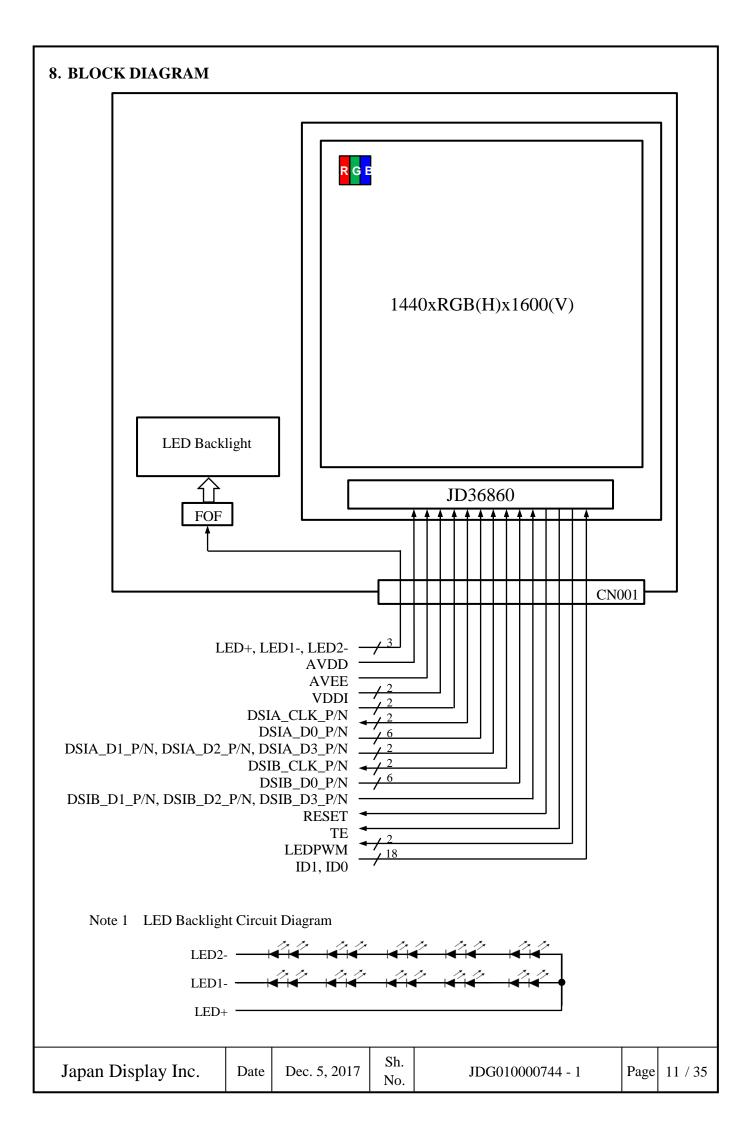

# 7. OPTICAL CHARACTERISTICS

| ICD | (BACKLIGHT ON) |  |

|-----|----------------|--|

| LUD | DACKLIUITI UN) |  |

| LCD (BACKLIGH     | I'ON) |        |              | -     |       |       |                   |             |

|-------------------|-------|--------|--------------|-------|-------|-------|-------------------|-------------|

| Item              |       | Symbol | Condition    | Min   | Тур   | Max   | Unit              | Note        |

| Brightness        |       | В      | φ=0°, θ=0°   | 120   | 150   | -     | cd/m <sup>2</sup> | (1),(2)     |

| Brightness Unifor | mity  | -      | φ=0°, θ=0°   | 75    | 85    | -     | %                 | (2),(3),(5) |

|                   |       |        | φ=60°, θ=0°  | 55    | 60    | -     |                   |             |

| Viewing Angle     |       | CR     | φ=60°, θ=90° | 55    | 60    | -     | -                 | (4),(6),(7) |

|                   |       |        | φ=60°, θ=45° | 55    | 60    | -     |                   |             |

| Contrast Ratio    |       | CR     | φ=0°, θ=0°   | 500   | 700   | -     | -                 | (6)         |

| Response Time     |       | tr+tf  | φ=0°, θ=0°   | 5     |       |       | ms                | (8)         |

|                   | Red   | Х      |              | 0.630 | 0.660 | 0.690 |                   |             |

|                   |       | у      |              | 0.297 | 0.327 | 0.357 |                   |             |

|                   | Green | Х      |              | 0.245 | 0.275 | 0.305 |                   |             |

| Color Tone        |       | у      |              | 0.622 | 0.652 | 0.682 |                   | (0)         |

| (Primary Color)   | Blue  | Х      | φ=0°, θ=0°   | 0.125 | 0.155 | 0.185 | -                 | (9)         |

|                   |       | У      |              | 0.026 | 0.056 | 0.086 |                   |             |

|                   | White | Х      |              | 0.279 | 0.299 | 0.319 |                   |             |

|                   |       | У      |              | 0.295 | 0.315 | 0.335 |                   |             |

| NTSC Ratio        |       | -      |              | 80    | 85    | -     | %                 | -           |

All the criteria shall be applied for initial(delivered) state. (Not for whole the product life.)

Measurement Conditions

| Measurement environment | : Dark room                                  |

|-------------------------|----------------------------------------------|

| Ambient temperature     | : Ta=25°C                                    |

| Sequence                | : Refer to Item 9.4                          |

| Power supply voltage    | : VDDI=1.8V, AVDD=5.7V, AVEE=-5.7V           |

| Backlight current       | : I <sub>LED</sub> =40mA x 2 Strings Duty10% |

Notes (1) Display image for measurement : All White (2) Measurment system;

| Sensor<br>50       | LCD  | Module       |            | r : CS-1000 or equivalent<br>surement point : Center of LCD's ac | ctive a | rea    |

|--------------------|------|--------------|------------|------------------------------------------------------------------|---------|--------|

|                    |      |              |            |                                                                  |         |        |

|                    |      |              |            |                                                                  |         |        |

|                    |      |              |            |                                                                  |         |        |

| Japan Display Inc. | Date | Dec. 5, 2017 | Sh.<br>No. | JDG010000744 - 1                                                 | Page    | 9 / 35 |

# 9. INTERFACE

# 9.1 INTERNAL PIN CONNECTION

| Symbol                 | Pin No.            |    | Description                | Spec.          |

|------------------------|--------------------|----|----------------------------|----------------|

| GND                    | 1,5,9,10,15,16,21, | Р  | Ground                     |                |

|                        | 22,27,28,33,34,39, |    |                            |                |

|                        | 40,43,46,49,50,    |    |                            |                |

|                        | A,B,C,D,E,F,G,H    |    |                            |                |

| AVDD                   | 3                  | Р  | Analog Power Supply        | 5.7+/-0.1V     |

| AVEE                   | 7                  | Р  | Analog Power Supply        | -5.7+/-0.1V    |

| VDDI                   | 2,4                | Р  | Logic and IF Power Supply  | 1.8+/-0.1V     |

| LED+                   | 41                 | Р  | Backlight Anode            |                |

| LED1-                  | 45                 | Р  | Backlight Cathode          |                |

| LED2-                  | 47                 | Р  | Backlight Cathode          |                |

| RESET                  | 42                 | Ι  | Reset fot LCD              | VDDI-GND input |

| TE                     | 44                 | 0  |                            |                |

| LEDPWM                 | 48                 | 0  |                            |                |

| DSI_D0P_A, DSI_D0N_A   | 11,13              | IO | MIPI data lane for Prot A  | <1Gbps         |

| DSI_D1P_A, DSI_D1N_A   | 17,19              | Ι  | MIPI data lane for Prot A  | <1Gbps         |

| DSI_D2P_A, DSI_D2N_A   | 24,26              | Ι  | MIPI data lane for Prot A  | <1Gbps         |

| DSI_D3P_A, DSI_D3N_A   | 12,14              | Ι  | MIPI data lane for Prot A  | <1Gbps         |

| DSI_D0P_B, DSI_D0N_B   | 36,38              | IO | MIPI data lane for Prot B  | <1Gbps         |

| DSI_D1P_B, DSI_D1N_B   | 30,32              | Ι  | MIPI data lane for Prot B  | <1Gbps         |

| DSI_D2P_B, DSI_D2N_B   | 23,25              | Ι  | MIPI data lane for Prot B  | <1Gbps         |

| DSI_D3P_B, DSI_D3N_B   | 35,37              | Ι  | MIPI data lane for Prot B  | <1Gbps         |

| DSI_CLKP_A, DSI_CLKN_A | 18,20              | Ι  | MIPI clock lane for Prot A | <1Gbps         |

| DSI_CLKP_B, DSI_CLKN_B | 29,31              | Ι  | MIPI clock lane for Prot B | <1Gbps         |

| ID1, ID0               | 6,8                | 0  | ID(Ground)                 |                |

# KYOCERA Connector producuts Corporation 14 5863 050 024 829+ BtoB(Plug) CN001 50pin

| I          |     | I      | I     |     | Ι     | Ι   |           | Ι         | I   | Ι          | I          | Ι   | Ι         | I         | Ι   | Ι          | Ι          |     | Ι         | Ι         | I   | Ι     | I   | Ι    | 1    | I    |           |

|------------|-----|--------|-------|-----|-------|-----|-----------|-----------|-----|------------|------------|-----|-----------|-----------|-----|------------|------------|-----|-----------|-----------|-----|-------|-----|------|------|------|-----------|

| L D        | 50  | 48     | 46    | 44  | 42    | 40  | 38        | 36        | 34  | 32         | 30         | 28  | 26        | 24        | 22  | 20         | 18         | 16  | 14        | 12        | 10  | 8     | 9   | 4    | 2    | ⊥ ≀  | C<br>C    |

| <u>н</u> + | GND | LEDPWM | GND   | TE  | RESET | GND | DSI_D0N_B | B_900_ISU | GND | DSI_D1N_B  | DSI_D1P_B  | GND | A_92D_ISU | DSI_D2N_A | GND | DSI_CLKP_A | DSI_CLKN_A | GND | DSI_D3P_A | DSI_D3N_A | GND | ID1   | ID0 | IQQV | IQQV |      | 0         |

| <u> </u>   | GND | LED2-  | LED1- | GND | LED+  | GND | DSI_D3N_B | DSI_D3P_B | GND | DSI_CLKN_B | DSI_CLKP_B | GND | DSI_D2N_B | DSI_D2P_B | GND | DSI_D1P_A  | DSI_D1N_A  | GND | DSI_D0P_A | DSI_D0N_A | GND | A VEE | GND | AVDD | GND  |      | л         |

| e –        | 49  | 47     | 45    | 43  | 41    | 39  | 37        | 35        | 33  | 31         | 29         | 27  | 25        | 23        | 21  | 19         | 17         | 15  | 13        | 11        | 9   | 7     | 5   | 3    | 1    |      | A         |

| I          |     | Ι      |       |     | Ι     |     |           |           |     |            |            | Ι   |           |           | Ι   |            | Ι          |     | Ι         | Ι         | Ι   | Ι     | Ι   | Ι    |      | 1    |           |

| Japan      | Dis | pla    | y I   | nc. |       |     | Date      | e         | De  | ec. 5      | 5, 20      | 017 |           | Sh<br>No  |     |            |            | JD  | G0        | 100       | 007 | 744   | - 1 |      |      | Page | 2 12 / 35 |

|            |     |        |       |     |       |     |           |           |     |            |            |     |           |           |     |            |            |     |           |           |     |       |     |      |      |      |           |

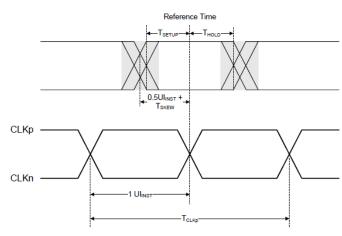

#### 9.2 TIMING CHARACTERISTICS ~ ~ ~

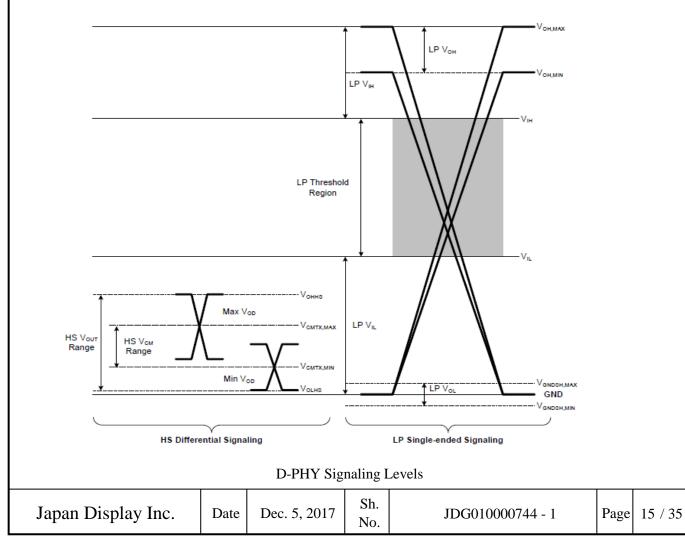

| (1)M   | PI DSI Characteristics                    |           |      |                 |     |     |     |      |

|--------|-------------------------------------------|-----------|------|-----------------|-----|-----|-----|------|

|        | Item                                      | Symbol    | Unit | Condition       | Min | Тур | Max | Note |

|        | Differential input<br>high threshold      | VIDTH     | mV   | VDDI=1.65~1.95V | -   | -   | 70  |      |

|        | Differential input<br>low threshold       | VIDTL     | mV   | VDDI=1.65~1.95V | -70 | -   | -   |      |

| HS-RX  | Single-ended input low voltage            | VILHS     | mV   | VDDI=1.65~1.95V | -40 | -   | -   |      |

| 115-КЛ | Single-ended input high voltage           | VIHHS     | mV   | VDDI=1.65~1.95V | -   | -   | 460 |      |

|        | Common-mode voltage<br>HS receive mode    | VCMRX(DC) | mV   | VDDI=1.65~1.95V | 70  | -   | 330 |      |

|        | Differential input<br>impedance           | ZID       | Ω    | VDDI=1.65~1.95V | 80  | 100 | 125 |      |

| LP-RX  | Logic 0 input voltage<br>not in ULP State | VIL       | mV   | VDDI=1.65~1.95V | -   | -   | 550 |      |

|        | Logic 1 input voltage                     | VIH       | mV   | VDDI=1.65~1.95V | 880 | -   | -   |      |

|        | Thevenin output<br>low level              | VOL       | mV   | VDDI=1.65~1.95V | -50 | -   | 50  |      |

| LP-TX  | Thevenin output<br>high level             | VOH       | V    | VDDI=1.65~1.95V | 1.1 | 1.2 | 1.3 |      |

|        | Output impedance of LP transmitter        | ZOLP      | Ω    | VDDI=1.65~1.95V | 80  | 100 | 125 |      |

| CD-RX  | Logic 0<br>contention threshold           | VILCD     | mV   | VDDI=1.65~1.95V | -   | -   | 200 |      |

|        | Logic 1<br>contention threshold           | VIHCD     | mV   | VDDI=1.65~1.95V | 450 | -   | -   |      |

| Japan Display Inc. | Date | Dec. 5, 2017 | Sh.<br>No. | JDG010000744 - 1 | Page | 13 / 35 |

|--------------------|------|--------------|------------|------------------|------|---------|

|--------------------|------|--------------|------------|------------------|------|---------|

| MIPI DSI HS-RX Clock and Da                        | ta-Clock Specifi                | cations            |                 |       |     |      |         |

|----------------------------------------------------|---------------------------------|--------------------|-----------------|-------|-----|------|---------|

| Item                                               | Symbol                          | Unit               | Condition       | Min   | Тур | Max  | Note    |

| UI instantaneous                                   | UI <sub>INST</sub>              | ns                 | VDDI=1.65~1.95V | 1     | -   | 4    | 1, 2, 7 |

| Data to Clock Skew<br>[measured at transmitter]    | T <sub>SKEW</sub> [TX]          | UI <sub>INST</sub> | VDDI=1.65~1.95V | -0.15 | -   | 0.15 | 3       |

| Data to Clock Setup Time<br>[measured at receiver] | T <sub>SETUP</sub> [RX]         | UI <sub>INST</sub> | VDDI=1.65~1.95V | 0.15  | -   | 0.15 | 4       |

| Data to Clock Hold Time<br>[measured at receiver]  | T <sub>HOLD</sub> [RX]          | UI <sub>INST</sub> | VDDI=1.65~1.95V | 0.15  | I   | 0.15 | 4       |

| 20% - 80% rise time                                | t <sub>R</sub> / t <sub>F</sub> | ps                 | VDDI=1.65~1.95V | 150   | -   | -    | 6       |

| and fall time                                      | ι <sub>R</sub> / ι <sub>F</sub> | UI <sub>INST</sub> | VDDI=1.65~1.95V | -     | -   | 0.3  | 5       |

Notes 1. This value corresponds to a minimum 250 Mbps data rate.

2. The minimum UI shall not be violated for any single bit period, i.e., any DDR half cycle within a data burst.

3. Total silicon and package delay budget of  $0.3^*$  UIINST when D-PHY is supporting maximum data rate = 1Gbps.

4. Total setup and hole window for receiver of  $0.3^*$  UIINST when D-PHY is supporting maximum data rate = 1Gbps.

5. Applicable when operating at HS bit rates  $\leq 1$  Gbps (UI  $\geq 1$  ns).

6. Applicable for all HS bit rates. However, to avoid excessive radiation, bit rates  $\leq 1$  Gbps (UI  $\geq 1$  ns), should not use values below 150 ps.

7. For MIPI speed limitation:

[1] Per lane bandwidth is 1Gbps,

[2] Total Bit Rate: 4Gbps for 8-8-8; 2.67 Gbps for 6-6-6; and for5-6-5.

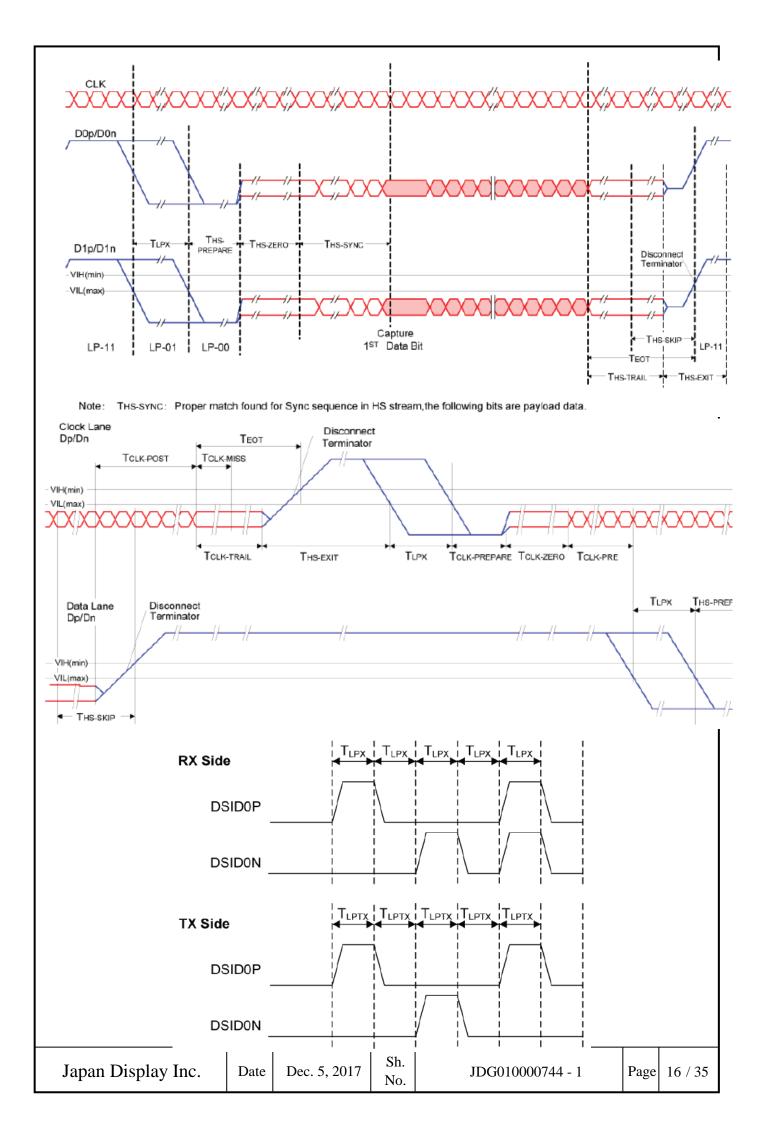

| Item                                                                                                                               | Symbol                  | Unit | Condition       | Min                 | Тур                | Max                 | Note     |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----------------|---------------------|--------------------|---------------------|----------|

| Time to drive LP-00 to prepare<br>for HS transmission                                                                              | T <sub>HS-PREPARE</sub> |      | VDDI=1.65~1.95V | 40ns<br>+4*UI       | -                  | 85ns<br>+6*UI       |          |

| Time to drive flipped differential<br>state after last payload data bit of<br>a HS transmission burst                              | T <sub>HS-TRAIL</sub>   |      | VDDI=1.65~1.95V | 60ns +<br>4*UI      | -                  | -                   |          |

| Time to drive LP-11<br>after HS burst                                                                                              | T <sub>HS-EXIT</sub>    | ns   | VDDI=1.65~1.95V | 100                 | -                  | -                   |          |

| Time to drive LP-00<br>after Turnaround Request                                                                                    | T <sub>TA-GO</sub>      |      | VDDI=1.65~1.95V |                     | 4*T <sub>LPX</sub> |                     |          |

| Time-out before new TX side starts driving                                                                                         | T <sub>TA-SURE</sub>    |      | VDDI=1.65~1.95V | 1*T <sub>LPTX</sub> | -                  | 2*T <sub>LPTX</sub> |          |

| Time to drive LP-00 by new TX                                                                                                      | T <sub>TA-GET</sub>     |      | VDDI=1.65~1.95V |                     | 5*T <sub>LPX</sub> |                     |          |

| Length of any Low-Power state<br>period                                                                                            | TLPTX                   | ns   | VDDI=1.65~1.95V | 50                  | -                  | -                   |          |

| Ratio of $T_{LPX(MASTER)}/T_{LPX(SLAVE)}$<br>between Master and Slave side                                                         | Ratio T <sub>LPX</sub>  |      | VDDI=1.65~1.95V | 2/3                 | -                  | 3/2                 |          |

| Time that the transmitter shall<br>continue sending HS clock after<br>the last associated Data Lane<br>has transitioned to LP mode | T <sub>CLK-POST</sub>   |      | VDDI=1.65~1.95V | 60ns<br>+52UI       | -                  | -                   |          |

| T <sub>CLK-PREPARE</sub> + Time for lead HS-0<br>drive period before starting Clock                                                |                         | ns   | VDDI=1.65~1.95V | 300                 | -                  | -                   |          |

| Japan Display Inc.                                                                                                                 | Date Dec. 5, 2          | 2017 | Sh.<br>No. JDG  | 01000074            | 44 - 1             | Pag                 | e 14 / 3 |

#### MIPI DSI LP-RX/TX Clock and Data-Clock Specifications

| Item                                                                                               | Symbol                   | Unit | Condition                   | Min | Тур | Max              | Note |

|----------------------------------------------------------------------------------------------------|--------------------------|------|-----------------------------|-----|-----|------------------|------|

| Time that the HS clock shall be driven prior to any associated                                     |                          |      | VDDI=DPHYVCC                | 0   |     |                  |      |

| Data Lane beginning the transition<br>from LP to HS mode                                           | T <sub>CLK-PRE</sub>     | UI   | =1.65~1.95V                 | 8   | -   | -                |      |

| Time to drive LP-00 to prepare<br>for HS clock transmission                                        | T <sub>CLK-PREPARE</sub> | ns   | VDDI=DPHYVCC<br>=1.65~1.95V | 38  | -   | 95               |      |

| Time to drive HS differential state<br>after last payload clock bit<br>of an HS transmission burst | T <sub>CLK-TRAIL</sub>   | ns   | VDDI=DPHYVCC<br>=1.65~1.95V | 60  | -   | -                |      |

| Time from start of THS-TRAIL period to start of LP-11 state                                        | T <sub>EOT</sub>         |      | VDDI=DPHYVCC<br>=1.65~1.95V | -   | -   | 105ns +<br>12*UI |      |

# Data to Clock Timing Definitions

# Video timing for non-compression mode MIPI Video Mode Timing Compression intrface 4-lane x 1-port

|                        | min   | typ  | max  | unit      |

|------------------------|-------|------|------|-----------|

| MIPIDSI                |       |      | 1000 | Mbps/lane |

| Frame Rate (Host side) |       |      | 90   | Hz        |

| Vertical Front Porch   |       | 150  |      | Lines     |

| Vertical Back Porch    |       | 150  |      | Lines     |

| Active line per frame  |       | 1600 |      | Lines     |

| Line Time              | 5.85  |      |      | us        |

| Horizontal back porch  | 0.16  |      |      | us        |

| Horizontal front porch | 0.416 |      |      | us        |

| Japan Display Inc. Data Dec 5 2017 Sh. IDC010000744 1 Page 17     |                    |      |              |                  |      |         |

|-------------------------------------------------------------------|--------------------|------|--------------|------------------|------|---------|

| Japan Display Inc. Date Dec. 5, 2017 No. JD0010000744 - 1 Page 17 | Japan Display Inc. | Date | Dec. 5, 2017 | JDG010000744 - 1 | Page | 17 / 35 |

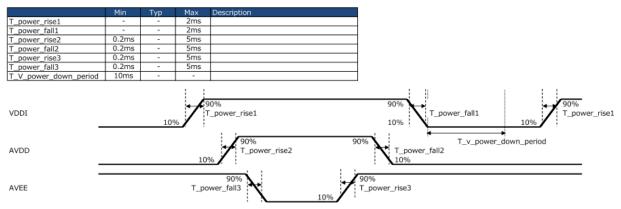

#### 9.3 POWER ON/OFF SEQUENCE

#### 1. Supply Power Voltage

|      | Min  | Тур  | Max  | Description                          |

|------|------|------|------|--------------------------------------|

| AVDD | 5.6  | 5.7  | 5.8  | Analog power supply for LCD.         |

| AVEE | -5.8 | -5.7 | -5.6 | Analog power supply for LCD.         |

| VDDI | 1.7  | 1.8  | 1.9  | Digital power supply for LCD and TP. |

#### 2. Supply Power Slew rate

#### 3. Power On sequence

| LCD Display Status      | Power ON | Sleep-in Mode               | Sleep-in Mode   | Sleep out sequence | Display ON     |

|-------------------------|----------|-----------------------------|-----------------|--------------------|----------------|

| VDDI                    | >1ms     |                             |                 |                    |                |

| AVDD                    | >1ms     | >10ms >10us >10us >10us >10 | >0mc            |                    |                |

| AVEE                    | <u> </u> |                             | *               |                    |                |

| RESET(RESX)             |          | #1 #2                       | Note2           | User wait time     |                |

| LCD Command             |          | LP 11 state (MIPI)          | Initial setting |                    | ≥40ms BL<br>ON |

| MIPI video stream Packe | t        | Note3                       |                 |                    |                |

| Back Light Control      |          |                             |                 |                    | BL ON          |

| TE(Vsync)               |          |                             |                 |                    |                |

#### 4. Power Off sequence

| LCD Display Status      | Dispaly ON                      | Sleep-in Mode | Power OFF     |

|-------------------------|---------------------------------|---------------|---------------|

| VDDI                    |                                 |               | >1ms          |

| AVDD                    | >0ms                            | >60ms         | ↔             |

| AVEE                    | >UIIIS                          | >00000 ►      | >1ms          |

| RESET(RESX)             |                                 |               | >0ms<br>Note4 |

| LCD Command             | BL >0ms Display Sleep<br>OFF In |               | NOLE4         |

| MIPI video stream Packe |                                 |               |               |

| Back Light Control      | BL ON                           |               |               |

| TE(Vsync)               |                                 |               |               |

Note 1: The **RESET** waveform #1(rise-fall-rise) is better thean #2(one rise)

Note 2: After Sleep-Out command, Driver IC will reload MTP registers and do internal power on action. Therefore, any initial setting by MIPI should be set

after Sleep-Out command with minimum delay time 100ms.

Note 3: When use MIPI lanes must go to LP11 state during power-on and RESET sequence

| Japan Display Inc. | Date | Dec. 5, 2017 | Sh.<br>No. | JDG010000744 - 1 | Page | 18 / 35 |

|--------------------|------|--------------|------------|------------------|------|---------|

|--------------------|------|--------------|------------|------------------|------|---------|

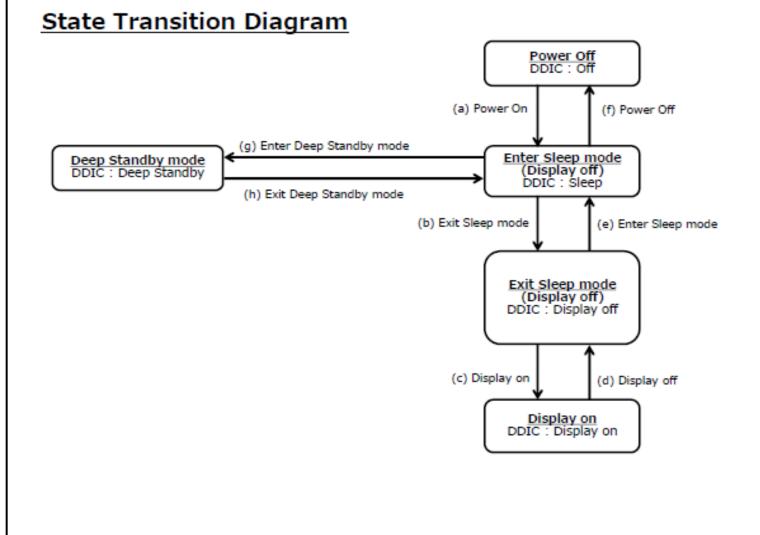

### 9.4 SEQUENCE

Power On Sequence

#### (a) Power On Sequence

| Step | Action/Command   |

|------|------------------|

| 1    | Reset="L"        |

| 2    | VDDI On          |

| 3    | Wait 1ms (min.)  |

| 4    | AVDD On          |

| 5    | Wait 1ms (min.)  |

| 6    | AVEE On          |

| 7    | Wait 10ms (min.) |

| 8    | Reset="H"        |

| 9    | Wait 10us (min.) |

| 10   | Reset="L"        |

| 11   | Wait 10us (min.) |

| 12   | Reset="H"        |

|      | Wait 10ms (min.) |

State transition diagram

| Sh.<br>No. | JDG010000744 - 1 | Page | 19 / 35 |

|------------|------------------|------|---------|

# 9.4 SEQUENCE

Initial setting & exit sleep mode sequence for non-compression mode

# (b) Exit Sleep mode Sequence (Initial setting & Exit Sleep mode) For mipi video mode

| Step | Action/Command         | DSI D | )ata | Addres | Data          | I2C Address | Param | Param | Param |                                           |

|------|------------------------|-------|------|--------|---------------|-------------|-------|-------|-------|-------------------------------------------|

|      |                        | Тур   | e    | s      |               | (TP)        | 1     | 2     | 3     |                                           |

| 1    | Page select            | DCS   | 15   | 0xFF   | 0x10          |             |       |       |       |                                           |

| 2    | Reload                 | DCS   | 15   | 0xFB   | 0x01          |             |       |       |       |                                           |

| 3    | SET_HORIZONTAL_ADDRESS | DCS   | 39   | 0x2A   | 0x00          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x00          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x05          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x9F          |             |       |       |       |                                           |

| 4    | SET_VERTICAL_ADDRESS   | DCS   | 39   | 0x2B   | 0x00          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x00          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x06          |             |       |       |       | 1600                                      |

|      |                        |       |      |        | 0x3F          |             |       |       |       |                                           |

|      | SET_TEAR_ON            | DCS   | 15   | 0x35   | 0x00          |             |       |       |       |                                           |

|      | SET_MIPI_LANE          | DCS   | 15   | 0xBA   | 0x07          |             |       |       |       | 4-lane x 1-port                           |

| 7    | SETDSIMODE             | DCS   | 15   | 0xBB   | 0x <b>1</b> 3 |             |       |       |       | 03: Video Mode bypass RAM, 10: Command Mo |

|      | BK_EN                  | DCS   | 15   | 0xE5   | 0x00          |             |       |       |       | Random 00h, Black 01h                     |

|      | Page select            | DCS   | 15   | 0xFF   | 0x26          |             |       |       |       | PWM adjustment for JDI recommended video  |

| 10   | Reload                 | DCS   | 15   | 0xFB   | 0x01          |             |       |       |       |                                           |

|      | DELY_VID               | DCS   | 15   | 0x02   | 0xC0          |             |       |       |       |                                           |

|      | DELY_VID               | DCS   | 15   | 0x03   | 0x00          |             |       |       |       |                                           |

|      | Page select            | DCS   | 15   | 0xFF   | 0x25          |             |       |       |       |                                           |

| 14   | Reload                 | DCS   | 15   | 0xFB   | 0x01          |             |       |       |       |                                           |

| 15   | PIN CTRL3              | DCS   | 15   | 0x62   | 0x60          |             |       |       |       |                                           |

| 16   | VSOUTS_1               | DCS   | 15   | 0x65   | 0x00          |             |       |       |       |                                           |

| 17   | VSOUTS_2               | DCS   | 15   | 0x66   | 0x07          |             |       |       |       |                                           |

| 18   | VSOUTW                 | DCS   | 15   | 0x67   | 0x56          |             |       |       |       | 10% duty                                  |

|      | Page select            | DCS   | 15   | 0xFF   | 0xD0          |             |       |       |       |                                           |

|      | Reload                 | DCS   | 15   | 0xFB   | 0x01          |             |       |       |       |                                           |

|      | Adjustment of timing   | DCS   | 15   | 0x05   | 0x88          |             |       |       |       |                                           |

|      | Page select            | DCS   | 15   | 0xFF   | 0x10          |             |       |       |       |                                           |

|      | Reload                 | DCS   | 15   | 0xFB   | 0x01          |             |       |       |       |                                           |

|      | Compression            | DCS   | 15   | 0xC0   | 0x83          |             |       |       |       | VESA DSC High Frame Rate Mode enable      |

| 25   | RGBMIPICTRL_HF         | DCS   | 39   | 0xBE   | 0x01          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x90          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x0F          |             |       |       |       |                                           |

|      |                        |       |      |        | 0x39          |             |       |       |       |                                           |

|      | exit_sleep_mode        | DCS   | 05   | 0x11   | -             |             |       |       |       |                                           |

| 27   | Wait 100ms (min.)      |       |      |        |               |             |       |       |       |                                           |

No.

# Note Mode, 13: Video Mode with RAM o timing Sh. JDG010000744 - 1 Page 20 / 35

#### (c) Display on Sequence

| - [ | Step | Action/Command    | DSI Data |    | Addres | Data | I2C Address | Param | Param | Param | Note |

|-----|------|-------------------|----------|----|--------|------|-------------|-------|-------|-------|------|

|     |      |                   | Тур      | e  | S      |      | (TP)        | 1     | 2     | 3     |      |

| Γ   | 1    | SET_DISPLAY_ON    | DCS      | 05 | 0x29   |      |             |       |       |       |      |

|     | 2    | Video Image Start |          |    |        |      |             |       |       |       |      |

|     | 3    | Wait 40ms (min.)  |          |    |        |      |             |       |       |       |      |

#### (d)Display off Sequence

| • | Step | Action/Command  | DSI Data<br>Type |    |      |  | I2C Address<br>(TP) | Param<br>1 | Param<br>2 | Param<br>3 | Note |

|---|------|-----------------|------------------|----|------|--|---------------------|------------|------------|------------|------|

|   | 1    | SET_DISPLAY_OFF | DCS              | 05 | 0x28 |  |                     | -          | -          |            |      |

#### (e) Enter Sleep mode Sequence

| - [ | Step | Action/Command   | DSI Data 🛛 🖌 |    | Addres | Data | I2C Address | Param | Param | Param | Note |

|-----|------|------------------|--------------|----|--------|------|-------------|-------|-------|-------|------|

|     |      |                  | Тур          | e  | S      |      | (TP)        | 1     | 2     | 3     |      |

| Γ   | 1    | SET_TEAR_OFF     | DCS          | 05 | 0x34   |      |             |       |       |       |      |

| - [ | 2    | ENTER_SLEEP_MODE | DCS          | 05 | 0x10   |      |             |       |       |       |      |

#### (f) Power Off Sequence

| Step | Action/Command | DSI Data | Addres | Data | I2C Address | Param | Param | Param | Note |

|------|----------------|----------|--------|------|-------------|-------|-------|-------|------|

|      |                | Туре     | s      |      | (TP)        | 1     | 2     | 3     |      |

| 1    | Reset="L"      |          |        |      |             |       |       |       |      |

| 2    | Wait 1ms(min.) |          |        |      |             |       |       |       |      |

| 3    | AVEE Off       |          |        |      |             |       |       |       |      |

| 4    | Wait 1ms(min.) |          |        |      |             |       |       |       |      |

| 5    | AVDD Off       |          |        |      |             |       |       |       |      |

| 6    | Wait 1ms(min.) |          |        |      |             |       |       |       |      |

| 7    | VDDI Off       |          |        |      |             |       |       |       |      |

|      |                |          |        |      |             |       |       |       |      |

#### (g) Enter Deep Standby mode Sequence

| Step | Action/Command  | DSI D | ata | Addres | Data | I2C Address | Param | Param | Param | Note                                                                                                                                                                                                                                                  |

|------|-----------------|-------|-----|--------|------|-------------|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                 | Тур   | e   | s      |      | (TP)        | 1     | 2     | 3     |                                                                                                                                                                                                                                                       |

| 1    | ENTER_DSTB_MODE | DCS   | 15  | 0x4F   | 0x01 |             |       |       |       |                                                                                                                                                                                                                                                       |

| 2    | Enter ULPM      |       |     |        |      |             |       |       |       | All Mipi lanes should be VSS with specified sequence in Mi<br>• Start: LP-11<br>• Escape Mode Entry (EME): LP-11 =>LP-10 =>LP-00 =><br>• Ultra-Low Power State (ULPS) command in Escape Mod<br>• Ultra-Low Power State (ULPS) when the MCU is keeping |

# (h) Exit Deep Standby mode Sequence(1)

| Step | Action/Command   | DSI D | ata      | Addres | Data | I2C Address | Param | Param | Param | Note                                                        |

|------|------------------|-------|----------|--------|------|-------------|-------|-------|-------|-------------------------------------------------------------|

|      |                  | Тур   | e        | s      |      | (TP)        | 1     | 2     | 3     |                                                             |

| 1    | Reset="L"        |       |          |        |      |             |       |       |       |                                                             |

| 2    | Wait 3ms (min.)  |       |          |        |      |             |       |       |       |                                                             |

| 3    | Exit ULPM        |       |          |        |      |             |       |       |       | All Mipi laes should be 1.2V with specified sequence in MIF |

|      |                  |       |          |        |      |             |       |       |       | • Mark-1: LP-00 =>LP-10 =>LP-11                             |

|      |                  |       |          |        |      |             |       |       |       |                                                             |

|      | Weit town (win ) |       | <u> </u> |        |      |             |       |       |       |                                                             |

| 4    | Wait 10ms (min.) |       |          |        |      |             |       |       |       |                                                             |

|   |           |                                                    | ]    |         |  |

|---|-----------|----------------------------------------------------|------|---------|--|

|   |           |                                                    |      |         |  |

|   |           |                                                    |      |         |  |

|   |           |                                                    |      |         |  |

|   |           |                                                    |      |         |  |

|   |           |                                                    | -    |         |  |

|   |           |                                                    |      |         |  |

|   |           |                                                    | ]    |         |  |

|   |           | as below.                                          |      |         |  |

| ¢ | ode: 000  | =>LP-00<br>1 1110 (First to Last bit)<br>lanes low |      |         |  |

|   |           |                                                    | ]    |         |  |

|   |           |                                                    | -    |         |  |

| ~ | 1IPI like | as below.                                          |      |         |  |

|   |           |                                                    |      |         |  |

|   |           |                                                    |      |         |  |

|   |           |                                                    |      |         |  |

|   | Sh.       |                                                    | D    |         |  |

| I | No.       | JDG010000744 - 1                                   | Page | 21 / 35 |  |

### **11. VISUAL INSPECTION**

#### 11.1 INSPECTION CONDITION

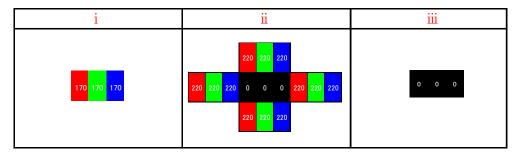

## 11.3 COSMETIC SPECIFICATION

# 11.3.1 Screen Defects Specification for LCD Module

| 11.3.1 Screen Defects Specification for LCD Module |                                                    |                                                                                                           |                                                                                                                |                    |                 |      |              |               |               |                  |

|----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------|-----------------|------|--------------|---------------|---------------|------------------|

| No.                                                | Item                                               |                                                                                                           |                                                                                                                |                    | num<br>e Number | Unit | Applied zone | LCD<br>module | Back<br>light | Note             |

| Brig                                               | ght Defect                                         |                                                                                                           |                                                                                                                | Igno               | red             | PC   | D            |               |               |                  |

| Fore                                               | smaller than the Dum                               |                                                                                                           | nite Dot of Limit                                                                                              | 0                  |                 | PC   | A, B, C      |               |               |                  |

| 1 Bub                                              |                                                    |                                                                                                           | Defect size is equal to or<br>smaller than the Dummy<br>White Dot of Limit Pattern,<br>check the brightness    |                    |                 | -    | -            | Or            | 1             | (1), (2),<br>(3) |

|                                                    |                                                    | than B<br>Limit I<br>(R,G,F                                                                               | ness is Darker<br>right Defect<br>Pattern<br>3,W)                                                              | Igno               |                 | PC   | A, B, C      |               |               | (3)              |

|                                                    |                                                    |                                                                                                           | ness is equal to                                                                                               | 0                  |                 | PC   | Α            |               |               |                  |

|                                                    |                                                    |                                                                                                           | ghter than Bright<br>Limit Pattern                                                                             | 1                  |                 | PC   | В            |               |               |                  |

|                                                    |                                                    | (R,G,E                                                                                                    |                                                                                                                | 2                  |                 | PC   | С            |               |               |                  |

| Darl                                               | k Defect                                           |                                                                                                           |                                                                                                                | Igno               | red             | PC   | D            |               |               |                  |

| Fore<br>Stai                                       | rk Dot, Dark<br>eign Particles,<br>n, Scratch, Air |                                                                                                           | is larger than the<br>rk Dot of Limit                                                                          | 0                  | I               | PC   | A, B, C      |               |               | (3), (4)         |

| D:A                                                | Bubble)<br>D:Average diameter<br>[mm]              | smaller tha<br>Dark Dot (<br>(L)                                                                          | is equal to or<br>a the Dummy<br>f Limit Pattern                                                               | 2                  |                 | PC   | С            | k             | (             |                  |

|                                                    |                                                    | Defect<br>than th                                                                                         | size is larger<br>ne Dummy Dark<br>Limit Pattern (S)                                                           | 0                  |                 | PC   | В            |               |               |                  |

|                                                    |                                                    | or sma<br>Dumm                                                                                            | size is equal to<br>ller than the<br>y Dark Dot of<br>Pattern (S)                                              | -                  |                 | -    | -            |               |               |                  |

|                                                    |                                                    | Brig<br>than<br>Patte                                                                                     | Brightness is Brighter<br>than Dark Defect Limit<br>Pattern                                                    |                    | red             | PC   | A,B          |               |               |                  |

|                                                    |                                                    |                                                                                                           | htness is equal to arker than Dark                                                                             | 0                  |                 | PC   | A            |               |               |                  |

|                                                    |                                                    |                                                                                                           | ect Limit Pattern                                                                                              | 2                  |                 | PC   | В            |               |               |                  |

| Tota                                               | al number = Brigh                                  | t defect +                                                                                                | dark defect                                                                                                    | N<=4 , D           | S>=4mm          | PC   | A,B,C        | Or            | 1             | -                |

|                                                    | e Defect                                           |                                                                                                           |                                                                                                                | 0                  |                 | PC   | A, B, C      | Or            | 1             | -                |

| Une                                                | ven Brightness (L                                  | inear)                                                                                                    |                                                                                                                | Serious            | one is          |      |              | 0             |               |                  |

| Une                                                | even Brightness (C                                 | Circular)                                                                                                 |                                                                                                                | not all            | owed            | -    | A, B, C      | Or            | 1             | (6)              |

| Scra                                               | atch of Polarizer                                  | W -0.05                                                                                                   | L <u>&lt;</u> 5                                                                                                | Igno               | red             |      |              |               |               | (5) (6)          |

| (Lin                                               | ner)[mm]                                           | W <u>≤</u> 0.05                                                                                           | 5 <l< td=""><td>0</td><td></td><td>PC</td><td>A, B, C</td><td>Of</td><td>f</td><td>(5), (6),<br/>(7)</td></l<> | 0                  |                 | PC   | A, B, C      | Of            | f             | (5), (6),<br>(7) |

| W:W                                                | Width, L:Length                                    | 0.05 <w< td=""><td>-</td><td>0</td><td></td><td></td><td></td><td></td><td></td><td>()</td></w<>          | -                                                                                                              | 0                  |                 |      |              |               |               | ()               |

|                                                    | atch of Polarizer                                  |                                                                                                           | D <u>&lt;</u> 0.25                                                                                             | Igno               | red             |      |              |               |               | (5) (6)          |

| (Cir                                               | cular)[mm]                                         | 0.25 <d< td=""><td>0</td><td></td><td>PC</td><td>A, B, C</td><td>Of</td><td>f</td><td>(5), (6),</td></d<> |                                                                                                                | 0                  |                 | PC   | A, B, C      | Of            | f             | (5), (6),        |

| D:A                                                | verage diameter                                    | -                                                                                                         |                                                                                                                | -                  |                 |      |              |               |               | (7)              |

| Air                                                | Bubble                                             | D <u>≤</u> 0.25<br>0.25 <d<br>-</d<br>                                                                    |                                                                                                                | Igno               | red             |      |              |               |               | (5) $(6)$        |

| [mn                                                | n]                                                 |                                                                                                           |                                                                                                                | 0                  | 0               |      | A, B, C      | Off           |               | (5), (6),        |

| D:A                                                | verage diameter                                    |                                                                                                           |                                                                                                                | -                  |                 |      |              |               |               | (7)              |

|                                                    | atch of FPC                                        |                                                                                                           |                                                                                                                | Seriou<br>is not a |                 | -    | D            | Of            | f             | (7)              |

| Japan                                              | Display Inc.                                       | Date                                                                                                      | Dec. 5, 2017                                                                                                   | , Sh.<br>No.       |                 | JDG0 | 10000744     | - 1           | Pag           | ge 24 / 35       |

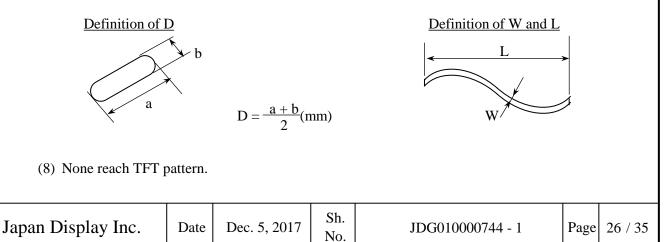

11.3.2 Panel chipping Specification: It is internal standard, and this is not guaranteed SPEC.

| Item                                | Criterion for Defects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Note |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|