# Inlink-CC<sup>\*</sup>

# Capacitor Coupled HART® Protocol Modem Module for OEM Applications

April 2011

# General Description

InLink-CC is a modem module for Highway Addressable Remote Transducer (HART) communications. It allows designers to easily implement a HART compliant modem without knowledge of the HART physical layer requirements. InLink-CC requires only three controller I/O pins; transmit data (TXD), receive data (RXD), and request to send (RXD).

InLink-CC is a complete modem solution, including capacitor coupling to the HART loop. The carrier detect (CD) output provides indication that a HART signal is being received. When RTS is low, the modulator is selected. Data to be transmitted is shifted into the TXD pin at 1200 BAUD. The modem modulates the data using phase continuous frequency shift keying (FSK) at Bell 202 shift frequencies of 1200Hz and 2200Hz. The transmitted waveform is shaped to meet the slew rate requirements of the HART protocol. Received data is filtered, demodulated, and converted to space and mark serial data at 1200 BAUD, shifted out on the RXD pin.

If isolation is a requirement for your application consider the 101-0016 InLink-TC which includes galvonic transformer isolation and a wide 3V to 5.2V supply range.

## **HART® Protocol**

The HART protocol is supported by the HART Communications Foundation, 9390 Research Blvd., Austin Texas 78759, USA. HART protocol specifications are available from the HART Communications Foundation.

Visit http://www.hartcomm.org for details.

## **Features**

- · Complies with HART Protocol Physical Layer

- Includes Capacitor Coupling to the HART Loop

- Modem Module Reduces Time-To-Market

- Small Footprint Simplifies Design Integration

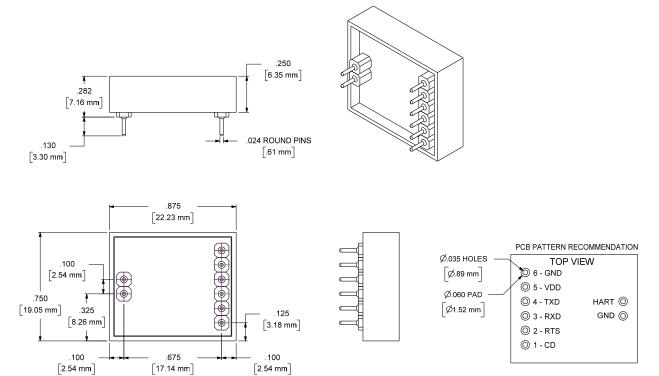

- Rugged Encapsulated Package with Gold Plated Pins for Increased Reliability

- Through-hole or Socket mounting

- 2.7V to 3.6V Operating Voltage

- Industrial Temperature Range, -40°C to +85°C

- Transmit Signal Wave-Shaping Sinusoidal Output with Lowest Harmonic Distortion

- Receive Band-Pass Filter and Digital Processing Provides Reliable Input Detection in Noisy Conditions

- CMOS Compatible

- Low Power 300μA Typical

# **Applications**

- Add HART capabilities to loop devices

- Remote Data Logging

- SCADA Units with HART capabilities

- Flow Computers

- Fieldbus HART Interfaces

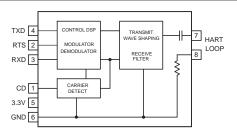

# **Block Diagram**

Figure 1. InLink Block Diagram

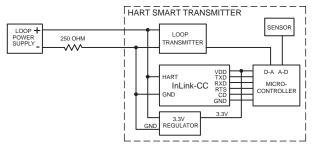

# Typical Application

The InLink-CC application shown in Figure 2 is for a loop-powered HART protocol smart transmitter. InLink-CC can also be used to simplify adding smart capabilities to exsisting devices

Figure 2. Typical Application, HART smart transmitter

# Application Considerations

## Power Considerations

The InLink-CC power supply, VDD, should be heavily filtered to prevent noise from interfering with the received HART data. VDD should have less than ±50mV of noise.

### Connecting to the HART Network

A HART modem must be coupled to the field device loop in a way that does not interfere with the current loop. InLink includes the necessary components to simplify this.

InLink-CC does not provide issolation and care should be taken when testing devices with floating grounds. In applications where the loop resistor is in the (-) side of the loop, the InLink-CC ground will be at a different potential than the loop supply ground.

## Pin Descriptions

#### 1 - CD

Carrier Detect (CD) indicates when a valid HART signal is being received. CD is high when RTS is high (InLink in receive or demodulate mode) and four consecutive pulses of an amplitude greater than a nominal 100mV p-p are received over the HART interface. CD will stay high as long as valid pulses continue to be received in less than 2.5ms between pulses. Once CD goes inactive, it takes another 4 consecutive pulses to activate it again. Four pulses amount to 3.33 ms at 1200 Hz and 1.82 ms when receiving 2200 Hz.

#### 2 - RTS

RTS is used to switch the modem between modulate mode, transmitting, and demodulate mode, receiving. A low level on RTS will activate the modulator. A high level on RTS will activate the demodulator.

### 3 - RXD

Received data is demodulated and shifted out serially on the RXD output. RXD will be high when receiving the 1200 Hz HART carrier, and low when receiving the 2200 Hz carrier. RXD is qualified internally with CD.

## 4 - TXD

TXD is the input to the InLink modulator. Data is shifted into the modem in a serial NRZ format. When TXD is low, the modulated HART frequency is 2200 Hz. When TXD is high, the modulated HART frequency is 1200 Hz.

## 5 - VDD

This is the InLink power input. To ensure a valid power on reset VDD should rise from 0V to 2.7V in less than 1ms. VDD should be between 2.7V and 3.6V, typically 3.3V, and have less than 50mv P-P noise. Wait at least 10ms after power on before starting a HART transaction.

## 6 - GND

InLink ground.

## HART/GND

These two pins are the HART protocol interface to the InLink modem. The HART pin is internally capacitor coupled to the loop. GND is internally connected to pin 6 - GND.

# Absolute Maximum Ratings

# **Operating Ratings**

Supply Voltage 3.6V Supply Voltage 2.7V to 3.6V -40°C to 85°C

DC Input, Output -0.5 Min, V<sub>DD</sub> + 0.3 Max Temperature Range

Storage Temp. Range-55°C to 150°C

## Cautions:

- 1. CMOS devices are damaged by high-energy electrostatic dishcarge. Modules must be stored in conductive foam or static bags.

- 2. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the module.

- 3. Remove power before insertion or removal of this module.

| Symbol           | Parameter                                    | V <sub>DD</sub> | Min.      | Тур. | Max.      | Units      |

|------------------|----------------------------------------------|-----------------|-----------|------|-----------|------------|

| $V_{\text{IL}}$  | Input Voltage - Low                          | 3.3             |           |      | 0.3 x VDD | V          |

| VIH              | Input Voltage - High                         | 3.3             | 0.7 x VDD |      |           | V          |

| Vol              | Output Voltage - Low (IOL=2mA)               | 3.3             |           |      | 0.5       | V          |

| Vон              | Output Voltage - High (IOH=2mA)              | 3.3             | 2.4       |      |           | V          |

| Cin              | Input Capacitance                            |                 |           | 2.9  |           | pF         |

| IIL/IH           | Input Leakage Current                        |                 |           |      | ±500      | nA         |

| loll             | Output Leakage Current                       |                 |           |      | ±10       | μΑ         |

| Ілтх             | Power Supply Current Transmitting (250 load) | 3.3             |           | 640  |           | μΑ         |

| I <sub>DRX</sub> | Power Supply Current Receiving               | 3.3             |           | 300  |           | μΑ         |

|                  | Demodulator Jitter                           |                 |           | 12   |           | % of 1 bit |

| R <sub>PO</sub>  | Power On Reset                               |                 |           | 0.5  | 2         | mS         |

| CD⊤              | Carrier Detect Threshold                     | 3.3             | 80        | 100  | 120       | mV         |

|                  | Power On Delay                               |                 |           |      | 10        | mS         |