# STUDENT WORKBOOK

Mr Circuit Lab 3

# "DIGITAL LOGIC GATES"

(#1301-P)

contains the printed Lessons, the printed Workbook, Solderless Circuit Board and experiment parts.

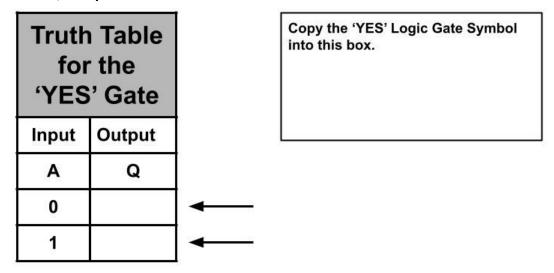

#### 1. The 'YES' Digital Logic Gate

Here is the 'YES' Logic Gate symbol

Rule for 'YES' Logic Gate: The OUTPUT is TRUE only if the INPUT is TRUE.

Using this rule, complete the Truth Table below:

# 2. The 'NOT' Digital Logic Gate

Here is the 'NOT' Logic Gate symbol

Rule for 'NOT' Logic Gate: The OUTPUT is FALSE only if the INPUT is TRUE. Using this rule, complete the Truth Table below:

| foi   | n Table<br>r the<br>ſ' Gate |          | Copy the 'NOT' Logic Gate Symbol into this box. |

|-------|-----------------------------|----------|-------------------------------------------------|

| Input | Output                      |          |                                                 |

| Α     | Q                           |          |                                                 |

| 0     |                             | <b>←</b> |                                                 |

| 1     |                             | <b>-</b> |                                                 |

#### 3. The 'AND' Digital Logic Gate

Here is the 'AND' Logic Gate symbol

Rule for 'AND' Logic Gate: The OUTPUT is TRUE only if <u>both</u> INPUTS are TRUE. Using this rule, complete the Truth Table below:

|            | Truth Table for the<br>'AND' Gate |             |          | Copy the 'AND' Logic Gate Symbol into this box. |

|------------|-----------------------------------|-------------|----------|-------------------------------------------------|

| Input<br>A | Input<br>B                        | Output<br>Q |          |                                                 |

| 0          | 0                                 |             | ] ←—     |                                                 |

| 0          | 1                                 |             | ]←—      |                                                 |

| 1          | 0                                 |             | <b>─</b> |                                                 |

| 1          | 1                                 |             | ]←—      |                                                 |

### 4. The 'NAND' Digital Logic Gate

Here is the 'NAND' Logic Gate symbol

Rule for 'NAND' Logic Gate: The OUTPUT is FALSE only if <u>both</u> INPUTS are TRUE. Using this rule, complete the Truth Table below:

| Truth Table for the<br>'NAND' Gate |            |             | Copy the 'NAND' Logic Gate Symbol into this box. |  |

|------------------------------------|------------|-------------|--------------------------------------------------|--|

| Input<br>A                         | Input<br>B | Output<br>Q | 1                                                |  |

| 0                                  | 0          |             | <b>—</b>                                         |  |

| 0                                  | 1          |             | ]←                                               |  |

| 1                                  | 0          |             | <b>—</b>                                         |  |

| 1                                  | 1          |             | <b>—</b>                                         |  |

#### 5. The 'OR' Digital Logic Gate

Here is the 'OR' Logic Gate symbol

Rule for 'OR' Logic Gate: The OUTPUT is TRUE if either or both INPUTS are TRUE. Using this rule, complete the Truth Table below:

|            | n Table f<br>'OR' Ga |             |          |

|------------|----------------------|-------------|----------|

| Input<br>A | Input<br>B           | Output<br>Q |          |

| 0          | 0                    |             | <b>—</b> |

| 0          | 1                    |             | <b>─</b> |

| 1          | 0                    |             | <b>—</b> |

| 1          | 1                    |             | <b>—</b> |

Copy the 'OR' Logic Gate Symbol into this box.

# 6. The 'NOR' Digital Logic Gate

Here is the 'NOR' Logic Gate symbol

Rule for 'NOR' Logic Gate: The OUTPUT is FALSE if either or <u>both</u> INPUTS are TRUE. Using this rule, complete the Truth Table below:

|            | Truth Table for the 'NOR' Gate |             |          | Copy the 'NOR' Logic Gate Symbol into this box. |

|------------|--------------------------------|-------------|----------|-------------------------------------------------|

| Input<br>A | Input<br>B                     | Output<br>Q |          |                                                 |

| 0          | 0                              |             | <b>─</b> |                                                 |

| 0          | 1                              |             | <b>─</b> |                                                 |

| 1          | 0                              |             | <b>—</b> |                                                 |

| 1          | 1                              |             | <b>─</b> |                                                 |

#### 7. The 'XOR' Digital Logic Gate

Here is the 'XOR' Logic Gate symbol

Rule for 'XOR' Logic Gate: The OUTPUT is TRUE if <u>either but not both</u> INPUTS are TRUE. Using this rule, complete the Truth Table below:

|            | n Table f<br>XOR' Ga |             |          |

|------------|----------------------|-------------|----------|

| Input<br>A | Input<br>B           | Output<br>Q | ]        |

| 0          | 0                    |             | ]←       |

| 0          | 1                    |             | <b>—</b> |

| 1          | 0                    |             | <b>—</b> |

| 1          | 1                    |             | ]←       |

Copy the 'XOR' Logic Gate Symbol into this box.

# 8. The 'XNOR' Digital Logic Gate

Here is the 'XNOR' Logic Gate symbol

Rule for 'XNOR' Logic Gate: The OUTPUT is FALSE if <u>either but not both</u> INPUTS are TRUE. Using this rule, complete the Truth Table below:

|            | Truth Table for the<br>'XNOR' Gate |             |           | Copy the 'XNOR' Logic Gate Symbol into this box. |

|------------|------------------------------------|-------------|-----------|--------------------------------------------------|

| Input<br>A | Input<br>B                         | Output<br>Q | 1         |                                                  |

| 0          | 0                                  |             | <b>—</b>  |                                                  |

| 0          | 1                                  |             | <b>←</b>  |                                                  |

| 1          | 0                                  |             | <b>——</b> |                                                  |

| 1          | 1                                  |             | <b>→</b>  |                                                  |

Copyright Mr Circuit Technology ©2023

#### Fill-in the missing words in the Rules for Logic Gates

| 1. Rule for 'YES' Logic Gate: The OUTPUT is                               | only if the INPUT is                          |

|---------------------------------------------------------------------------|-----------------------------------------------|

| 2. Rule for 'NOT' Logic Gate: The OUTPUT is                               | only if the INPUT is                          |

| 3. Rule for 'AND' Logic Gate: The OUTPUT is                               | only if both INPUTS are                       |

| 4. Rule for 'NAND' Logic Gate: The OUTPUT is                              | only if <u>both</u> INPUTS are                |

| 5. Rule for 'OR' Logic Gate: The OUTPUT is                                | if either or both INPUTS are                  |

| 6. Rule for 'NOR' Logic Gate: The OUTPUT is                               | _ if either or <u>both</u> INPUTS are         |

| 7. Rule for 'XOR' Logic Gate: The OUTPUT is                               | if <u>either but not both</u> INPUTS are      |

| 8. Rule for 'XNOR' Logic Gate: The OUTPUT is                              | if either but not both INPUTS are             |

| "The OUTPUT is FALSE "                                                    | •                                             |

| Here are the Logic Gate Symbols. Can you match them to the with its name. | neir names? Draw a line connecting the symbol |

| YES Gate                                                                  | <b>⇒</b> >                                    |

| NOT Gate                                                                  | -7-                                           |

| AND Gate                                                                  | ~                                             |

|                                                                           |                                               |

| NAND Gate                                                                 | =D~                                           |

| NAND Gate  OR Gate                                                        | <b>-</b> D-                                   |

|                                                                           | <del></del>                                   |

Copyright Mr Circuit Technology ©2023

**XNOR Gate**