# PSpice Model High-side driver with MultiSense analog feedback for automotive applications STMicroelectronics VN7020AJ

# **Model Information**

| Model      | A macro model                                                     |

|------------|-------------------------------------------------------------------|

| Call Name  | MDC_VN7020AJ_PS                                                   |

|            | 1:INPUT 2:FaultRSTB 3:SEn 4:AGND 5:SEL0 6:SEL1 7:MultiSense 8:NC1 |

| Pin Assign | 9:NC2 10:NC3 11:NC4 12:NC5 13:OUTPUT1 14:OUTPUT2 15:OUTPUT3       |

|            | 16:OUTPUT4 17:VCC                                                 |

| File List  | Model Library MDC_VN7020AJ_PS01.lib                               |

|            | Model Report MDC_VN7020AJ_PS.pdf(this file)                       |

Verified Simulator Version

PSpice

## Note

## References

The information which was used for modeling is as follow:

| [Data Sheet] |

|--------------|

|--------------|

| Date/Version | Rev 4              |

|--------------|--------------------|

| Product name | VN7020AJ           |

| Company name | STMicroelectronics |

[Characteristics listed]

| Standby mode activation                                   |

|-----------------------------------------------------------|

| Normal mode operation                                     |

| Short-circuit condition(Outputs configured for Latch-off) |

| UVLO                                                      |

| OFF-state diagnostics (Short to VCC)                      |

| OFF-state diagnostics (Open-load)                         |

| Negative output voltage (inductive loads turn-off)        |

| Turn-on/Turn-off delay time                               |

| MultiSense timings (current sense mode)                   |

| Multisense timings (chip temperature and VCC sense mode)  |

| Logic inputs (VIH=1.8V、VIL=1.35V)                         |

|                                                           |

## **Simulation Condition**

This table shows the range of evaluated simulation range that was not occurs any convergence problems in this area.

| Item        | Condition | Unit  |

|-------------|-----------|-------|

| Temperature | 25        | deg C |

# O : Implemented × : Not Implemented

# -: Not applicable

# **Model Functions Table**

|                                                           | RANK=1 |             |

|-----------------------------------------------------------|--------|-------------|

| Functions                                                 | RANK   | Implemented |

| Standby mode activation                                   | 1      | $\bigcirc$  |

| Normal mode operation                                     | 1      | $\bigcirc$  |

| Short-circuit condition(Outputs configured for Latch-off) | 1      | $\bigcirc$  |

| UVLO                                                      | 1      | $\bigcirc$  |

| OFF-state diagnostics (Short to VCC)                      | 1      | $\bigcirc$  |

| OFF-state diagnostics (Open-load)                         | 1      | $\bigcirc$  |

| Negative output voltage (inductive loads turn-off)        | 1      | $\bigcirc$  |

| Turn-on/Turn-off delay time                               | 1      | $\bigcirc$  |

| MultiSense timings (current sense mode)                   | 1      | $\bigcirc$  |

| Multisense timings (chip temperature and VCC sense mode)  | 1      | $\bigcirc$  |

| Logic inputs (VIH=1.8V、VIL=1.35V)                         | 1      | 0           |

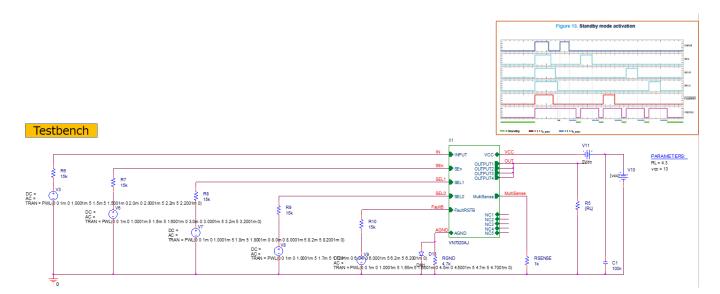

Standby mode activation

Simulation results are following. Explanatory notes — : simulated

Standby mode activation

Simulation results are following. Explanatory notes — : simulated

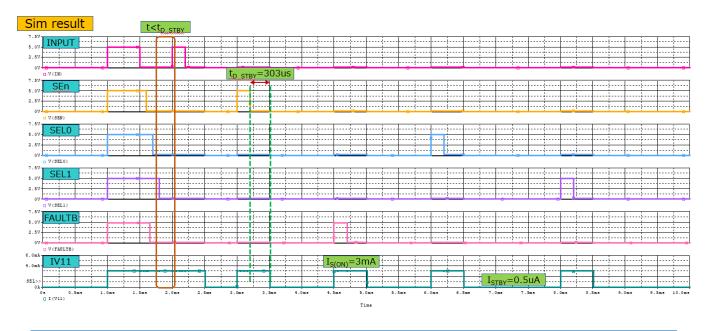

#### Normal mode operation

Simulation results are following. Explanatory notes - : simulated

Normal mode operation

Simulation results are following. Explanatory notes — : simulated

#### Sim result

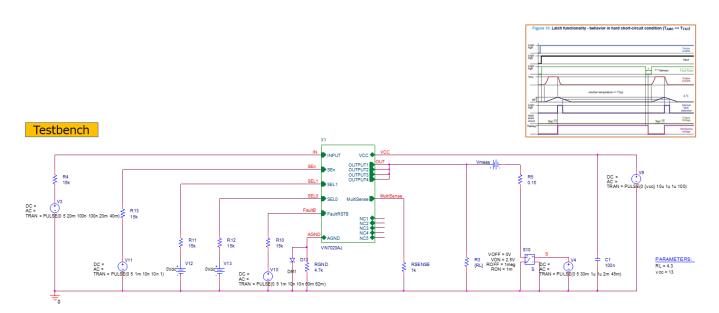

Short-circuit condition(Outputs configured for Latch-off)

Simulation results are following. Explanatory notes - : simulated

Short-circuit condition(Outputs configured for Latch-off)

Simulation results are following. Explanatory notes -: simulated

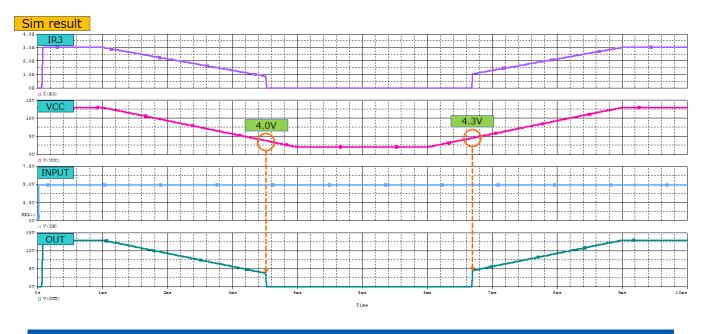

# UVLO

Simulation results are following. Explanatory notes -: simulated

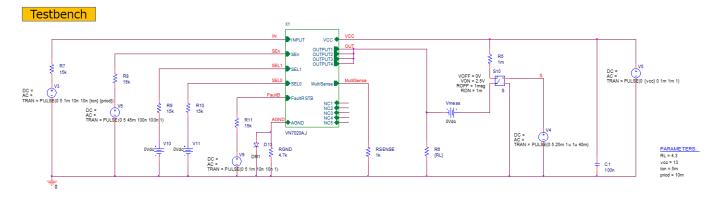

# Testbench

# UVLO

Simulation results are following. Explanatory notes -: simulated

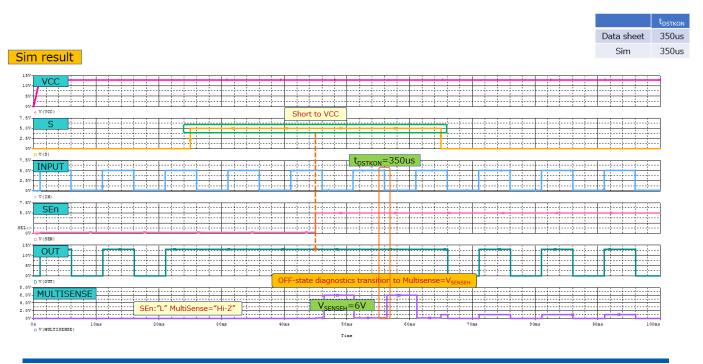

OFF-state diagnostics (Short to VCC) Simulation results are following.

Explanatory notes — : simulated

OFF-state diagnostics (Short to VCC) Simulation results are following. Explanatory notes — : simulated

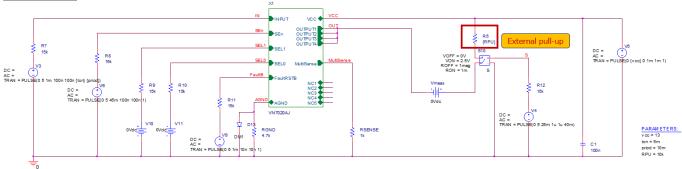

# OFF-state diagnostics (Open-load)

Simulation results are following. Explanatory notes — : simulated

OFF-state diagnostics (Open-load) Simulation results are following. Explanatory notes — : simulated

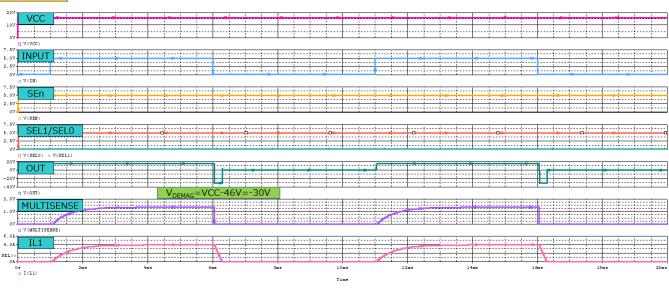

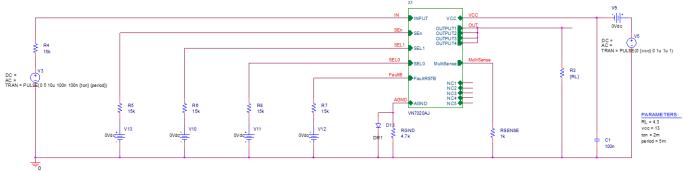

Negative output voltage (inductive loads turn-off)

Simulation results are following.

Explanatory notes - : simulated

## Testbench

Negative output voltage (inductive loads turn-off) Simulation results are following. Explanatory notes — : simulated

## Sim result

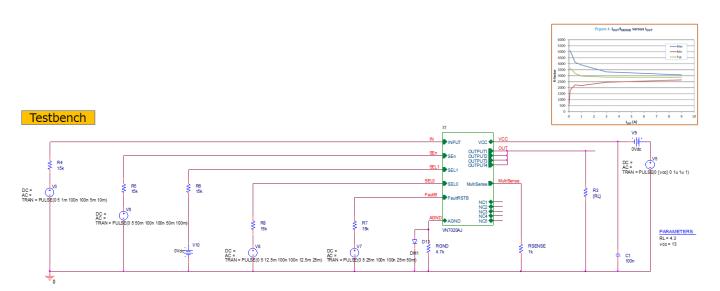

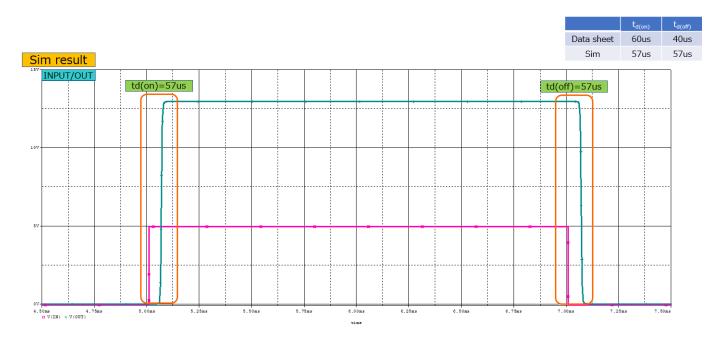

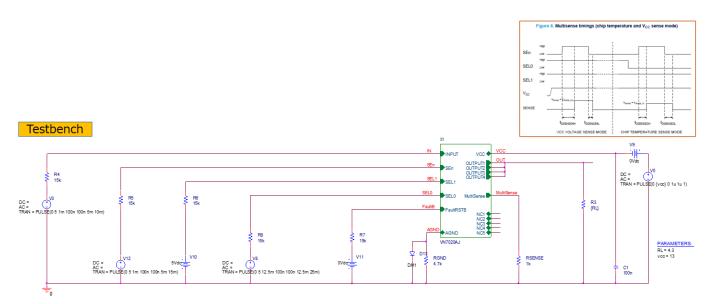

Turn-on/Turn-off delay time

Simulation results are following. Explanatory notes — : simulated

#### Testbench

Turn-on/Turn-off delay time Simulation results are following.

Explanatory notes — : simulated

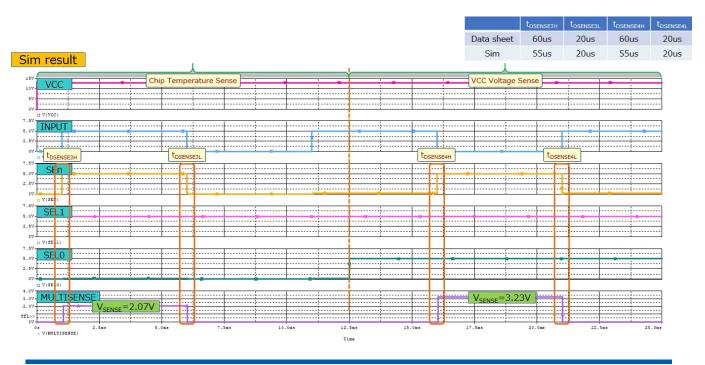

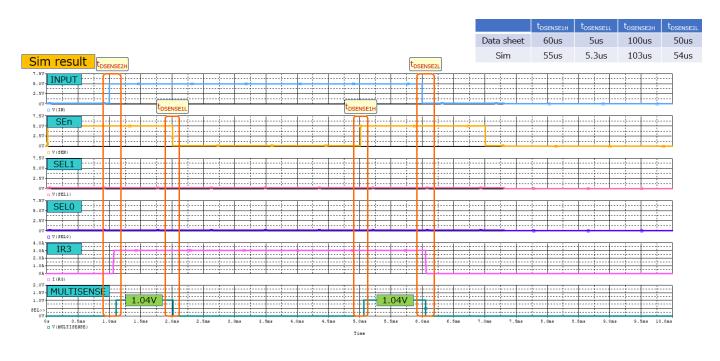

Multisense timings (chip temperature and VCC sense mode)

Simulation results are following.

Explanatory notes -: simulated

Multisense timings (chip temperature and VCC sense mode)

Simulation results are following.

Explanatory notes - : simulated

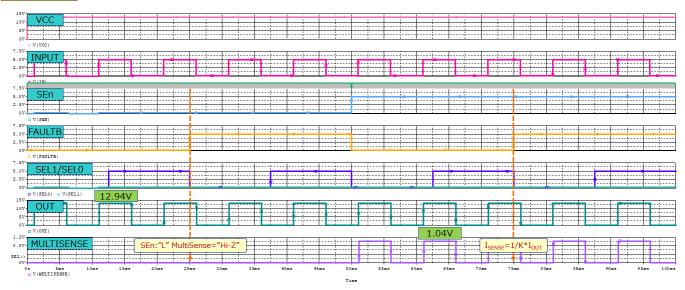

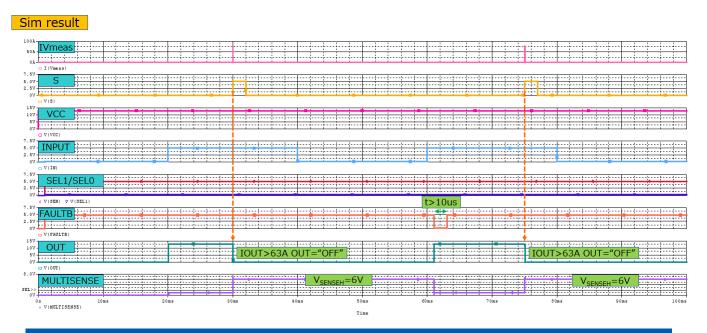

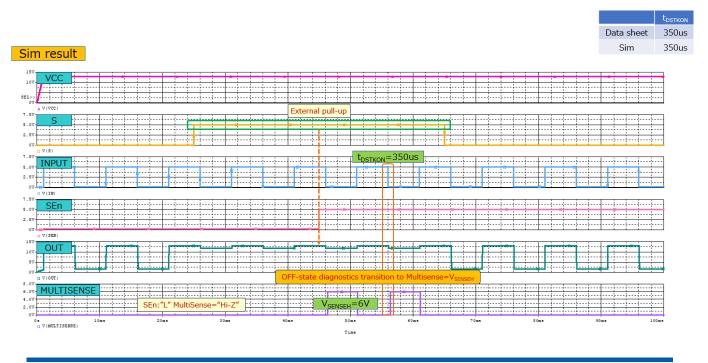

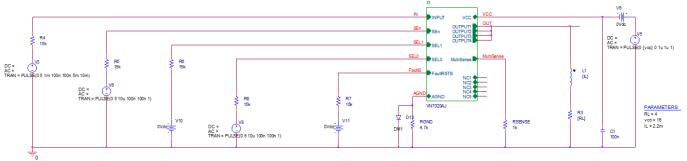

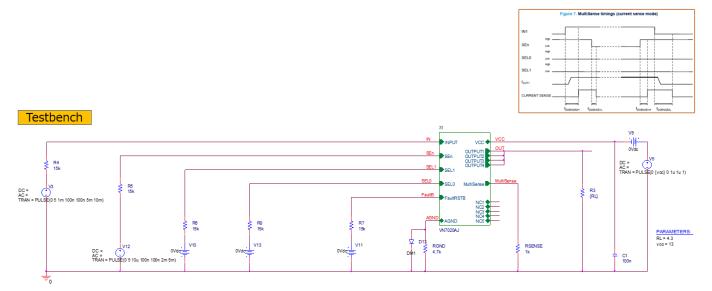

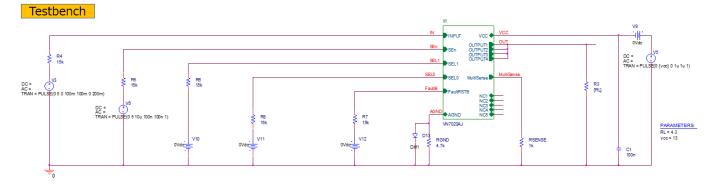

## MultiSense timings (current sense mode)

Simulation results are following.

Explanatory notes -: simulated

# MultiSense timings (current sense mode) Simulation results are following.

Explanatory notes — : simulated

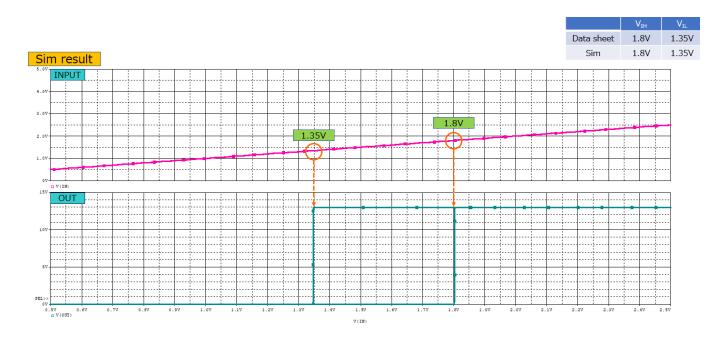

Logic inputs (VIH=1.8V, VIL=1.35V) Simulation results are following. Explanatory notes — : simulated

Logic inputs (VIH=1.8V, VIL=1.35V) Simulation results are following. Explanatory notes — : simulated

# DISCLAIMER

- 1. This SPICE (Simulation Program with Integrated Circuit Emphasis) model and its content (the "Contents") are copyright of MoDeCH Inc. All rights reserved. Any redistribution or reproduction of any or all part of the Contents in any form is prohibited without express written permission made by MoDeCH Inc.

- 2. MoDeCH Inc. as licensor (the" Licensor") hereby grants to you, as licensee (the "Licensee"), a nonexclusive, non-transferable license to use the Contents as long as you abide by the terms and conditions of this DISCLAIMER.

- 3. The Licensee is not authorized to sell, loan, rent and redistribute or license the Contents in whole or in part, or in modified form, to anyone.

- 4. The Licensor shall in no way be liable to the Licensee or any third party for any loss or damage (including ,but not limited to, lost profits, or other incidental, consequential, or punitive damages), however caused (including through negligence) which may be directly or indirectly suffered from, arising out of, or in connection with, any use of the Contents.

- 5. Notwithstanding anything contained in this DISCLAIMER, in no event shall Licensor be liable for any claims, damages or loss which may arise from the modification, combination, operation or use of the Contents with the Licensee's computer programs.

- 6. The Licensor does not warrant that the Contents will function in any environment.

- 7. The Contents may be changed or updated without notice. MoDeCH Inc. may also make improvements and/or changes in the products, pricing and/or the programs related to the Contents at any time without notice.

MoDeCH Inc.

Head Office Location: 5-15 Yokoyama-cho, Hachioji-Shi, Tokyo 192-0081, Japan Tel:+81-42-656-3360 E-Mail:model-on-support@modech.co.jp URL:http://www.modech.com/en/