# **LTspice Model Film Capacitor** SHIZUKI ELECTRIC COMPANY INC. UR80Y807K81573

## **Model Information**

| Model                      | A macro mode          | I                                    |  |

|----------------------------|-----------------------|--------------------------------------|--|

| Call Name                  | MDC_UR80Y807K81573_LT |                                      |  |

| Pin Assign                 | 2 pins, no polarity   |                                      |  |

| File List                  | Model Library         | MDC_UR80Y807K81573_LT01.lib          |  |

|                            | Model Report          | MDC_UR80Y807K81573_LT.pdf(this file) |  |

| Verified Simulator Version |                       | LTspice XVII                         |  |

Note

### References

The information which was used for modeling is as follow:

[Data Sheet]

| N.A.                          |

|-------------------------------|

| UR80Y807K81573                |

| SHIZUKI ELECTRIC COMPANY INC. |

|                               |

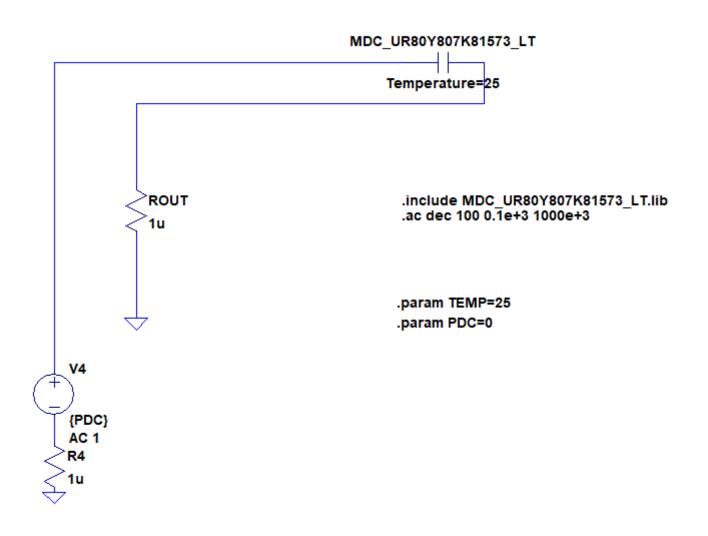

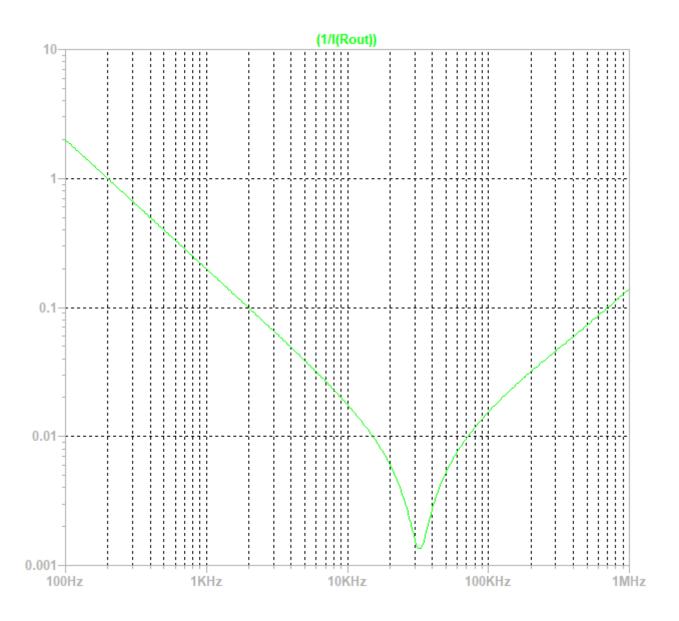

ESR vs Frequency Impedance vs Frequency

### Simulation Condition

This table shows the range of evaluated simulation range that was not occurs any convergence problems in this area.

| Item        | Condition | Unit  |

|-------------|-----------|-------|

| Temperature | 25        | deg C |

## **Model Functions Table**

| Functions              | Implemented |

|------------------------|-------------|

| ESR vs Frequency       | 0           |

| Impedance vs Frequency | 0           |

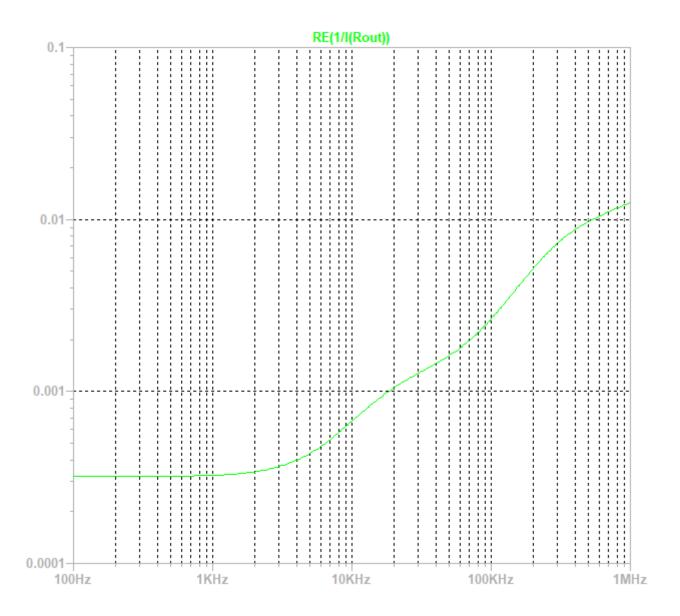

ESR vs Frequency Testbench

## **Referred to Data Sheet**

Simulation results are following. Explanatory notes — : simulated

ESR vs Frequency

Impedance vs Frequency Testbench

# **Referred to Data Sheet**

Simulation results are following. Explanatory notes — : simulated

Impedance vs Frequency

## DISCLAIMER

- 1. This SPICE (Simulation Program with Integrated Circuit Emphasis) model and its content (the "Contents") are copyright of MoDeCH Inc. All rights reserved. Any redistribution or reproduction of any or all part of the Contents in any form is prohibited without express written permission made by MoDeCH Inc.

- 2. MoDeCH Inc. as licensor (the" Licensor") hereby grants to you, as licensee (the "Licensee"), a nonexclusive, non-transferable license to use the Contents as long as you abide by the terms and conditions of this DISCLAIMER.

- 3. The Licensee is not authorized to sell, loan, rent and redistribute or license the Contents in whole or in part, or in modified form, to anyone.

- 4. The Licensor shall in no way be liable to the Licensee or any third party for any loss or damage (including ,but not limited to, lost profits, or other incidental, consequential, or punitive damages), however caused (including through negligence) which may be directly or indirectly suffered from, arising out of, or in connection with, any use of the Contents.

- 5. Notwithstanding anything contained in this DISCLAIMER, in no event shall Licensor be liable for any claims, damages or loss which may arise from the modification, combination, operation or use of the Contents with the Licensee's computer programs.

- 6. The Licensor does not warrant that the Contents will function in any environment.

- 7. The Contents may be changed or updated without notice. MoDeCH Inc. may also make improvements and/or changes in the products, pricing and/or the programs related to the Contents at any time without notice.

MoDeCH Inc.

Head Office Location: 5-15 Yokoyama-cho, Hachioji-Shi, Tokyo 192-0081, Japan Tel:+81-42-656-3360 E-Mail:model-on-support@modech.co.jp URL:http://www.modech.com/en/