# PRL-480N DUAL CHANNEL PROGRAMMABLE NECL DELAY MODULE

#### APPLICATIONS

- High Speed Clock De-skewing •

- Critical Timing Adjustment

- Sub-nanosecond Pulse Width generation

- An Essential Lab Tool for Working with GHz NECL Circuits

#### **FEATURES**

- 1.2 GHz Maximum Clock Rate •

- 2.2ns Maximum Delay

- 17.5ps minimum program resolution •

- Single-ended or Differential Inputs

- Internal 50 $\Omega$ /-2V Input Terminations also • accept Sine wave or AC coupled PECL Signals

- Complementary NECL Outputs drive  $50\Omega/-2V$

- DC Coupled I/O's

- SMA I/O Connectors •

- Ready-to-Use 1.3 x 2.9 x 3.9-in. Module including a ±8.5V/±1.4 A AC/DC Adapter

### DESCRIPTION

The PRL-480N is a dual channel programmable ECL Delay module. It is intended for clock de-skewing and critical timing adjustment in high speed logic circuit testing, and it has a maximum clock frequency of 1.2GHz. The outputs of the two channels can be connected to an AND gate, such as the PRL-435, for generating sub-nanosecond pulse width signals.

The delay of each channel can be individually programmed using a seven-position DIP-switch and a channel selector switch. When the channel selector switch is up, channel I is in the pass-through mode, and channel II is latched. Any change in the DIP switch setting causes a delay change in the channel I outputs only. Similarly, when the switch is down, channel II only is in pass-through mode. When the switch is in the center position, or HOLD mode, both channels are latched.

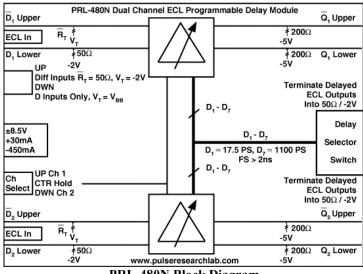

The input of each channel can be driven either differentially or single ended. A switch selects either single-ended or differential inputs, as shown in Fig. 1. In the differential input mode, both inputs D and  $\overline{D}$  are terminated internally into 50  $\Omega/2$  V, and, therefore, either one or both inputs can accept AC coupled signals as well. In the single input mode, signals should be connected to the D inputs only. Inputs  $\overline{D}$  are switched internally to V<sub>BB</sub>, nominally -1.3 V, and termination resistors  $\overline{R}_{T}$ 's for the  $\overline{D}$  input channels are changed to 62  $\Omega$ . Complementary outputs of the PRL-480 are designed for driving 50  $\Omega$  loads terminated into -2 V, or AC coupled 50  $\Omega$  loads.

The PRL-480N is housed in a 1.3 x 2.9 x 3.9-in. extruded aluminum enclosure and is supplied with a  $\pm 8.5$  V/ $\pm 1.4$  A AC/DC Adapter.

| SYMBOL            | PARAMETER                                                                               | Min             | Тур                                           | Max            | UNIT | Comments       |

|-------------------|-----------------------------------------------------------------------------------------|-----------------|-----------------------------------------------|----------------|------|----------------|

| R <sub>in</sub>   | Input Resistance                                                                        | 49.5            | 50                                            | 50.5           | Ω    |                |

| V <sub>TT</sub>   | Input Termination Voltage (fixed)                                                       | -2.2            | -2                                            | -1.8           | V    | D Inputs       |

| v <sub>T</sub>    | Input Termination Voltage (variable)                                                    | -1.17/-<br>2.2  | -1.3/-2                                       | -1.43/-<br>1.8 | V    | D Inputs       |

| +I <sub>CC</sub>  | Positive DC Input Current                                                               |                 | 25                                            | 30             | mA   |                |

| $-I_{EE}$         | Negative DC Input Current                                                               |                 | -420                                          | -450           | mA   |                |

| V <sub>DC</sub>   | DC Input Voltage                                                                        | ±7.5V           | ±8.5V                                         | ±12V           | V    |                |

| V <sub>AC</sub>   | AC/DC Adaptor Input Voltage                                                             | 103             | 115                                           | 127            | V    |                |

| t <sub>PLH</sub>  | Insertion propagation Delay to output $\uparrow$                                        |                 | 2500                                          |                | ps   | D1-D7 set to 0 |

| t <sub>PHL</sub>  | Insertion propagation Delay to output $\downarrow$                                      |                 | 2500                                          |                | ps   | D1-D7 set to 0 |

| Δt                | Step Delay<br>D1 High<br>D2 High<br>D3 High<br>D4 High<br>D5 High<br>D6 High<br>D7 High |                 | 17.5<br>35<br>70<br>140<br>280<br>560<br>1120 |                | ps   |                |

| $t_r/t_f$         | Rise/Fall Times (20%-80%)                                                               |                 | 700                                           | 900            | ps   | Note (1)       |

| t <sub>SKEW</sub> | Skew between Q& $\overline{Q}$ Outputs                                                  |                 | 40                                            | 80             | ps   |                |

| t <sub>SKEW</sub> | Skew between Q1& Q2 Outputs                                                             |                 | 40                                            | 80             | ps   | D1-D7 set to 0 |

| fMAX              | Max clock frequency                                                                     | 1               | 1.2                                           |                | GHz  | Note (2)       |

| V <sub>CMR</sub>  | Common Mode Range                                                                       | -2.7            |                                               | -0.4           | V    |                |

|                   | Size                                                                                    | 1.3 x 2.9 x 3.9 |                                               |                | in.  |                |

|                   | Weight                                                                                  |                 | 8                                             |                | Oz   |                |

## **SPECIFICATIONS\*** ( $0^{\circ}$ C $\leq$ TA $\leq$ **35** $^{\circ}$ C)

PRL-480N Block Diagram

\*All measurements are made with outputs terminated into 50  $\Omega$ /-2 V, using the PRL-550NQ4X, four-channel NECL Terminators, connected to a 50  $\Omega$  input sampling oscilloscope.

#### Notes:

(1). The output rise and fall times are measured with both the Q and  $\overline{Q}$  outputs terminated into 50  $\Omega$ /-2 V. An unused complementary output should be either terminated into 50  $\Omega$ /-2 V or AC coupled into a 50  $\Omega$  load. Otherwise, output waveform distortion and rise time degradation will occur. Use the PRL-550ND4X or PRL-550NQ4X, two or four channel ECL Terminators, respectively, for the 50  $\Omega$ /-2 V termination and for connection of ECL signals to 50  $\Omega$  input oscilloscopes when DC level information is required. Otherwise, use the PRL-ACT-50, dual AC coupled 50  $\Omega$  Termination module, for the unused outputs and the PRL-SC-104 DC Block for connection to a 50  $\Omega$  input oscilloscope. The PRL-ACX-12dB, AC coupled attenuator, can also be used for either terminating unused output or connection to a 50  $\Omega$  input oscilloscope.

(2).  $f_{MAX}$  is measured by AC coupling a sine wave to the D input using the differential input mode (switch up). The differential outputs are first divided by four, using the PRL-255N, and then measured using the PRL-550NQ4X four channel NECL Terminator, connected to a sampling 'scope.