# PRL-4122, 1:22 FANOUT 50 $\Omega$ TTL/CMOS LINE DRIVER

## **APPLICATIONS**

- TTL/CMOS Clock Distribution

- 1:22 Fanout Line Driver

- High Speed Digital Communications System Testing

- Mini Modular Instrument

# **FEATURES**

- $f_{MAX} > 100 \text{ MHz}$

- Drives 100 ft of cable @ 80 MHz

- 1.8 ns Typical Output Rise & Fall Times

- 2.5 V into 50 Ω Typical

- TTL Compatible 50  $\Omega$  or 1 k $\Omega$  Input

- Twenty in-phase 50  $\Omega$  TTL Outputs

- Two auxiliary 50  $\Omega$  TTL Outputs suitable for cascading

- Active Low EN (Enable) Inputs for each bank of 10 outputs

- BNC I/O Connectors, plus two SMA auxiliary outputs

- DC Coupled I/Os

- Self-contained 3.0 x 6.8 x 4.0-in. unit includes an AC/DC Adapter

PRL-4122-BNC, Front View

PRL-4122-BNC, Rear View

# **DESCRIPTION:**

The PRL-4122-BNC is a 1:22 fanout, 50  $\Omega$  TTL Line Driver. It is intended for distribution of high-speed clock and logic signals to multiple loads via long lines. The 50  $\Omega$  back-terminated outputs can drive long lines with or without 50  $\Omega$  load terminations. With 50  $\Omega$  load terminations, however, all outputs of the PRL-4122 can drive 100 ft of 50  $\Omega$  cables at clock rates greater than 80 MHz.

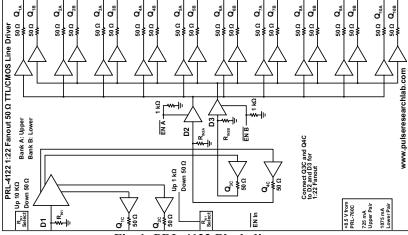

The PRL-4122 is implemented as a 1:4 fanout buffer (equivalent to a PRL-414B module) with two of its outputs externally cabled to the inputs of two 1:10 fanout buffers (each equivalent to a PRL-4110 module). The twenty outputs from the two 1:10 modules are in phase, while the additional two outputs of the 1:4 module are advanced by approximately 10 ns. These auxiliary outputs can be used to drive PRL-4110 or PRL-4220 units for additional in-phase outputs.

The input resistance of the PRL-4122's primary input can be selected to be either  $50 \Omega$  or  $1 k\Omega$  by a switch. The  $1 k\Omega$ -input is desirable when interfacing with low power circuits. The  $50 \Omega$  back terminated outputs typically deliver 2.5 V into  $50 \Omega$  or 5.0 V into Hi-Z loads. All I/Os are DC coupled and have BNC connectors, except for the auxiliary outputs which are SMA. SMA primary I/Os are available on special order (P/N PRL-4122-SMA).

Each 1:10 fanout bank also has an independent TTL-compatible  $\overline{EN}$  input pulled down via a 1 k $\Omega$  resistor. When left open the Enable is active, and the fanout bank will output signals. Each bank can be disabled by driving its  $\overline{EN}$  input high. A block diagram showing the equivalent input and output circuits of the PRL-4122 is shown in Fig. 1.

The PRL-4122 is housed in a 3.0 x 6.8 x 4.0-in. extruded aluminum enclosure and is supplied with the PRL-760C,  $\pm 8.5 \text{ V/} \pm 1.8 \text{ A C/DC}$  Adapter.

## **RELATED PRODUCTS:**

PRL-4110, 1:10 Fanout 50  $\Omega$  TTL Line Driver

PRL-4220, 2:20 Fanout 50 Ω TTL Line Driver, equivalent to two PRL-4110 units in a single enclosure

PRL-4330, 3:30 Fanout 50 Ω TTL Line Driver, equivalent to three PRL-4110 units in a single enclosure

1234 Francisco Street, Torrance, CA 90502 Tel: 310-515-5330 Fax: 310-515-0068 sales@pulseresearchlab.com www.pulseresearchlab.com

# PRELIMINARY SPECIFICATIONS\* (0 °C $\leq$ Ta $\leq$ 35 °C)

Unless otherwise specified, dynamic measurements are made with the input set to  $50 \Omega$  and all outputs terminated into  $50 \Omega$ .

| SYMBOL              | PARAMETER                              | Min  | Тур     | Max             | UNIT | Comments                         |

|---------------------|----------------------------------------|------|---------|-----------------|------|----------------------------------|

| R <sub>IN Low</sub> | Input Resistance Low Range             | 49.5 | 50.0    | 50.5            | Ω    |                                  |

| R <sub>IN Hi</sub>  | Input Resistance High Range            | 990  | 1000    | 1010            | Ω    |                                  |

| R <sub>IN EN</sub>  | Input Resistance, Enable               |      | 1       |                 | kΩ   |                                  |

| R <sub>OUT</sub>    | Output Resistance                      |      | 50      |                 | Ω    |                                  |

| $V_{\mathrm{IL}}$   | TTL Input Low Level                    | -0.5 | 0.0     | 0.5             | V    |                                  |

| $V_{\mathrm{IH}}$   | TTL Input High Level                   | 2.0  | 2.4     | 5.0             | V    |                                  |

| V <sub>IL EN</sub>  | EN Input Low Level                     | -0.5 | 0.0     | 0.5             | V    |                                  |

| V <sub>IH EN</sub>  | EN Input High Level                    | 2.0  | 2.4     | 5.0             | V    | Drive EN High to disable output  |

| Vol                 | TTL Output Low Level                   | 0.0  | 0.25    | 0.5             | V    | $R_L$ =50 $\Omega$               |

| Voh1                | TTL Output High Level                  | 2.2  | 2.5     |                 | V    | $R_L=50 \Omega @ DC$             |

| Voh2                | TTL Output High Level                  | 4.4  | 5.0     |                 | V    | $R_L=1 M\Omega @ DC$             |

| I <sub>DC1</sub>    | DC Input Current <sup>(1)</sup>        |      | 1220    |                 | mA   | f=50 MHz sq. wave <sup>(1)</sup> |

| $I_{DC2}$           | DC Input Current <sup>1)</sup>         |      | 1510    |                 | mA   | f ≤ 100 MHz                      |

| $I_{DC3}$           | DC Input Current <sup>1)</sup>         |      |         | 1800            | mA   | f=125 MHz                        |

| V <sub>DC</sub>     | DC Input Voltages                      | 7.75 | 8.50    | 12.00           | V    |                                  |

| V <sub>AC</sub>     | AC/DC Adapter Input Voltage            | 103  | 115     | 127             | V    |                                  |

| $T_{PLH}$           | Propagation Delay to output ↑          |      | 19      | 22              | ns   |                                  |

| $T_{ m PHL}$        | Propagation Delay to output ↓          |      | 19      | 22              | ns   |                                  |

| $t_r/t_f$           | Rise/Fall Times (10%-90%)              |      | 1.8/1.5 | 2.5             | ns   |                                  |

| T <sub>SKEW1</sub>  | Skew between any 2 outputs             |      | 500     | 900             | ps   | Within one 1:10 bank             |

| T <sub>SKEW1</sub>  | Skew between any 2 outputs             |      | 1200    | 1600            | ps   | Any two primary outputs          |

| F <sub>MAX1</sub>   | Max. Clock Frequency <sup>(2)(3)</sup> | 100  | 125     |                 | MHz  | RG58C/U, cable length = 3 ft     |

| F <sub>MAX2</sub>   | Max. Clock Frequency                   |      | 80      |                 |      | RG58C/U, cable length = 100 ft   |

| PW <sub>MIN1</sub>  | Minimum Pulse Width                    |      | 4       |                 | ns   | ↑ Input                          |

| PW <sub>MIN2</sub>  | Minimum Pulse Width                    |      | 6       |                 | ns   | ↓ Input                          |

|                     | Size                                   |      |         | 3.0 x 6.8 x 4.0 |      |                                  |

|                     | Weight                                 | 1.5  |         |                 | lb.  | Excluding AC adapter             |

Fig. 1: PRL-4122 Block diagram

#### Notes:

- (1) Power dissipation includes all three internal boards with all outputs terminated into  $50~\Omega$ . Each 1:10 board draws 725 mA maximum. The 1:4 board is powered internally from the bottom 1:10 board and draws 350 mA maximum.

- (2) f<sub>MAX</sub> should not exceed 125 MHz, otherwise damage of the unit due to overheating may result.

- (3) f<sub>MAX2</sub> is measured by driving a PRL-414B at the end of a 100 ft cable.