# PRL-257-2 6 GHz PROGRAMMABLE 2φ FREQUENCY DIVIDER

#### APPLICATIONS

- Systems Clock Simulation

- Low Jitter NECL Clock Source

- SONET Clock Generator

- Scope triggering

- PRBS/BERT synchronization

- Optimizing outputs from frequency synthesizers

- Testing high-speed serial/SERDES links

- An Essential Lab Tool for Working with ECL Circuits

### FEATURES

- 6.6 GHz maximum External Clock Input frequency

- f/2 to f/32 with independent  $2\varphi$  outputs

- Common Divide by 2 pre-scalar for both  $\varphi 1$  and  $\varphi 2$

- $\varphi$ 1 output=(f/2)/(1, 2, 4 or 8), for max. ratio of 16

- $\varphi$ 2 output=(f/2)/(2, 4, 8 or 16), for max. ratio of 32

- Both φ1 and φ2 have two pairs of complementary NECL square wave outputs

- Single-ended AC Coupled Input with internal 50  $\Omega$  terminations

- 5 ps typical Edge Jitter

- 40 ps typical skew between  $f/n \& \overline{f/n}$  NECL outputs

- Complementary DC coupled NECL Outputs drive 50  $\Omega$  loads terminated to -2 V, AC coupled or floating 50  $\Omega$  loads

- SMA I/O Connectors

- Ready-to-Use 1.3 x 2.9 x 2.9-in. Module includes a ±8.5V AC/DC Adapter

### DESCRIPTION

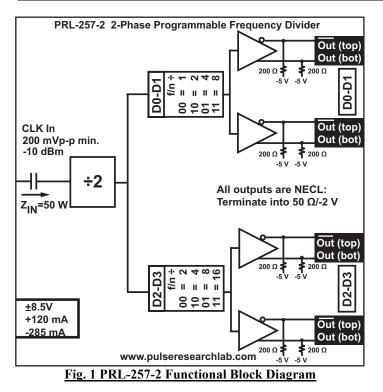

The PRL-257-2 is an AC-coupled input, manually programmable, two phase frequency divider with two sets of complementary NECL outputs. It is capable of running at input frequencies in excess of 6.6 GHz.

It has a common divide-by-2 pre-scalar front end followed by two banks of independent manually programmable dividers,  $\varphi$ 1 and  $\varphi$ 2. The f/2 pre-scalar output is further divided by 1, 2, 4, or 8 for the  $\varphi$ 1 bank via D0 and D1 of a two-bit DIP switch, providing a maximum ratio of 16. It is divided by 2, 4, 8 or 16 for the  $\varphi$ 2 bank via D2 and D3 of a second two-bit DIP switch, providing a maximum ratio of 32. All outputs are synchronous with the input frequency and are square waves (50% duty cycle) suitable for driving long lines terminated into 50  $\Omega$ /-2 V or AC-coupled 50  $\Omega$  loads.

The PRL-257-2 is ideal for applications where a high frequency divider or pre-scalar is needed for triggering or downsampling. The two phases of output enable applications requiring two different ratios from a common reference frequency. Applications for the PRL-257-2 include data acquisition, test, measurement, R&D, and system integration.

The unit includes an AC adapter for ready-to-use convenience on the bench or in a system. All I/O connectors are SMA. The extruded aluminum housing is suitable for mounting with the optional brackets.

# \*SPECIFICATIONS ( $0^{\circ} C \le T_A \le 35^{\circ}C$ )

| SYMBOL                 | PARAMETER                                                     | Min            | Тур   | Max   | UNIT | Comments                                |

|------------------------|---------------------------------------------------------------|----------------|-------|-------|------|-----------------------------------------|

| R <sub>in</sub>        | External Clock Input Resistance                               |                | 50    |       | Ω    | AC Coupled                              |

| Cc                     | Input Coupling Capacitor                                      | 0.08           | 0.10  | 0.12  | uf   | Input TC=50 μs                          |

| IDC                    | DC Input Current                                              |                | +120/ | +135/ | mA   |                                         |

|                        |                                                               |                | -285  | -300  |      |                                         |

| V <sub>DC</sub>        | DC Input Voltage                                              | ±7.5           | ±8.5  | ±12   | V    |                                         |

| V <sub>AC</sub>        | AC/DC Adapter Input Voltage                                   | 103            | 115   | 127   | V    |                                         |

| V <sub>INmin</sub>     | Minimum p-p Input Amplitude                                   | 500            | 400   |       | mV   | Sine Wave@ f <sub>min</sub> In I        |

|                        |                                                               | 350            | 250   |       |      | Square Wave, t <sub>r</sub> <2 ns       |

|                        |                                                               | 100            | 50    |       |      | Square Wave, t <sub>r</sub> <500 ps     |

| V <sub>INmax</sub>     | Maximum p-p Input Amplitude                                   |                | 2.0   | 1.25  | V    | Sine or Square Wave                     |

| V <sub>OH</sub>        | Output Hi Level @ 100MHz                                      | -1.13          | -0.9  | -0.81 | V    | Output terminated to 50 $\Omega$ /-2 V  |

| V <sub>OL</sub>        | Output Lo Level @ 100MHz                                      | -1.95          | -1.6  | -1.48 | V    | Output terminated to 50 $\Omega$ /-2 V  |

| t <sub>PLH1</sub>      | Propagation Delay from Input to $\varphi 1$ output $\uparrow$ |                | 2500  |       | ps   |                                         |

| t <sub>PLH2</sub>      | Propagation Delay from Input to φ2 output ↑                   |                | 2500  |       | ps   |                                         |

| $t_r/t_f l$            | Rise/Fall Times (20%-80%), NECL outputs                       |                | 200   | 250   | ps   | Note (1)                                |

| t <sub>SKEW1</sub>     | Skew $\Leftrightarrow \varphi 1$ or $\varphi 2$ outputs       |                | 40    | 120   | ps   |                                         |

| t <sub>SKEW2</sub>     | Skew $\Leftrightarrow \varphi 1$ and $\varphi 2$ outputs      |                | 40    | 120   | ps   | D0/D1=10, D2/D3=00                      |

|                        | Peak to peak Jitter                                           |                | 5     | 10    | ps   |                                         |

| <sup>f</sup> min In I  | Minimum Input frequency                                       | 120            | 100   |       | MHz  | Sine Wave Input                         |

| <sup>f</sup> min In II | Minimum Input frequency                                       | 150            | 100   |       | KHz  | Square Wave Input, $t_r < 2 \text{ ns}$ |

| f <sub>max In</sub>    | Max Input clock frequency                                     | 6              | 6.6   |       | GHz  |                                         |

| fmax Out               | Max Output frequency                                          | 3              | 3.3   |       | GHz  | φ1 Outputs                              |

|                        |                                                               | 1.5            | 1.65  |       |      | φ2 Outputs                              |

|                        | Size                                                          | 1.3 x 2.9x 2.9 |       |       | in.  |                                         |

|                        | Weight                                                        | 10             |       |       | Oz   |                                         |

\*All dynamic NECL measurements are made with outputs terminated into 50  $\Omega$ /-2 V, using the PRL-550NQ4X, four-channel NECL Terminator, connected to a 50  $\Omega$  input sampling oscilloscope.

#### Notes:

(1) The output rise and fall times of each NECL channel are measured with its complementary output terminated into 50  $\Omega$ /-2 V. An unused complementary 50  $\Omega$  output must be either terminated into 50  $\Omega$ /-2 V or AC coupled into a 50  $\Omega$  load; otherwise, output waveform distortion and rise time degradation will occur. Use the PRL-ACT-50, Dual Ch. AC-Coupled 50  $\Omega$  Termination, for the AC coupled termination. Use the PRL-SC-104 or PRL-ACX-12dB (0.1 µf DC block and 12 dB AC-coupled attenuator, respectively) for connection of NECL signals to 50  $\Omega$  input oscilloscopes.