LZE GMBH • FRAUENWEIHERSTRASSE 15 • 91058 ERLANGEN

## FH3D04 SOFTWARE DEFINED QUAD 3D HALL SENSOR

## **DATASHEET**

DATE 21.11.2023

EDITION 1 REVISION 1.00

## **CHANGELOG**

| Date / Edition / Revision            | Changes         |

|--------------------------------------|-----------------|

| 21.11.2023, Edition 1, Revision 1.00 | Initial version |

|                                      |                 |

|                                      |                 |

|                                      |                 |

|                                      |                 |

Content

## 0 Content

| 0<br>1<br>1.1<br>1.2<br>1.3                                                                 | Content FH3D04 Overview General Description Block Diagram Customer Support.                                                                                                                                                                                                                                                       | 5<br>5                           |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2<br>2.1<br>2.2<br>2.3<br>2.4                                                               | Characteristics Operating Conditions Absolute Maximum Ratings (Non-Operating) Magnetic Specifications Current Consumption                                                                                                                                                                                                         | 9<br>9<br>10                     |

| 3<br>3.1<br>3.2<br>3.3                                                                      | Package and Circuit Connection Package and Dimension Pins Electrical Connection                                                                                                                                                                                                                                                   | 15<br>18                         |

| 4<br>4.1<br>4.2<br>4.3                                                                      | SPI Communication  Communication Interface                                                                                                                                                                                                                                                                                        | 22<br>25                         |

| 5<br>6<br>6.1<br>6.1.1<br>6.1.2<br>6.1.3                                                    | Register Map  Application Notes  First raw measurements with the basic configuration  Basic configuration  Measurement of Pixel 0, Sensor X, Gain 128, DecLen 512  Measurement of Pixel 1, Sensor Z, Gain 64, DecLen 512                                                                                                          | 40<br>40<br>41                   |

| 6.1.4<br>6.2<br>6.3<br>6.4<br>6.5<br>6.5.1                                                  | Measurement of the Temperature, with preheating of the next Sensor Pixel 0, Sensor X, Gain 128, DecLen 512  High speed measurement configuration using sequencer.  Magnetic resolution  Measurement time  Signal postprocessing  Temperature postprocessing                                                                       | 41<br>43<br>45<br>45             |

| 6.5.2<br>6.6<br>7                                                                           | Magnetic postprocessing  Determination of magnetic trim values using the integrated excitation coils  Digital Building Block                                                                                                                                                                                                      | 48                               |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9 | Communication Interface Control State Machine Sensor selection and analogue configuration Single phase measurement Automatic 4-phase measurement Automatic 2-phase measurement Background Temperature measurement Read Value Register 1 Parity to Register 100 Sequencer Number to Register 0x100 Range Warning to Register 0x100 | 51<br>52<br>54<br>54<br>55<br>55 |

| 7.3                                                                                         | Example of a Measuring Process                                                                                                                                                                                                                                                                                                    | 57                               |

### Content Offset Centering 57 Four Byte OTP......61 OTP read example 63 OTP programming example ......63 References .......64 Sensors 66 Sensor multiplexer 67 Offset-Centering .......74 System Clock 76

7.3.1

7.3.2

7.3.3

7.4

7.5

7.5.1

7.5.2

8

8.1

8.2

8.3 8.4

8.5

8.6

8.7

8.8

8.9

8.10

8.11

8.12

8.13

9

10

11 12

FH3D04 Overview

## 1

### FH3D04 Overview

### 1.1

### **General Description**

The FH3D04 is a quad 3D Hall sensor based on Fraunhofer HallinOne® technology. This versatile magnetic field sensor uses pure Hall effect principle without magnetizable materials.

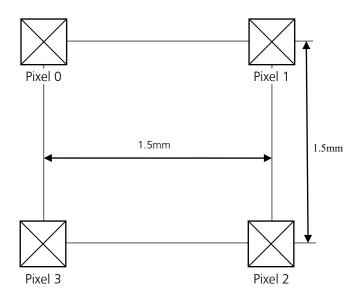

FH3D04 offers high dynamic magnetic range and accurate 3D magnetic field measurement at four positions arranged in a square with a pitch of 1.5 mm in a planar IC in a 2.5x2.5x0.6mm WLCSP package with 0.5mm solder ball pitch.

It can be used as a position sensor for linear (axial/orthogonal and axial/parallel) or angular (on-axis and off-axis) movement of permanent magnets, as a current sensor or as a magnetic field probe. Even 3D and up to 6D position measurement for joystick or gimbal applications are possible.

By use of several integrated 3D Hall sensors measurements stray field robust applications can be implemented.

Sensor placement: Four 3D Hall sensors (also called pixel cells) arranged in a square with a

pitch of 1.5 mm.

Temperature sensor for system-level drift tracking.

**Measurements:** Magnetic field value (X-, Y- or Z-direction) of the activated sensor or tem-

perature signal. Measurement range full scale from ~10 mT up to ~1.5 T. Measurement rate up to 80 kHz at 10 Bit or 1.8 kHz at 16 Bit resolution.

Software defined sensor: Each sensor element can be independently configured concerning meas-

urement range and rate. The measurement flow (active sensor elements and measurement order) is software defined, too. An OTP contains elec-

trical trim values,

Integrated excitation coil: Enables magnetic calibration without need for magnetic setup and mag-

netic self-test during operation.

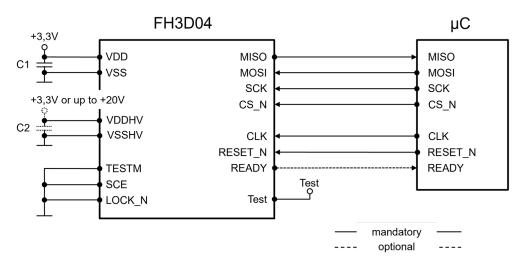

Communication interface: The ASSP offers a register based four wire SPI interface with the pins

MISO, MOSI, SCK, CS\_N and an optional READY signal. The maximum interface clock frequency is 16 MHz. Daisy Chain available on request.

**Digital state machine:** The digital state machine consists of

an automatic decimation of the sigma-delta based ADC values

shadow registers as memory for the output values for continuous operation

control for automatic spinning current measurement and offset centring

| FH3D04 Overview |

|-----------------|

- sequencer for measuring several sensors without reconfiguration

- diagnostic flags

During normal operation minimum the following functionality has to be implemented for example in an external microcontroller:

- initialization of the ASIC

- sequential control of the measurements (measure x, y, z and temperature) or just readout of sequencer result values

- signal processing

- o sensitivity compensation over temperature

- o offset compensation over temperature

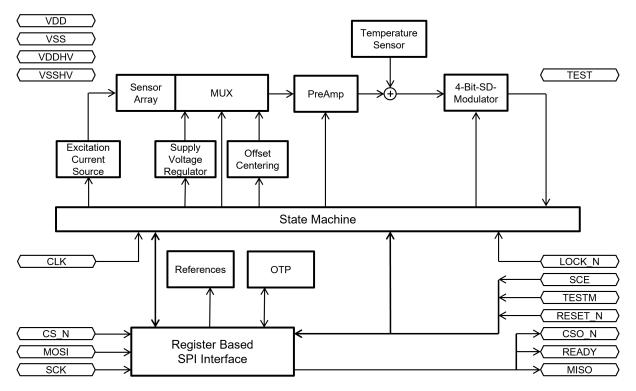

## 1.2 Block Diagram

The chip consists of four 3D Hall sensors, an excitation coil and its high voltage current source, the analogue signal computation channel with programmable gain amplifier plus offset centering,  $\Sigma\Delta$ -Modulator and a decimation register. The state machine controls the sequencer, decimation, offset centering and the 4-phase measurement cycle. The system clock has to be fed in by a dedicated CLK pad.

Figure 1: Block diagram

| FH3D04 Overview |  |

|-----------------|--|

## 1.3 Customer Support

For questions and troubleshooting please contact the customer support:

Email: contact@lze-innovation.de

## 2 Characteristics

# 2.1 Operating Conditions

Table 1: Operating conditions

| Parameter                     | Min. | Тур. | Max. | Unit |

|-------------------------------|------|------|------|------|

| Ambient temperature           | -40  | 25   | 125  | °C   |

| VDD                           | 3.0  | 3.3  | 3.6  | V    |

| VDDHV during routine test     |      | 20   |      | V    |

| VDDHV during normal operation | 3.0  | 3.3  | 3.6  | V    |

# 2.2 Absolute Maximum Ratings (Non-Operating)

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability (eq. hot carrier degradation).

Table 2: Absolute Maximum Ratings

| Parameter                | Symbol | Min. | Max.    | Unit |                                |

|--------------------------|--------|------|---------|------|--------------------------------|

| DC supply voltage        | VDD    | -0.3 | 7.0     | V    |                                |

| DC supply voltage        | VDDHV  | -0.3 | 22      | V    |                                |

| Input pin voltage        | V_in   | -0.3 | VDD+0.3 | V    |                                |

| Input current on any pin | I_in   | -100 | 100     | mA   | Norm: JEDEC78                  |

| Storage Temperature      | T_strg | -55  | 125     | °C   |                                |

| Humidity                 |        | 5    | 85      | %    | Non-condensing                 |

| Electrostatic discharge  | ESD    | +/-2 |         | kV   | Norm: MIL 883 E<br>method 3015 |

| Soldering Conditions     | T_lead |      |         |      | Norm: IEC 61760-1              |

| Characteristics |  |

|-----------------|--|

### 2.3

## Magnetic Specifications

As the chip has no memory for magnetic compensation values it is not magnetically trimmed during the final test, so the raw measurements have huge tolerances.

As described in chapter 6.6 the integrated test circuits can be used to measure the magnetic trim values on module level. With this information and the signal processing described in chapter 6.5 accurate measurements can be done.

Both magnetic specifications for raw values and for on chip calibrated and postprocessed values are given in the following tables.

The min., typ. and max. values are based on a small number of samples from one engineering lot, measured with 3.3 V supply, offset centring regulation settled, OCToggle set to low. Unless otherwise noted  $25^{\circ}$ C. Drift values are with respect to  $25^{\circ}$ C.  $1\sigma$  values are measured while  $5\sigma$  values are calculated.

Table 3: Magnetic Specifications: Basic configuration with signal processing on microcontroller and on chip magnetic trimming.

| Parameter                            | Symbol  | Min.  | Тур.  | Max.  | Unit   | Note                     |

|--------------------------------------|---------|-------|-------|-------|--------|--------------------------|

| Magnetic field range XY              | BmaxXY  | -88   |       | 88    | mT     | -40°C 125°C<br>5σ value  |

|                                      |         | -131  |       | 131   | mT     | 5 <b>σ</b> value         |

| Magnetic field range Z               | BmaxZ   | -131  |       | 131   | mT     | -40°C 125°C<br>5σ value  |

|                                      |         | -172  |       | 172   | mT     | 5 <b>σ</b> value         |

| Magnetic sensitivity XY              | SXY     | 99.7  | 100.0 | 100.4 | LSB/mT | $1\sigma = 0.173$        |

| Magnetic sensitivity Z               | SZ      | 99.8  | 100.0 | 100.3 | LSB/mT | $1\sigma = 0.136$        |

| Magnetic resolution XY               |         |       | 10.0  |       | μT/LSB |                          |

| Magnetic resolution Z                |         |       | 10.0  |       | μT/LSB |                          |

| Sensitivity drift X, Y               |         | -0.8  | 0.0   | 0.8   | %      | -40°C 125°C<br>1σ = 0.43 |

| Sensitivity drift Z                  |         | -0.9  | 0.0   | 1.1   | %      | -40°C 125°C<br>1σ = 0.55 |

| Sensitivity matching X/Y             |         | 99.5  | 100   | 100.4 | %      | -40°C 125°C<br>1σ = 0.17 |

| Sensitivity matching XorY/Z          |         | 99.7  | 100   | 100.3 | %      | $1\sigma = 0.12$         |

| Sensitivity matching drift<br>XorY/Z |         | -0.6  |       | 1.0   |        | -40°C 125°C              |

| Orthogonality X/Y                    |         | 89.6  | 90.1  | 90.6  | 0      | $1\sigma = 0.26$         |

| Orthogonality Z2X or Z2Y             |         | 89.6  | 89.9  | 90.2  | 0      | $1\sigma = 0.13$         |

| Magnetic offset XY                   | BoffsXY | 0.0   | 0.0   | 0.0   | mT     | (1)                      |

| Magnetic offset Z                    | BoffsZ  | 0.0   | 0.0   | 0.0   | mT     | (1)                      |

| Magnetic offset drift XY             |         | -0.38 | 0.0   | 0.29  | mT     | -40°C 125°C<br>1σ = 0.27 |

| Magnetic offset drift Z              |         | -0.09 | 0.0   | 0.01  | mT     | -40°C 125°C<br>1σ = 0.02 |

| 1σ Noise XY                          |         |       | 11.6  |       | μΤ     |                          |

| 1σ Noise Z                           |         |       | 9.9   |       | μΤ     |                          |

Basic configuration: GainXY =128, GainZ = 64, UD = 2.6 V. (1) After offset adjustment. Take care of the geomagnetic field!

Table 4: Magnetic Specifications: Raw Values with basic configuration

| Parameter                            | Symbol  | Min.  | Тур.   | Max.   | Unit       | Note                     |

|--------------------------------------|---------|-------|--------|--------|------------|--------------------------|

| Magnetic field range XY              | BmaxXY  | -88   |        | 88     | mT         | -40°C 125°C<br>5σ value  |

|                                      |         | -131  |        | 131    | mT         | 5σ value                 |

| Magnetic field range Z               | BmaxZ   | -131  |        | 131    | mT         | -40°C 125°C<br>5σ value  |

|                                      |         | -172  |        | 172    | mT         | 5σ value                 |

| Magnetic sensitivity XY              | SXY     | 95.4  | 97.4   | 100.5  | LSB/mT     | 1σ = 1.6                 |

| Magnetic sensitivity Z               | SZ      | 90.9  | 92.8   | 94.4   | LSB/mT     | 1σ = 1.4                 |

| Magnetic resolution XY               |         |       | 10.27  |        | μT/LSB     |                          |

| Magnetic resolution Z                |         |       | 10.78  |        | μT/LSB     |                          |

| Sensitivity drift XY                 |         | -39.8 |        | 44.9   | %          | -40°C 125°C              |

| Sensitivity drift Z                  |         | -37.7 |        | 40.2   | %          | -40°C 125°C              |

| Sensitivity matching X/Y             |         | 99.88 | 100.07 | 100.28 | %          | -40°C 125°C<br>1σ = 0.09 |

| Sensitivity matching XorY/Z          |         | 51.7  | 52.2   | 53.2   | %          | $1\sigma = 0.5$          |

| Sensitivity matching drift<br>XorY/Z |         | -4.3  |        | 2.8    | %          |                          |

| Orthogonality X/Y                    |         | 89.6  | 90.1   | 90.6   | 0          | $1\sigma = 0.29$         |

| Orthogonality Z/X Z/Y                |         | 90.5  | 92.0   | 93.0   | %          | $1\sigma = 0.71$         |

| Magnetic offset XY                   | BoffsXY | -5.2  | -0.5   | 3.7    | mT         | $1\sigma = 3.05$         |

| Magnetic offset Z                    | BoffsZ  | -0.17 | -0.0   | 0.14   | mT         | $1\sigma = 0.09$         |

| Magnetic offset drift XY             |         | -1.60 | 0.02   | 1.95   | mT         | -40°C 125°C<br>1σ = 1.09 |

| Magnetic offset drift Z              |         | -0.07 | 0.00   | 0.06   | mT         | -40°C 125°C<br>1σ = 0.03 |

| 1σ Noise XY                          |         |       | 11.6   |        | μΤ         |                          |

| 1σ Noise Z                           |         |       | 9.9    |        | <u>μ</u> Τ |                          |

Table 5: Magnetic Specifications: Small measurement range, raw values

| Parameter               | Symbol | Min.  | Тур.  | Max.   | Unit   | Note                    |

|-------------------------|--------|-------|-------|--------|--------|-------------------------|

| Magnetic field range XY | BmaxXY | -9.1  |       | 9.1    | mT     | -40°C 125°C<br>5σ value |

|                         |        | -17.7 |       | 17.7   | mT     | 5σ value                |

| Magnetic field range Z  | BmaxZ  | -11.2 |       | 11.2   | mT     | -40°C 125°C<br>5σ value |

|                         |        | -14.7 |       | 14.7   | mT     | 5σ value                |

| Magnetic sensitivity XY | SXY    | 193.2 |       | 620    | LSB/mT | -40°C 125°C<br>5σ value |

|                         |        | 321.0 | 377.8 | 434.5  | LSB/mT | 5σ value                |

| Magnetic sensitivity Z  | SZ     | 358.2 |       | 1011.5 | LSB/mT | -40°C 125°C<br>5σ value |

|                         |        | 543.5 | 659.5 | 775.5  | LSB/mT | 5σ value                |

Small measurement range configuration: GainXY = 512, Gain Z = 512, UD = 2.6 V

Table 6: Magnetic Specifications: High measurement range, raw values

| Parameter               | Symbol | Min.  | Тур. | Max. | Unit   | Note                            |

|-------------------------|--------|-------|------|------|--------|---------------------------------|

| Magnetic field range XY | BmaxXY | -1.76 |      | 1.76 | Т      | -40°C 125°C<br>5 <b>σ</b> value |

|                         |        | -2.50 |      | 2.50 | Т      | 5σ value                        |

| Magnetic field range Z  | BmaxZ  | -2.19 |      | 2.19 | Т      | 40°C 125°C<br>5 <b>σ</b> value  |

|                         |        | -2.87 |      | 2.87 | T      | 5σ value                        |

| Magnetic sensitivity XY | SXY    | 3.02  |      | 9.79 | LSB/mT | -40°C 125°C<br>5 <b>σ</b> value |

|                         |        | 5.02  | 5.90 | 6.79 | LSB/mT | 5σ value                        |

| Magnetic sensitivity Z  | SZ     | 2.80  |      | 7.90 | LSB/mT | -40°C 125°C<br>5 <b>σ</b> value |

|                         |        | 4.24  | 5.15 | 6.06 | LSB/mT | 5σ value                        |

High measurement range configuration: GainXY = 64, GainZ = 32, UD = 0.325 V

|                 | <br> |  |

|-----------------|------|--|

| Characteristics |      |  |

## 2.4 **Current Consumption**

Table 7: Current Consumption

| Parameter                | Symbol        | Min. | Тур. | Max. | Unit | Note      |

|--------------------------|---------------|------|------|------|------|-----------|

| IDD during measurements  | $IDD_{meas}$  |      | 11.0 | 15.0 | mA   | (1, 2, 3) |

| IDD all analog blocks PD | $IDD_{reset}$ |      | 0.25 | 0.5  | mA   | (1, 2)    |

| IDD analog PD, clk off   | $IDD_{PD}$    |      | 1    | 20   | μΑ   | (1, 2)    |

- (1) Output currents in I/O pins are not included.(2) Values are DC mean currents.(3) Low IDD version available on request

# 3 Package and Circuit Connection

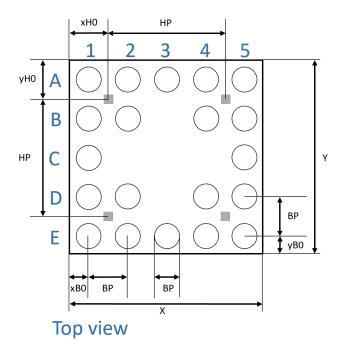

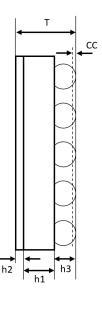

# 3.1 Package and Dimension

$2.5 \times 2.5 \times 0.6$  mm WLCSP with 0.5 mm ball pitch.

Side view

Figure 2: Package Drawing

Table 8: Package Dimensions

| Parameter                     | Symbol   | Value     | Unit | Note |

|-------------------------------|----------|-----------|------|------|

| Hall Sensor Pitch             | HP       | 1500      | μm   |      |

| Hall Sensor to chip edge      | xH0, yH0 | 507.5     | μm   |      |

| Chip length                   | Χ        | 2515 ± 20 | μm   |      |

| Chip width                    | Υ        | 2515 ± 20 | μm   |      |

| Chip thickness                | T        | 600±30    | μm   |      |

| Distance chip border to bumps | xB0, yB0 | 257.5     | μm   |      |

| Bump pitch                    | BP       | 500       | μm   |      |

| Wafer thickness               | h1       | 346±15    | μm   |      |

| Backside Laminate             | h2       | 22±5      | μm   |      |

| Bump height                   | h3       | 232±23    | μm   |      |

| Solder Ball Coplanarity       | CC       | 40        | μm   |      |

| Bump diameter                 | BD       | 329±20    | μm   |      |

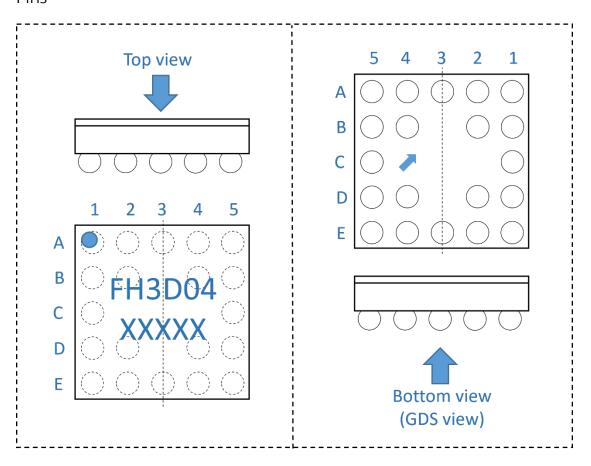

Table 9: Pads and pad positions

| Pad | Name    | Pad po  | osition | Protection to |

|-----|---------|---------|---------|---------------|

|     |         | X       | Υ       |               |

| A3  | VDD     | 1410.00 | 2266.00 | VSS           |

| A2  | VSS     | 1560.00 | 2266.00 | VDD           |

| E4  | VDDHV   | 897.65  | 176.95  | VSSHV         |

| E3  | VSSHV   | 1162.55 | 176.95  | VDDHV         |

| A1  | LOCK_N  | 2266.00 | 2248.80 | VDD/VSS       |

| E1  | RESET_N | 2266.00 | 221.20  | VDD/VSS       |

| A4  | READY   | 204.00  | 2040.60 | VDD/VSS       |

| A5  | MISO    | 204.00  | 2248.80 | VDD/VSS       |

| B5  | MOSI    | 204.00  | 1832.40 | VDD/VSS       |

| E5  | CLK     | 204.00  | 221.20  | VDD/VSS       |

| C5  | SCK     | 204.00  | 429.40  | VDD/VSS       |

| B2  | SCE     | 2266.00 | 2040.60 | VDD/VSS       |

| E2  | TESTM   | 2266.00 | 429.40  | VDD/VSS       |

| D1  | CS_N    | 2266.00 | 691.90  | VDD/VSS       |

| D5  | CSO_N   | 204.00  | 637.60  | VDD/VSS       |

| B1  | TEST    | 2266.00 | 1883.30 | VDD/VSS       |

Reference position for x- and y- positions is the lower left chip edge.

The chip size is  $2470\mu m\ x\ 2470\mu m$  between the scribe outer edges.

Table 10: PCB land pad diameter recommendation

| Description                   | Value | Unit | Note |

|-------------------------------|-------|------|------|

| Non-soldermask defined (NSMD) | 270   | μm   |      |

| Soldermask defined (SMD)      | 300   | μm   |      |

Figure 3: Top and bottom view WLCSP

| LOCK_N        | VSS     | VDD   | READY   | MISO      |

|---------------|---------|-------|---------|-----------|

| A1            | A2      | A3    | A4      | A5        |

| TEST          | SCE     |       | PIN2.NC | MOSI      |

| B1            | B2      |       | B4      | B5        |

| PIN1.NC<br>C1 |         |       |         | SCK<br>C5 |

| CS_N          | PIN3.NC |       | PIN4.NC | CSO_N     |

| D1            | D2      |       | D4      | D5        |

| RESET_N       | TEST_M  | VSSHV | VDDHV   | CLK       |

| E1            | E2      | E3    | E4      | E5        |

Figure 4: Top view pinout

Table 11: Pin description

| Pin | Name    | Pad         | Description                                                       |

|-----|---------|-------------|-------------------------------------------------------------------|

| A1  | LOCK_N  | Digital In  | Lock, must be connected to VSS                                    |

| A2  | VSS     | Supply      | Ground (0 V)                                                      |

| A3  | VDD     | Supply      | Supply voltage 3.3 V                                              |

| A4  | READY   | Digital Out | Measurement ready signal                                          |

| A5  | MISO    | Digital Out | Master in / Slave out (SPI output)                                |

| B1  | TEST    | Analog Out  | Test pin                                                          |

| B2  | SCE     | Digital In  | Scan test enable, must be connected to VSS                        |

| B5  | MOSI    | Digital In  | Master out Slave in (SPI input)                                   |

| C5  | SCK     | Digital In  | SPI Interface clock                                               |

| D1  | CS_N    | Digital In  | Chip Select (low-active)                                          |

| D5  | CSO_N   | Digital Out | Chip Select Output (low-active),<br>available on customer request |

| E1  | RESET_N | Digital In  | Reset                                                             |

| E2  | TESTM   | Digital In  | Test Mode, must be connected to VSS                               |

| E3  | VSSHV   | Supply      | Ground (0 V)                                                      |

| E4  | VDDHV   | Supply      | Supply voltage (3.3 V or 20 V for routine tests)                  |

| E5  | CLK     | Digital In  | System clock (8 MHz)                                              |

The digital input pins have Schmitt-trigger functionality. The outputs are slew rate controlled CMOS drivers. The corresponding levels are shown in this table and are valid for a junction temperature range of -40 ...125°C.

Table 12: Pin input and output levels

| Name                           | Min. | Max. | Unit | Comment                 |

|--------------------------------|------|------|------|-------------------------|

| Input negative going threshold | 1.12 | 1.27 | V    | VDD=3.0V                |

| Input negative going threshold | 1.42 | 1.52 | V    | VDD=3.6V                |

| Input positive going threshold | 1.77 | 1.87 | V    | VDD=3.0V                |

| Input positive going threshold | 2.07 | 2.23 | V    | VDD=3.6V                |

| Output low level               | 0    | 0.4  | V    | 8mA load<br>(MISO 16mA) |

| Output high level              | 2.5  | VDD  | V    | 8mA load<br>(MISO 16mA) |

CS\_N as low active chip select signal activates receiving and sending of interface data. If only a single chip is used, CS\_N can remain 'low'. All interface data is synchronized internally and transferred after 16 SCK cycles.

The system clock CLK only toggles the state machine and ADC. It can be run at a maximum frequency of 8 MHz.

## 3.3 Electrical Connection

The sensor chip must be connected to a supply of 3.3 V via its VDD and VSS pins.

The integrated coils may be connected to 3.3 V or up to 20 V depending on the application. If the integrated coils should be used to measure the sensitivity during the final module test in a short time, VDDHV should be connected to 20 V. If the integrated coils should be used to monitor the sensors functionality the integrated coils can be connected to 3.3 V. All unused input pins should be connected to VSS to guarantee proper function. Decoupling capacitors between VDD and VSS as well as between VHHDV and VSSHV close to the sensor chip are strongly recommended. For communication of a single sensor with a microcontroller, all four SPI signals CS\_N, SCK, MOSI and MISO have to be connected. After power up, a proper reset cycle of the sensor chip has to be executed. Pin READY can be used to detect a finished measurement.

Figure 5: Typical electrical connection

Recommended additional components:

C1: Non-magnetic capacitor near pins (100 nF)

Optional components:

C2: Non-magnetic capacitor near pins (100 nF)

#### Please note:

It is strongly recommended to use a PCB with wide bandwidth, low impedance supply layer system and impedance controlled digital signal lines with matching series resistors to the hardware setup. A stable supply and clean signals are mandatory for low sensor noise and faultless communication at high SPI frequency.

SPI Communication

### 4

### **SPI** Communication

### 4.1

### Communication Interface

The serial interface samples the information at MOSI with the rising edge of SCK.

The output bits at MISO are updated with every falling SCK edge. MISO is only activated if CS\_N is low. Otherwise the output is hi-Z. This allows for parallel operation of multiple ICs.

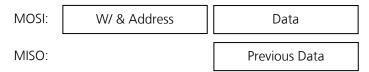

Two different access modes are possible. A 16 bit word can be written to a certain address or a 16 bit word can be read. The MSB of the address word (A<15>) decides about reading or writing the data.

A<15> = 0 (read measurement data / RAM) A<15> = 1 (write parameter / RAM)

### Writing:

For writing a word into a register the appropriate address and the write/read bit must be written to the interface. The interface counter counts the SCK cycles and detects the end of the address word and the beginning and end of the data word. Therefore the chip select (CS\_N) can be set to 'low' and does not need to be controlled.

During the write access the current data in the addressed register is written to MISO. Using this, the interface register behaves like a 32-bit shift register. The chip select does not affect the register but controls the transfer of data only.

### Reading:

For reading a register the address with A<15> = 0 is written to the interface. After 16 SCK cycles the actual reading starts.

During clocking out the data from a register at MISO, the bits at MOSI are interpreted as new R/W command and address.

MOSI: R/ & Address R/ & Address R/ & Address

MISO: Data Data

Figure 6: Reading mode

#### Failure detection:

For detection of communication errors, the current value of a register can be read back at the same time as new data is written to it.

| SPI | Communication |  |

|-----|---------------|--|

During a write access first the address is transmitted. After the address is written, the interface can read the content of this register and prepare for read back. During writing the new data and finalizing the transmission, the old register content is available at the MISO pin. The controller can verify the old register content.

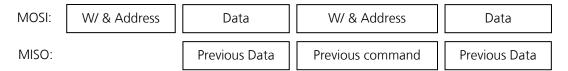

Figure 7: Writing mode

With this function it is possible to check the connection between ASIC and controller as well as the content of the concerning register.

After a write command transfer is complete, the complete transfer data is present at MISO during the next transfer phase. The correct communication can be verified here.

Figure 8: Command verification

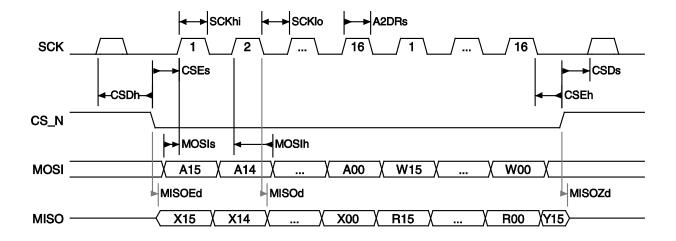

### SPI synchronization:

While usually CS\_N can stay active (low) over many periods of word transfers, it may happen in harsh environments, that spikes on the SCK signal disturb internal synchronization of the slave's interface to the master's one. In such cases the CS\_N signal can be set to high in order to reset the internal SCK counter. Thus, synchronization of master and slave can be restored.

Figure 9: SPI timing

Table 13: SPI timing values

| Parameter                           | Symbol                         | Min.      | Тур.  | Max. | Unit | Note |

|-------------------------------------|--------------------------------|-----------|-------|------|------|------|

| External CLK frequency              | $f_{CLK}$                      | 7.95<br>0 | 8     | 8.05 | MHz  |      |

| External CLK pulswidth HI           | $t_{\sf CLKhi}$                | 62        | 62.5  | 63   | ns   |      |

| External CLK pulswidth LO           | $t_{\text{CLKlo}}$             | 62        | 62.5  | 63   | ns   |      |

| External CLK duty cycle             | $D_{CLK}$                      | 49        | 50    | 51   | %    |      |

| SCK frequency<br>Standard registers | f <sub>sck</sub>               | 0         |       | 16   | MHz  | (1)  |

| SCK pulswidth HI                    | t <sub>scKhi</sub>             | 30        | 31.25 |      | ns   |      |

| SCK pulswidth LO                    | t <sub>scKlo</sub>             | 30        |       |      | ns   |      |

| CS_N enable setup time before SCK   | $t_{\scriptscriptstyle{CSEs}}$ | 10        |       |      | ns   |      |

| CS_N enable hold time after SCK     | $t_{\scriptscriptstyleCSEh}$   | 10        |       |      | ns   |      |

| CS_N disable setup time before SCK  | t <sub>CSDs</sub>              | 10        |       |      | ns   |      |

| CS_N disable hold time after SCK    | $t_{CSDh}$                     | 10        |       |      | ns   |      |

| MOSI setup time before SCK          | t <sub>MOSIs</sub>             | 10        |       |      | ns   |      |

| MOSI hold time after SCK            | t <sub>MOSIh</sub>             | 10        |       |      | ns   |      |

| MISO delay after SCK                | t <sub>MISOd</sub>             |           |       | 10   | ns   |      |

| MISO enable delay after CS_N        | t <sub>MISOEd</sub>            |           |       | 20   | ns   |      |

| MISO high Z delay after CS_N        | t <sub>MISOZd</sub>            |           |       | 20   | ns   |      |

| Output edge rise time               | t <sub>Or</sub>                |           | 3     | 8    | ns   |      |

| Output edge fall time               | t <sub>Of</sub>                |           | 3     | 8    | ns   |      |

Typical values are given for 25°C. Output load of MISO is 100 pF, other outputs 25 pF. (1) must not exceed  $8 \cdot f_{\text{CLK}}$

### 4.2

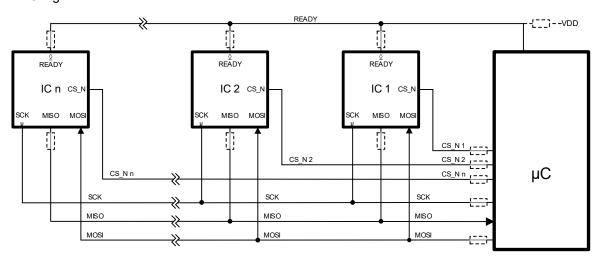

### Multiple CS\_N Parallel Operation

FH3D04 is optimized for being stitched to lines or areas with 1.5 mm pixel distance. The simplest way to communicate with several ICs for combined operation is to use separate CS\_N wires for every device. Communication with a device is only possible while CS\_N is low. Then the output MISO is active, otherwise it is high impedance.

It then is important that only one CS\_N signal is active at a time to avoid shorts and thus distortions on the MISO signal.

Figure 10: Example for configuration with several FH3D04 devices and one master controller in chip select mode.

In combination with an external pull up resistor to the supply voltage (VDD) the READY output can be configured to act as an open drain output such that a wired and combination of all READY signals clearly indicates the end of every measurement in all devices.

If the routings between the devices are long, a series resistor close to the driving output is recommended to avoid (or at least suppress) distortions due to reflections in the lines at the receiving devices (see dashed resistors).

## 4.3

## Adressed Parallel Operation

In parallel operation Daisy Chain is only available on customer request, but addressing is available and ensures comfortable selection of single FH3D04 without CS\_N low/high operations after initialization (e.g. for DMA driven data transfers).

During initialization to a via CS\_N low selected FH3D04 an address can be assigned by using SPI address 0x009. If all parallel FH3D04 have an address all CS\_N can stay low and a device can be addressed and activated by using SPI address 0x00A. The register content is described in the following tables.

SPI Communication

Table 14: Register 0x009 bit assignment

| Bitpos. | Signal     | Meaning               |

|---------|------------|-----------------------|

| 15-8    | OwnAddrGrp | Set own group address |

| 7-0     | OwnAddr    | Set own address       |

Table 15: Register 0x00A bit assignment

| Bitpos. | Signal  | Meaning                            |

|---------|---------|------------------------------------|

| 15-8    | AddrGrp | Chip select with own group address |

| 7-0     | Addr    | Chip select with own address       |

For operating a system in such a configuration it is necessary to assign a unique OwnAddr to every device before it can be addressed. The following sections describe the necessary procedures.

### **Distributing OwnAddr Values**

Distributing the addresses to several devices on the same SPI is possible by selecting the single device via  $CS_N$  low. After setting an  $OwnAddr \neq 0$  the active device will be deactivated.

### Addressing

Holding all available CS\_Ns low and writing an address into register 0x00A via SPI activates only the chip whose OwnAddr<7:0> is identical to the written Addr<7:0>. CS\_N must be low during the write command. ICs whose OwnAddr is not identical are deactivated. In this way it is possible to switch from one already addressed chip to another by a single write command to address 0x00A.

## 5 Register Map

Following tables show all available registers for communication with the sensor via SIP.

After a reset the electrical trim values have to be read out of OTP via registers 0x050 and 0x051 and configuration registers 0x002 to 0x040 have to be written once. Measurements can be started using register 0x001. The measured values can be read from register 0x100, while 0x102 contains status bits. A read operation from register 0x100 deletes the ready bit.

Table 16: Register 0x001 content

| Bitpos. | Signal        | Width | Meaning                                                                                                                                    |

|---------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 15-13   | AmpGain<2:0>  | 3     | Amplifier Gain 0=32, 1=64, 2=128, 3=256, 4=512, 5=1024, 6 and 7 is not allowed                                                             |

| 12      | TempSel       | 1     | Temperature Select                                                                                                                         |

| 11-10   | PixelSel<1:0> | 2     | Pixel Select<br>0: upper left 3D Hall sensor, 1: upper right 3D Hall sensor<br>2: lower right 3D Hall sensor, 3: lower left 3D Hall sensor |

| 9-8     | SensSel<1:0>  | 2     | Sensor Select<br><1:0> : Sensor: 0 = X, 1 = Y, 2 = Z,<br>3 = Hall sensor off                                                               |

| 7-1     | DecLen<7:1>   | 7     | Decimation Length lower bits DecLen<0> is always 0 If DecLen<10:1> is 0 DecLen = 1                                                         |

| 0       | DecEn         | 1     | Decimation Enable                                                                                                                          |

To start a measurement with basic configuration using register 0x001 write via SPI transfer: **8001h – ??01h** Pixel ?, Sensor ?, Gain ?, DecLen<10:8> +0

Table 17: Register 0x002 content

| Bitpos. | Signal       | Width | Meaning                                                         |

|---------|--------------|-------|-----------------------------------------------------------------|

| 15-13   | AmpComp<2:0> | 3     | Amplifier Compensation 7 = auto compensation                    |

| 12      | Fast2P       | 1     | Fast two phase SC                                               |

| 11      | SMUXChopInv  | 1     | Sensor MUX Chopper Invert                                       |

| 10-8    | DecLen<10:8> | 3     | Decimation Length upper bits<br>If DecLen<10:1> is 0 DecLen = 1 |

| 7-0     | DecWait<7:0> | 8     | Decimation Wait, has to be at least 3                           |

For basic configuration of register 0x002 write via SPI transfer:

8002h - E250h

AmpComp: 7; DecLen: 2\*256+(DecLen<7:1>\*2); DecWait: 80

Table 18: Register 0x003 content

| Bitpos. | Signal        | Width | Meaning                                                                                                                                                                                                          |

|---------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-13   | SRegDVal<2:0> | 3     | Sensor Regulator Difference Value<br>0 = 0.325V, 1 = 0.65V, 2 = 1.3V<br>3 = 2.0V, 5 = 2.6V, 6 = 2.8V                                                                                                             |

| 12-10   | SRegNVal<2:0> | 3     | Sensor Regulator Negative Value<br>0 = 0.2V, 2 = 0.5V, 3 = 0.65V<br>5 = 0.95V, 6 = 1.1V                                                                                                                          |

| 9-6     | ECCSel<3:0>   | 4     | "Excitation Current Coil Select" Activates the calibration coil. 0: coils off 1: P2 XY 2: P2 Q 3: P2 Z + P1 H 4: P2 H + P1 Z 5: P1 Q 6: P1 XY 7: P3 XY 8: P3 Q 9: P3 Z + P0 H 10: P3 H + P0 Z 11: P0 Q 12: P0 XY |

| 5-3     | ECVal<2:0>    | 3     | Excitation Current Value                                                                                                                                                                                         |

| 2       | ECSign        | 1     | Excitation Current Sign                                                                                                                                                                                          |

| 1-0     | Phase<1:0>    | 2     | Phase                                                                                                                                                                                                            |

For basic configuration of register 0x003 write via SPI transfer:

8003h - A000h

SRegDVal:5 = 2.6 V; SRegNVal:0 = 0.2 V

Table 19: Register 0x004 content

| Bitpos. | Signal      | Width | Meaning                                                                                                  |

|---------|-------------|-------|----------------------------------------------------------------------------------------------------------|

| 15      | Reserved    | 1     | Reserved set to zero                                                                                     |

| 14      | ModOpM      | 1     | Modulator Operating Mode                                                                                 |

| 13      | ECEnHV      | 1     | Excitation Current Enable High Voltage<br>0: 0.2mA per Digit (EC_Val+1)<br>1: 1.4mA per Digit (EC_Val+1) |

| 12-9    | Auto4P<3:0> | 4     | Auto4P                                                                                                   |

| 8       | OCSign      | 1     | Offset Centering Sign                                                                                    |

| 7-6     | OCMode<1:0> | 2     | Offset Centering Mode<br>Typical: 0b10                                                                   |

| 5       | OCAuto      | 1     | Auto Centering                                                                                           |

| 4       | OCIRefR     | 1     | Offset Centering Current Reference Resistor                                                              |

| 3       | OCToggle    | 1     | Offset Centering Toggle                                                                                  |

| 2-0     | OCGain<2:0> | 3     | Offset Centering Gain                                                                                    |

For basic configuration of register 0x004 write via SPI transfer:

8004h - 0AA9h

Auto4P:0101b; OCMode:10b; OCAuto; OCToggle; OCGain: 001b

Table 20 Register 0x005 content

| Bitpos. | Signal        | Width | Meaning                                     |

|---------|---------------|-------|---------------------------------------------|

| 15-6    | Reserved      | 10    | Reserved set to zero                        |

| 5       | Rng2Reg100    | 1     | Write the range warning bit in register 100 |

| 4       | SeqNr2Reg100  | 1     | Write the sequencer number in register 100  |

| 3       | Parity2Reg100 | 1     | Write the parity bit in register 100        |

| 2-1     | RM<1:0>       | 2     | Ready Mode                                  |

| 0       | RVR1          | 1     | Read Value Register 1                       |

For basic configuration of register 0x005 write via SPI transfer: **8004h – 0002h** RM: 1

Table 21: Register 0x006 content

| Bitpos. | Signal       | Width | Meaning                             |

|---------|--------------|-------|-------------------------------------|

| 15-11   | Reserved     | 5     | Reserved set to zero                |

| 10      | OC_PO        | 1     | Offset Centering PO                 |

| 9       | ModRefBuf_PO | 1     | Modulator Reference Buffer Power On |

| 8       | Buf_PO       | 1     | Buffer Power On                     |

| 7       | EC_PO        | 1     | Excitation Current Power On         |

| 6       | Bias_PO      | 1     | Bias Power On                       |

| 5       | Mod_PO       | 1     | Modulator Power On                  |

| 4       | Amp_PO       | 1     | Amplifier Power On                  |

| 3       | SRegN_PO     | 1     | Sensor Regulator N Power On         |

| 2       | SRegD_PO     | 1     | Sensor Regulator D Power On         |

| 1       | SMUXPowerEn  | 1     | Sensor Modulator Power Enable       |

| 0       | SMUXSigEn    | 1     | Sensor Mux Signal Enable            |

For basic configuration of register 0x004 write via SPI transfer: **8006h – 077Fh** all PO except EC\_PO; SMUXPowEn;

Table 22: Register 0x007 content

| Bitpos. | Signal   | Width | Meaning               |

|---------|----------|-------|-----------------------|

| 15-0    | Reserved | 16    | Reserved, has to be 0 |

For basic configuration of register 0x007 no action is needed.

Table 23: Register 0x008 content

| Bitpos. | Signal       | Width | Meaning                                                                                                                                       |

|---------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | SConstI_PO   | 1     | "Sensor Constant Current PowerOn"                                                                                                             |

| 14      | SIMeasEn     | 1     | "Sensor Current Measurement Enable"<br>0: Temperature measurement<br>1: Current measurement                                                   |

| 13      | SIMeas_PO    | 1     | "Sensor Current Measurement Power On" Switch on the current measurement.                                                                      |

| 12-6    | lbBoost<6:0> | 7     | I Bias Boost <6> IbBoostEC <5> IbBoostAmp <4> IbBoostBuf <3> IbBoostSupReg <2> IbBoostMod <1> IbBoostRefBuf <0> IbBoostOC                     |

| 5-4     | ICTEn<1:0>   | 2     | In-Circuit-TestEnable <1> Disconnect Test4/3 from GND and connect is to the pads. <0> Disconnect Test2/1 from GND and connect is to the pads. |

| 3       | ICTUP        | 1     | In-Circuit-Test UP Switch positive sensor supply voltage to <i>TEST.</i> ICTEn<0> has to be set.                                              |

| 2       | ICTUN        | 1     | In-Circuit-Test UN Switch negative sensor supply voltage to TEST. ICTEn<0> has to be set.                                                     |

| 1       | ICTIb        | 1     | In-Circuit-Test lb Switch 10uA reference current to TEST. ICTEn<0> has to be set.                                                             |

| 0       | ICTURef      | 1     | In-Circuit-Test URef<br>Switch bandgap reference voltage to <i>TEST.</i><br>ICTEn<0> has to be set.                                           |

For basic configuration of register 0x008 no action is needed.

Table 24: Register 0x009 content

| Bitpos. | Signal     | Width | Meaning               |

|---------|------------|-------|-----------------------|

| 15-8    | OwnAddrGrp | 8     | Set own group address |

| 7-0     | OwnAddr    | 8     | Set own address       |

For basic configuration of register 0x009 no action is needed.

Table 25: Register 0x00A content

| Bitpos. | Signal  | Width | Meaning                            |

|---------|---------|-------|------------------------------------|

| 15-8    | AddrGrp | 8     | Chip select with own group address |

| 7-0     | Addr    | 8     | Chip select with own address       |

For basic configuration of register 0x00A no action is needed.

Table 26: Register 0x00B content

| Bitpos. | Signal            | Width | Meaning                            |

|---------|-------------------|-------|------------------------------------|

| 15-4    | Reserved          | 12    | Reserved set to zero               |

| 3-0     | BgndTempMeas<3:0> | 4     | Background temperature measurement |

For basic configuration of register 0x00B no action is needed.

Table 27: Register 0x010 content

| Bitpos. | Signal      | Width | Meaning                  |

|---------|-------------|-------|--------------------------|

| 15-8    | Reserved    | 8     | Reserved set to zero     |

| 7-0     | OCVal0<7:0> | 8     | Offset Centering Value 0 |

For basic configuration of register 0x010 no action is needed.

Table 28: Register 0x02F content

| Bitpos. | Signal   | Width | Meaning              |

|---------|----------|-------|----------------------|

| 15-2    | Reserved | 14    | Reserved set to zero |

| 1       | Reserved | 1     | Reserved set to zero |

| 0       | SeqEn    | 1     | Sequencer enable     |

For basic configuration of register 0x02F no action is needed.

Table 29: Register 0x030 content

| Bitpos. | Signal            | Width | Meaning                                                                                                                                    |

|---------|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 15-13   | Seq0AmpGain<2:0>  | 3     | Amplifier Gain 0=32, 1=64, 2=128, 3=256, 4=512, 5=1024, 6 and 7 is not allowed                                                             |

| 12      | Seq0TempSel       | 1     | Temperature Select                                                                                                                         |

| 11-10   | Seq0PixelSel<1:0> | 2     | Pixel Select<br>0: upper left 3D Hall sensor, 1: upper right 3D Hall sensor<br>2: lower right 3D Hall sensor, 3: lower left 3D Hall sensor |

| 9-8     | Seq0SensSel<1:0>  | 2     | Sensor Select<br><1:0>: Sensor: $0 = X$ , $1 = Y$ , $2 = Z$ ,<br>3 = all sensors off                                                       |

| 7-1     | Seq0DecLen<7:1>   | 7     | Decimation Length<br><0> is always 0<br>If DecLen<10:1> is 0 DecLen = 1                                                                    |

| 0       | Seq0DecEn         | 1     | Decimation Enable                                                                                                                          |

For basic configuration of register 0x030 no action is needed.

Table 30: Register 0x031 content

| Bitpos. | Signal            | Width | Meaning                                                                                                |

|---------|-------------------|-------|--------------------------------------------------------------------------------------------------------|

| 15-13   | Seq1AmpGain<2:0>  | 3     | Amplifier Gain 0=32, 1=64, 2=128, 3=256, 4=512, 5=1024, 6 and 7 is not allowed                         |

| 12      | Seq1TempSel       | 1     | Temperature Select                                                                                     |

| 11-10   | Seq1PixelSel<1:0> | 2     | Pixel Select<br>0: upper left pixel, 1: upper right pixel<br>2: lower right pixel, 3: lower left pixel |

| 9-8     | Seq1SensSel<1:0>  | 2     | Sensor Select<br><1:0>: Sensor: $0 = X$ , $1 = Y$ , $2 = Z$ ,<br>3 = all sensors off                   |

| 7-1     | Seq1DecLen<7:1>   | 7     | Decimation Length<br><0> is always 0<br>If DecLen<10:1> is 0 DecLen = 1                                |

| 0       | Seq1DecEn         | 1     | Decimation Enable                                                                                      |

For basic configuration of register 0x031 no action is needed.

Table 31: Register 0x032 content

| Bitpos. | Signal            | Width | Meaning                                                                                                                                    |

|---------|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 15-13   | Seq2AmpGain<2:0>  | 3     | Amplifier Gain 0=32, 1=64, 2=128, 3=256, 4=512, 5=1024, 6 and 7 is not allowed                                                             |

| 12      | Seq2TempSel       | 1     | Temperature Select                                                                                                                         |

| 11-10   | Seq2PixelSel<1:0> | 2     | Pixel Select<br>0: upper left 3D Hall sensor, 1: upper right 3D Hall sensor<br>2: lower right 3D Hall sensor, 3: lower left 3D Hall sensor |

| 9-8     | Seq2SensSel<1:0>  | 2     | Sensor Select<br><1:0>: Sensor: $0 = X$ , $1 = Y$ , $2 = Z$ ,<br>3 = all sensors off                                                       |

| 7-1     | Seq2DecLen<7:1>   | 7     | Decimation Length<br><0> is always 0<br>If DecLen<10:1> is 0 DecLen = 1                                                                    |

| 0       | Seq2DecEn         | 1     | Decimation Enable                                                                                                                          |

For basic configuration of register 0x032 no action is needed.

Table 32: Register 0x033 content

| Bitpos. | Signal            | Width | Meaning                                                                                                                                    |

|---------|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 15-13   | Seq3AmpGain<2:0>  | 3     | Amplifier Gain 0=32, 1=64, 2=128, 3=256, 4=512, 5=1024, 6 and 7 is not allowed                                                             |

| 12      | Seq3TempSel       | 1     | Temperature Select                                                                                                                         |

| 11-10   | Seq3PixelSel<1:0> | 2     | Pixel Select<br>0: upper left 3D Hall sensor, 1: upper right 3D Hall sensor<br>2: lower right 3D Hall sensor, 3: lower left 3D Hall sensor |

| 9-8     | Seq3SensSel<1:0>  | 2     | Sensor Select<br><1:0>: Sensor: 0 = X, 1 = Y, 2 = Z,<br>3 = all sensors off                                                                |

| 7-1     | Seq3DecLen<7:1>   | 7     | Decimation Length<br><0> is always 0<br>If DecLen<10:1> is 0 DecLen = 1                                                                    |

| 0       | Seq3DecEn         | 1     | Decimation Enable                                                                                                                          |

For basic configuration of register 0x033 no action is needed.

Table 33: Register 0x40 content

| Bitpos. | Signal         | Width | Meaning                        |

|---------|----------------|-------|--------------------------------|

| 15      | Reserved       | 1     | Reserved, set to zero          |

| 14-9    | BGTrim<5:0>    | 6     | Bandgap Trim                   |

| 8-4     | lBiasTrim<4:0> | 5     | Trim bits for IBias generation |

| 3-0     | SRegTrim<3:0>  | 4     | Trim bits for sensor regulator |

For basic configuration of register 0x040 with typical electrical trim values write via SPI transfer:

**8040h – 4058h** BGTrim=32; IBiasTrim=5; SRegTrim=8

Attention: Electrical trim values are device dependent and have to be read from OTP at startup.

Table 34: Register 0x050 content

| Bitpos. | Signal        | Width | Meaning              |

|---------|---------------|-------|----------------------|

| 15-8    | Reserved      | 8     | Reserved set to zero |

| 7-0     | FuseAddr<7:0> | 8     | Fuse Address         |

For basic configuration of register 0x050 no action is needed.

Table 35: Register 0x051 content

| Bitpos. | Signal        | Width | Meaning              |

|---------|---------------|-------|----------------------|

| 15-8    | Reserved      | 8     | Reserved set to zero |

| 7-0     | FuseData<7:0> | 8     | Fuse Data            |

For basic configuration of register 0x051 no action is needed.

Table 36: Register 0x100 content

| Bitpos. | Signal                                       | Width | Meaning                                                     |

|---------|----------------------------------------------|-------|-------------------------------------------------------------|

| 15      | DecVal<15><br>RngWarn<br>SeqNr<1><br>Parity  | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 14      | DecVal<14><br>SeqNr<1><br>SeqNr<0><br>Parity | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 13      | DecVal<13><br>SeqNr<0><br>Parity             | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 12      | DecVal<12><br>Parity                         | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 11-0    | DecVal<11:0>                                 | 12    | Decimation Value                                            |

Table 37: Register 0x102 content

| Bitpos. | Signal     | Width | Meaning                                                                                       |

|---------|------------|-------|-----------------------------------------------------------------------------------------------|

| 15      | Ready      | 1     | Ready                                                                                         |

| 14      | HistWarn   | 1     | Histogram Warning                                                                             |

| 13      | RngWarn    | 1     | Range Warning                                                                                 |

| 12-11   | Reserved   | 2     | Reserved set to zero                                                                          |

| 10-9    | SeqNr<1:0> | 2     | Sequencer number                                                                              |

| 8-4     | FC<4:0>    | 5     | Field Component<br><4>: Temperature<br><3:2>: Pixel<br><1:0>: Sensor: $0=X$ , $1=Y$ , $2=Z$ , |

| 3-1     | Reserved   | 3     | Reserved set to zero                                                                          |

| 0       | DecVal<16> | 1     | Decimation Value MSB; only relevant if measurement result width is 17 Bit                     |

Register Map

Table 38: Register 0x103 content

| Bitpos. | Signal                         | Width | Meaning                                                 |

|---------|--------------------------------|-------|---------------------------------------------------------|

| 15-0    | {Reserved<7:0>,<br>OCVal<7:0>} | 16    | Offset Centering Value if one of the Auto4P Bits is set |

|         | or                             |       | otherwise                                               |

|         | HistVal<15:0>                  |       | Histogram in single phase measurements                  |

Table 39: Register 0x104 content

| Bitpos. | Signal        | Width | Meaning                                                     |

|---------|---------------|-------|-------------------------------------------------------------|

| 15-0    | TempVal<15:0> | 16    | Temperature Value of the background temperature measurement |

Table 40: Register 0x130 content

| Bitpos. | Signal                                                      | Width | Meaning                                                     |

|---------|-------------------------------------------------------------|-------|-------------------------------------------------------------|

| 15      | Seq0DecVal<15><br>Seq0RngWarn<br>Seq0SeqNr<1><br>Seq0Parity | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 14      | Seq0DecVal<14> Seq0SeqNr<1> Seq0SeqNr<0> Seq0Parity         | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 13      | Seq0DecVal<13><br>Seq0SeqNr<0><br>Seq0Parity                | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 12      | Seq0DecVal<12><br>Seq0Parity                                | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 11-0    | Seq0DecVal<11:0>                                            | 12    | Decimation Value                                            |

Register Map

Table 41: Register 0x131 content

| Bitpos. | Signal                                                      | Width | Meaning                                                     |

|---------|-------------------------------------------------------------|-------|-------------------------------------------------------------|

| 15      | Seq1DecVal<15><br>Seq1RngWarn<br>Seq1SeqNr<1><br>Seq1Parity | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 14      | Seq1DecVal<14> Seq1SeqNr<1> Seq1SeqNr<0> Seq1Parity         | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 13      | Seq1DecVal<13><br>Seq1SeqNr<0><br>Seq1Parity                | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 12      | Seq1DecVal<12><br>Seq1Parity                                | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 11-0    | Seq1DecVal<11:0>                                            | 12    | Decimation Value                                            |

Table 42: Register 0x132 content

| Bitpos. | Signal                                                      | Width | Meaning                                                     |

|---------|-------------------------------------------------------------|-------|-------------------------------------------------------------|

| 15      | Seq2DecVal<15><br>Seq2RngWarn<br>Seq2SeqNr<1><br>Seq2Parity | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 14      | Seq2DecVal<14> Seq2SeqNr<1> Seq2SeqNr<0> Seq2Parity         | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 13      | Seq2DecVal<13><br>Seq2SeqNr<0><br>Seq2Parity                | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 12      | Seq2DecVal<12><br>Seq2Parity                                | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 11-0    | Seq2DecVal<11:0>                                            | 12    | Decimation Value                                            |

| Register Map |

|--------------|

|              |

Table 43: Register 0x0133 content

| Bitpos. | Signal                                                       | Width | Meaning                                                     |

|---------|--------------------------------------------------------------|-------|-------------------------------------------------------------|

| 15      | Seq3DecVal<15><br>Seq3RngWarn<br>Seq3SeqNr<1><br>Seq3Parity  | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 14      | Seq3DecVal<14><br>Seq3SeqNr<1><br>Seq3SeqNr<0><br>Seq3Parity | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 13      | Seq3DecVal<13><br>Seq3SeqNr<0><br>Seq3Parity                 | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 12      | Seq3DecVal<12><br>Seq3Parity                                 | 1     | Depending on<br>Rng2Reg100<br>SeqNr2Reg100<br>Parity2Reg100 |

| 11-0    | Seq3DecVal<11:0>                                             | 12    | Decimation Value                                            |

### 6

### **Application Notes**

In this chapter a step-by-step instruction is given to use the sensor in a proper way.

With the basic configuration (chapter. 6.1) first measurements can be done for bring-up.

Using the described signal postprocessing (chapter. 6.5) and the determination of magnetic trim values (Chap. 6.6) measurements over temperature with a high accuracy can be realized.

#### 6.1

### First raw measurements with the basic configuration

A decimation length of 512 leads to a resolution of 15 bit.

The wait length can be equal for all sensors. The typical wait length for this decimation length is 80.

The sensor supply regulator has to be set to UD = 2.6 V.

The gain is different for XY and Z sensors. XY sensors use gain 128, Z sensors use gain 64.

#### 6.1.1

#### **Basic configuration**

The basic configuration has to be written once after a sensor reset.

The default trim values for the bandgap reference, bias current and sensor supply regulator are:

ICT\_VREF\_TRIM: 6'b100000

ICT\_IBIAS\_TRIM: 4'b0101

ICT\_SREG\_TRIM: 4'b1000

The device specific values are available in the OTP (please refer to chapter 7.5) and have to be used in application. For a basic configuration please send the following commands:

- 8040h 4058h

- BGTrim 32; IBiasTrim 5; SRegTrim 8

- 8002h E250h

- AmpComp: 7; DecLen: 2\*256+(DecLen<7:1>\*2); DecWait: 80

- 8003h A000h

- SRegDVal:5 = 2.6 V; SRegNVal:0 = 0.2 V

- 8004h 0AA9h

- Auto4P:0101b; OCMode:10b; OCAuto; OCToggle; OCGain: 001b

- 8005h 0002h

- RM 1

- 8006h 077Fh

- all PO except EC\_PO; SMUXPowEn; SMUXSigEn

#### 6.1.2

#### Measurement of Pixel 0, Sensor X, Gain 128, DecLen 512

- Gain 128 = 2-> 010b

- PixelSel = 00b

- SensSel = X = 00b

- DecLen = 512 = 200h -> DecLen<7:1>=0 -> 0000000b

- DecEn = 1b start measurement

Send the following command to start the measurement:

• 8001h - 4001h Pixel 0, Sensor X, Gain 128, DecLen 512

Read out measurement by sending the following commands as described in chapter 4.1.

0102h - 0100h - 0000h

#### 6.1.3

#### Measurement of Pixel 1, Sensor Z, Gain 64, DecLen 512

- Gain 64 = 1-> 001b

- PixelSel = 1b

- SensSel = Z = 10b

- DecLen = 512 = 200h -> DecLen<7:1>=0 -> 0000000b

- DecEn = 1b start measurement

Send the following command to start the measurement:

• 8001h - 2601h Pixel 1, Sensor Z, Gain 64, DecLen 512

Read out measurement by sending the following commands as described in chapter 4.1.

• 0102h - 0100h - 0000h

#### 6.1.4

## Measurement of the Temperature, with preheating of the next Sensor Pixel 0, Sensor X, Gain 128, DecLen 512

For a constant power consumption and a stable sensor temperature the next hall sensor can be activated during the temperature measurement. The gain setting for the next hall sensor has to be used.

- Gain 128 = 2-> 010b

- TempSel = 1b

- PixelSel = 0b

- SensSel = X = 00b

- DecLen = 512 = 200h -> bit 3 to 0 are allways 0 -> 100000b

- DecEn = 1b start measurement

Send the following command to start the measurement:

• 8001h - 5041h Pixel 0, Sensor X, Gain 128, DecLen 512

Read out measurement by sending the following commands as described in chapter 4.1.

0102h – 0100h – 0000h

#### 6.2

### High speed measurement configuration using sequencer

Single hall sensor elements can be measured with up to 80 kHz at 10 Bit resolution. In sequencer mode the measurements are taken continuously. The SPI communication has no influence to the measurement frequency.

For details about sequencer configuration please refer to chapter 7.4.

Another option for communication in high speed configurations is continuous measurement, please refer to chapter 7.3.1.

#### **Basic configuration:**

- 8040h 4058h

- BGTrim 32; IBiasTrim 5; SRegTrim 8

- 8002h F00Ah

- AmpComp 7; Fast2P; DecWait 10

- 8003h A000h

- SRegDVal:5 = 2.6 V; SRegNVal:0 = 0.2 V

- 8004h 0AA9h

- Auto4P:0101b; OCMode:10b; OCAuto; OCToggle; OCGain: 001b

- 8005h 003Ah

- Rng2Reg100; SeqNr2Reg100; Parity2Reg100, RM 1

- 8006h 077Fh

- all PO except EC\_PO; SMUXPowEn; SMUXSigEn

Sequencer configuration: Z-Sensor Pixel 0, Gain 256, DecLen 34

- 8030h 6223h

- Gain 256; Pixel 0; Sensor Z; DecLen 34, DecEn

#### Sequencer start:

- 802Fh 0001h

- SeqEn

**Measurement value readout:** Read data and status at every READY toggle. Alternatively read from register 0x100.

- 0130h 0000h

- Seq0RngWarn, Seq0SeqNr, Seq0Parity, Seq0DecVal

#### Resolution:

• DecLen: 34, Number of phases: 2,  $\pm 7.5$  Digit/decimation cycle 34 \* 2 \* (+7.5 - (-7.5)) \* 2) =  $1020 \rightarrow$  **10 Bit**

#### Measurement time / sample rate:

DecWait: 10; DecLen: 34, Number of phases: 2

(6+10+34) \* 2 = 100 cycles @ 8 MHz system clock

→ measurement time 12.5 µs, sample rate 80 kHz

# 6.3 Magnetic resolution

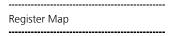

The basic configuration is working in four-phase spinning current scheme with a decimation length of 512. As the  $\sum \Delta$ -ADC has a resolution of 4 bit and is symmetrical around 0. The maximum ADC value magnitude is 7.5.

The measurement values are in the range of ±15360 which is a resolution of 14.9 bit.

The following picture shows the signal path and its typical parameters.

Figure 11: Signal Path

| Application Notes |  |

|-------------------|--|

With a differential input of the ADC of ±1.106 V, a 4-bit resolution, a decimation length of 512 a gain of 128 and a 4 phase spinning current scheme the resolution of the ADC can be calculated to:

$$(2*1.06 \text{ V}) / 128 / (512 * 15 * 4) = 539.1 \text{ nV}$$

With a sensitivity of 54 mV/T for the X and Y sensors the magnetic resolution can be calculated to:

$$539.1 \text{ nV} / 54 \text{ mV/T} = 9.98 \mu\text{T}.$$

With a gain of 64 and a sensitivity of 94 mV/T the magnetic resolution of the Z sensors is:

$$(2*1.06 \text{ V}) / 64 / (512*15*4) = 1078.3 \text{ nV}$$

$$1078.3 \text{ nV} / 94 \text{ mV/T} = 11.47 \mu\text{T}$$

### 6.4

#### Measurement time

In the basic configuration the hall sensors are operated in a four-phase spinning current scheme while the temperature sensor always is operated in a two phase chopper principle.

The pure measurement time can be calculated by:

- (DecLen + DecWait + 6) \* 4 \* (nr. of hall sensors) + (DecLen+ DecWait + 6) \* 2

- (512 + 80 + 6) \* 4 \* 3 + (512 + 80 + 6) \* 2 = 8372

- MHz = 125 ns

- 8372 \* 125ns = 1046.5 μs

If the SPI runs at 16MHz the time for communication can be calculated by:

- 16 bit address + 16 bit data = 32 bit

- 16MHz = 62.5 ns

- Per sensor (magnet or temperature) 1 x start + 2 x read

- 32 \* 4 \* 3 \* 62.5 ns = 24 μs

The complete measurement time for all tree hall sensors and the temperature sensor is about 1070.5  $\mu$ s including all the communication in non-interleaved mode.

#### 6.5

### Signal postprocessing

In many applications, the raw senor values can be used without any postprocessing. In this case the parameters described in Table 4 can be used. If the performance described in Table 3 is needed the raw measured digital values have to be converted into magnetic flux density values by using the following signal postprocessing. The necessary parameters can be generated on chip by using the integrated excitation wires as described in chapter 6.6. If higher accuracies are needed the sensitivities and offsets have to be measured by using 3D Helmholtz coils.

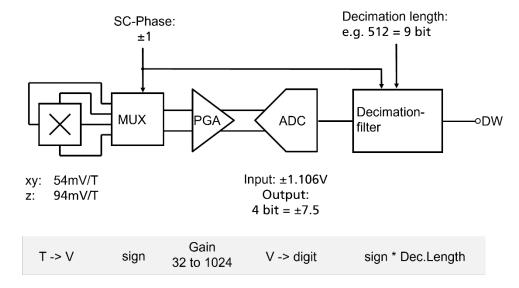

## 6.5.1 Temperature postprocessing

As in constant voltage supplied mode the sensitivity of the Hall sensors is temperature dependent the temperature has to be measured. The necessary temperature postprocessing is shown in Figure 12.

Figure 12: Temperature postprocessing

Using the basic configuration, the temperature value TVal has only to be compensated with the device specific temperature offset TOffset which has to be measured at 25°C.

$$TOffset = TVal(at 25^{\circ}C)$$

This postprocessed temperature value TValPP can then be used for the magnetic postprocessing.

$$TValPP = TVal - TOffset$$

If a different configuration is used the measured temperature value TVal hast to be scaled by the factor TDecLenFactor which can be calculated by:

$$TDecLenFactor = \frac{512}{DecLen}$$

If the temperature in °C is needed TValPP can be converted in °C by the factor Digit2Celsius.

$$Digit2Celsius = 0.072484471 \frac{^{\circ}C}{Digit}$$

The temperature in °C can be calculated by:

$$TValin^{\circ}C = TValPP * Digit2Celsius + 25^{\circ}C$$

## 6.5.2 Magnetic postprocessing

The necessary magnetic postprocessing is shown in Figure 13.

Figure 13: Magnetic postprocessing

Using the basic configuration, the digital hall signal HVal can be converted from Digit to Tesla over temperature using the direction specific typical functions  $S_{XY}(TValPP)$  or  $S_Z(TValPP)$ .

$$S_{Typ,XY}(TValPP) = 2.4864 \times 10^{-14} \times TValPP^3 + 5.4240 \times 10^{-10} \times TValPP^2 + 4.1604 \times 10^{-6} \times TValPP + 0.010687$$

$$S_{Typ,Z}(TValPP) = 2.6029 \times 10^{-14} \times TValPP^3 + 5.6780 \times 10^{-10} \times TValPP^2 - 4.3553 \times 10^{-6} \times TValPP + 0.011187$$

If different configurations than the basic configurations are used the measured Hall values HVal have to be scaled to the basic configuration parameters (decimation length of 512; gain 128 for XY, gain 64 for Z; sensor supply) by the factor HConfigFactor which can be calculated by:

$$HConfigFactor = \frac{1}{\left(\frac{UsedGain}{BasicGain}\right) \times \left(\frac{UsedDecLen}{BasicDecLen}\right) \times \left(\frac{UsedSupply}{BasicSupply}\right)}$$

For high accuracies as described in Table 3, the device specific production deviations concerning nominal sensitivity, amplifier gains and sensor supply regulator voltages has to be compensated using the factor HGainComp which needs to be calculated for each sensor. Chapter 6.6 describes how this value can be measured.

The magnetic values in Tesla have to be compensated with the device and sensor specific magnetic offsets over temperature O(TValPP). The minimum offset compensation should be done at 25°C as described in chapter 6.6. For higher accuracies the offset temperature coefficient has to be used as described in chapter 6.6.

As the orthogonality errors Z/X and Z/Y can be in the range of several degrees. Depending on accuracy needed in application these orthogonality errors have to be compensated by the coefficient  $Orth_{XY}(HValPP(Z))$ . Chapter 6.6 describes how these factors can be measured on chip.

|             |       | <br> |

|-------------|-------|------|

| Application | Notes |      |

Using the basic configuration, the postprocessed magnetic field values can be calculated by:

$$HValPP_Z = HVal_Z \times HGainComp \times S_Z(TValPP) - O_Z(TValPP)$$

$$HValPP_{XY} = HVal_{XY} \times HGainComp \times S_{XY}(TValPP) - O_{XY}(TValPP) - Orth_{XY}(HValPP_Z(TValPP))$$

#### 6.6

### Determination of magnetic trim values using the integrated excitation coils

The integrated excitation coils can be used to measure the sensors sensitivities, offsets and offset temperature coefficients due to self-heating. If possible choose the maximum excitation current and supply voltage to get low noise measurements and high self-heating effects. Perform this test at room temperature (25°C).

At first the magnetic trimming measurement sequence has to be implemented.