# SN54170, SN54LS170, SN74170, SN74LS170 4-BY-4 REGISTER FILES WITH OPEN-COLLECTOR OUTPUTS

SDLS065 - MARCH 1974 - REVISED MARCH 1988

- Separate Read/Write Addressing Permits Simultaneous Reading and Writing

- Fast Access Times . . . Typically 20 ns

- Organized as 4 Words of 4 Bits

- Expandable to 1024 Words of n-Bits

- For Use as:

Scratch-Pad Memory

Buffer Storage between Processors

Bit Storage in Fast Multiplication Designs

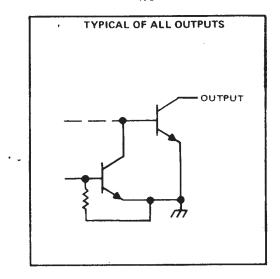

- Open-Collector Outputs with Low Maximum Off-State Current: '170 . . . 30 μΑ 'LS170 . . . 20 μΑ

- SN54LS670 and SN74LS670 Are Similar But Have 3-State Outputs

### description

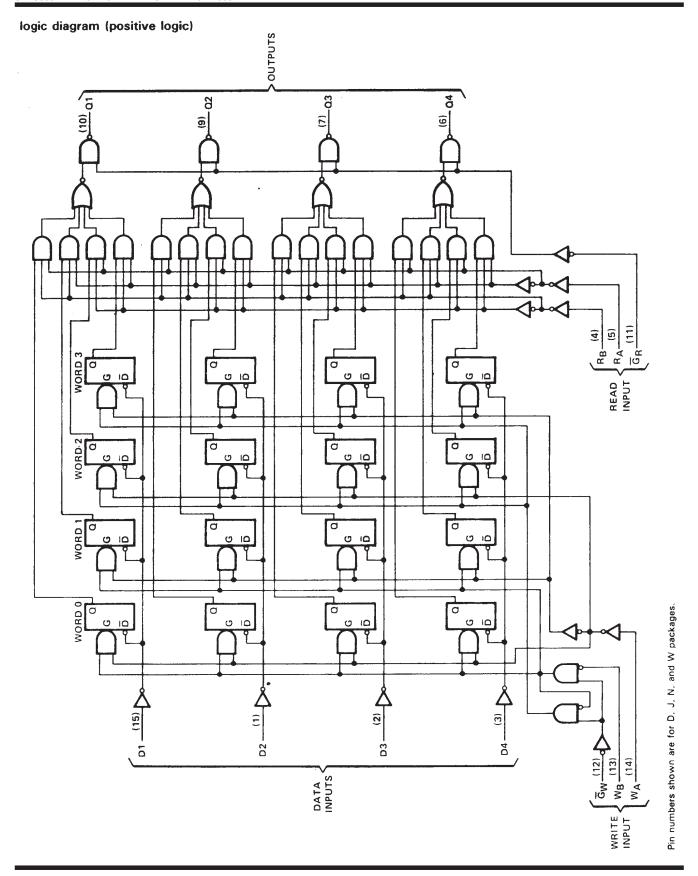

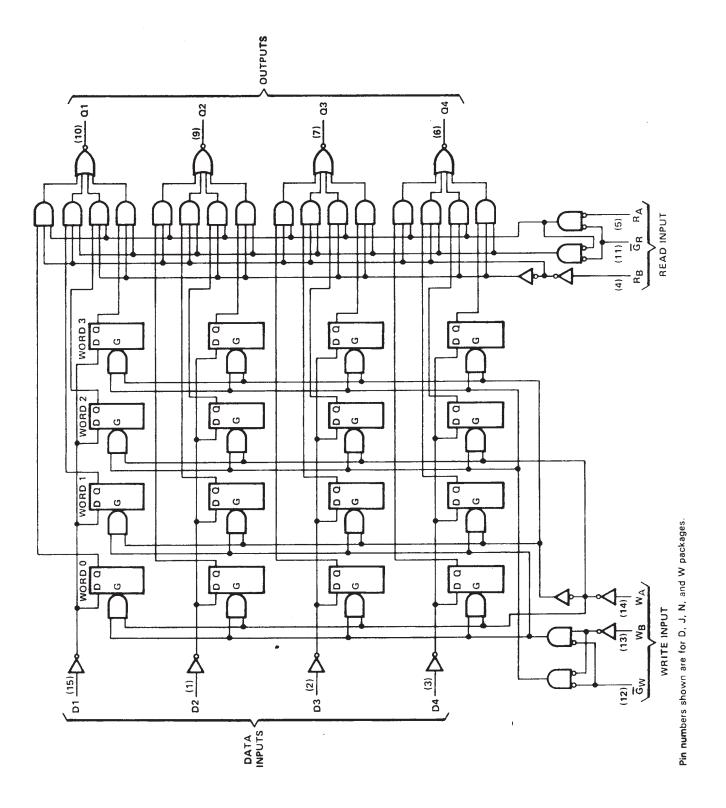

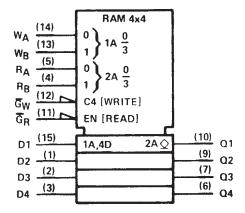

The '170 and 'LS170 MSI 16-bit TTL register files incorporate the equivalent of 98 gates. The register file is organized as 4 words of 4 bits each and separate on-chip decoding is provided for addressing the four word locations to either write-in or retrieve data. This permits simultaneous writing into one location and reading from another word location.

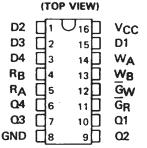

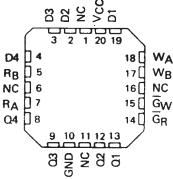

SN54170, SN54LS170 . . . J OR W PACKAGE SN74170 . . . N PACKAGE SN74LS170 . . . D OR N PACKAGE

SN54LS170 . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

Four data inputs are available which are used to supply the 4-bit word to be stored. Location of the word is determined by the write-address inputs A and B in conjunction with a write-enable signal. Data applied at the inputs should be in its true form. That is, if a high-level signal is desired from the output, a high level is applied at the data input for that particular bit location. The latch inputs are arranged so that new data will be accepted only if both internal address gate inputs are high. When this condition exists, data at the D input is transferred to the latch output. When the write-enable input,  $\overline{G}_W$ , is high, the data inputs are inhibited and their levels can cause no change in the information stored in the internal latches. When the read-enable input,  $\overline{G}_R$ , is high, the data outputs are inhibited and remain high.

The individual address lines permit direct acquisition of data stored in any four of the latches. Four individual decoding gates are used to complete the address for reading a word. When the read address is made in conjunction with the read-enable signal, the word appears at the four outputs.

This arrangement—data-entry addressing separate from data-read addressing and individual sense line—eliminates recovery times, permits simultaneous reading and writing, and is limited in speed only by the write time (30 nanoseconds typical) and the read time (25 nanoseconds typical). The register file has a nondestructive readout in that data is not lost when addressed.

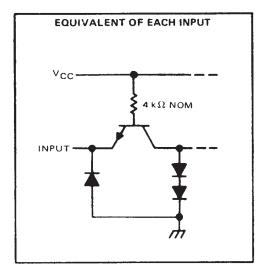

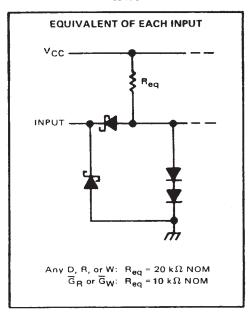

All '170 inputs and all inputs except the read enable and write enable of the 'LS170 are buffered to lower the drive requirements to one Series 54/74 or Series 54LS/74LS standard load, respectively. Input-clamping diodes minimize switching transients to simplify system design. High-speed, double-ended AND-OR-INVERT gates are employed for the read-address function and drive high-sink-current, open-collector outputs. Up to 256 of these outputs may be wire-AND connected for increasing the capacity up to 1024 words. Any number of these registers may be paralleled to provide n-bit word length.

The SN54170 and SN54LS170 are characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C; the SN74170 and SN74LS170 are characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

### logic diagram (positive logic)

# SN54170, SN54LS170, SN74170, SN74LS170 4-BY-4 REGISTER FILES WITH OPEN-COLLECTOR OUTPUTS

SDLS065 - MARCH 1974 - REVISED MARCH 1988

#### WRITE FUNCTION TABLE (SEE NOTES A, B, AND C)

#### WRITE INPUTS WORD Ğw 1 2 3 WB WA Q = D $\sigma_0$ $Q_0$ $Q_0$ Q = DН L $Q_0$ $a_0$ $Q_0$ $\alpha_0$ $Q_0$ L L Q = D $a_0$ H Н L $Q_0$ $a_0$ $Q_0$ Q = D $\sigma_{0}$ н Х Х $a_0$ $Q_0$

#### READ FUNCTION TABLE (SEE NOTES A AND D)

| RE | AD INPU | ITS | OUTPUTS |      |      |      |  |  |  |

|----|---------|-----|---------|------|------|------|--|--|--|

| RB | RA      | GR  | Q1      | 02   | Q3   | Q4   |  |  |  |

| L  | L       | L   | W0B1    | W0B2 | W0B3 | W0B4 |  |  |  |

| L  | Н       | L   | W1B1    | W1B2 | W1B3 | W1B4 |  |  |  |

| Н  | L       | L   | W2B1    | W2B2 | W2B3 | W2B4 |  |  |  |

| н  | Н       | L   | W3B1    | W3B2 | W3B3 | W3B4 |  |  |  |

| ×  | X       | Н   | н       | Н    | Н    | н    |  |  |  |

NOTES: A. H = high level, L = low level, X = irrelevant.

- B. (Q = D) = The four selected internal flip-flop outputs will assume the states applied to the four external data inputs.

- C.  $Q_0$  = the level of Q before the indicated input conditions were established.

- D. W0B1 = The first bit of word 0, etc.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                                      | 1 |

|-----------------------------------------------------------------------|---|

| Input voltage: '170                                                   | , |

| 'LS170                                                                |   |

| Off-state output voltage: '170                                        | , |

| 'LS170                                                                |   |

| Operating free-air temperature range: SN54170, SN54LS170 (see Note 2) | ) |

| SN74170, SN74LS170 0°C to 70°C                                        | ) |

| Storage temperature range                                             | ) |

NOTES: 1. Voltage values are with respect to network ground terminal.

2. An SN54170 in the W package operating at free-air temperatures above  $105^{\circ}\text{C}$  requires a heat sink that provides a thermal resistance from case to free-air,  $R_{\theta \text{CA}}$ , of not more than  $38^{\circ}\text{C/W}$

# logic symbols†

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

Pin numbers shown are for D, J, N, and W packages,

### recommended operating conditions

|                                                          |                                                                |     | SN5417 | 0   | SN74170 |     |      |      |

|----------------------------------------------------------|----------------------------------------------------------------|-----|--------|-----|---------|-----|------|------|

|                                                          | -                                                              | MIN | NOM    | MAX | MIN     | NOM | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>                          |                                                                | 4.5 | 5      | 5.5 | 4.75    | 5   | 5.25 | ٧    |

| High-level output voltage, VOH                           |                                                                |     |        | 5.5 |         |     | 5.5  | ٧    |

| Low-level output current, IOL                            |                                                                |     |        | 16  |         |     | 16   | mA   |

| Width of write-enable or read-enable pulse, tw           |                                                                | 25  |        | -   | 25      |     |      | ns   |

| Setup times, high- or low-level data                     | Data input with respect to write enable, t <sub>su(D)</sub>    | 10  |        |     | 10      |     |      | ns   |

| (see Figure 2)                                           | Write select with respect to write enable, t <sub>su</sub> (W) | 15  |        |     | 15      |     |      | ns   |

| Hold times, high- or low-level data                      | Data input with respect to write enable, th(D)                 | 15  |        |     | 15      |     |      | ns   |

| (see Note 3 and Figure 2)                                | Write select with respect to write enable, th(W)               | 5   |        |     | 5       |     |      | ns   |

| Latch time for new data, t <sub>latch</sub> (see Note 4) |                                                                | 25  |        | -   | 25      |     |      | ns   |

| Operating free-air temperature range, TA (see Note 2     | 2)                                                             | -55 | -      | 125 | 0       |     | 70   | °C   |

- NOTES: 2. An SN54170 in the W package operating at free-air temperatures above 105°C requires a heat sink that provides a thermal resistance from case to free-air, R<sub>6CA</sub>, of not more than 38°C/W.

- 3. Write select setup time will protect the data written into the previous address. If protection of data in the previous address is not required, t<sub>su(W)</sub> can be ignored as any address selection sustained for the final 30 ns of the write-enable pulse and during t<sub>h(W)</sub> will result in data being written into that location. Depending on the duration of the input conditions, one or a number of previous addresses may have been written into.

- 4. Latch time is the time allowed for the internal output of the latch to assume the state of new data. See Figure 2. This is important only when attempting to read from a location immediately after that location has received new data.

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                              | TEST CONDITIONS†                                                                                  | MIN | TYP‡ | MAX  | UNIT |  |

|------------------|----------------------------------------|---------------------------------------------------------------------------------------------------|-----|------|------|------|--|

| VIH              | High-level input voltage               |                                                                                                   | 2   |      |      | V    |  |

| VIL              | Low-level input voltage                |                                                                                                   |     |      | 8.0  | V    |  |

| VIK              | Input clamp voltage ,                  | $V_{CC} = MIN$ , $I_I = -12 \text{ mA}$                                                           |     |      | -1.5 | V    |  |

| ¹он              | High-level output current              | V <sub>CC</sub> = MIN, V <sub>OH</sub> = 5.5 V,<br>V <sub>IH</sub> = 2 V, V <sub>IL</sub> = 0.8 V |     |      | 30   | μΑ   |  |

| VOL              | Low-level output voltage               | V <sub>CC</sub> = MIN, V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = 0.8 V, I <sub>OL</sub> = 16 mA |     | 0.2  | 0.4  | ٧    |  |

| f <sub>1</sub>   | Input current at maximum input voltage | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V                                                     |     | _    | 1    | mA   |  |

| ЧН               | High-level input current               | V <sub>CC</sub> = MAX, V <sub>1</sub> = 2.4 V                                                     |     |      | 40   | μА   |  |

| I <sub>I</sub> L | Low-level input current                | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4 V                                                     |     |      | -1.6 | mA   |  |

|                  | 6                                      | V <sub>CC</sub> = MAX, SN54170                                                                    |     | 1278 | 140  | mA   |  |

| ICC              | Supply current                         | See Note 5 SN74170                                                                                |     | 127§ | 150  |      |  |

$<sup>^\</sup>dagger$  For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

$<sup>^{\</sup>ddagger}$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_{A} = 25^{\circ}\text{C}$ .

<sup>§</sup>Typical supply current shown is an average for 50% duty cycle.

NOTE 5: Maximum I<sub>CC</sub> is guaranteed for the following worst-case conditions: 4.5 V is applied to all data inputs and both enable inputs, all address inputs are grounded, and all outputs are open.

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

| PARAMETER <sup>†</sup> | FROM TO TEST CONDITIONS (INPUT)     |        | MIN                                       | TYP | MAX  | UNIT     |     |

|------------------------|-------------------------------------|--------|-------------------------------------------|-----|------|----------|-----|

| tPLH                   | Good eachle                         | Any Q  | C. = 15 oF                                |     | 10   | 15       | ns  |

| tPHL                   | Read enable                         | Ally Q | CL = 15 pF,<br>RL = 400 Ω,                |     | 20   | 30       |     |

| <sup>†</sup> PLH       | Read Select                         | Any Q  | See Figures 1 and 2                       |     | 23   | 35       | ns  |

| <sup>†</sup> PHL       | Head Select                         | Any C  |                                           |     | 30   | 40       |     |

| <sup>t</sup> PLH       | Maior and to                        | A O    | C: -15 oF                                 |     | 25   | 40<br>45 | ns  |

| <sup>t</sup> PHL       | Write enable                        | Any Q  | $C_L = 15  pF$ ,<br>$R_L = 400  \Omega$ , |     | 34   |          | 115 |

| tPLH                   | 0                                   | AO     |                                           | 2   | 20   | 30       | ns  |

| tPHL                   | TPHL Data Any Q See Figures 1 and 3 |        | 30                                        | 45  | 1113 |          |     |

$t_{\text{PLH}}$  = propagation delay time, low-to-high-level output

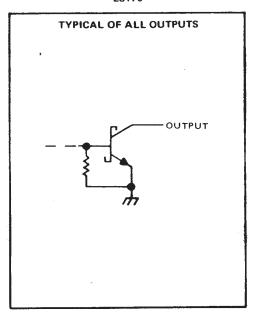

# schematics of inputs and outputs

170

170

tpHL = propagation delay time, high-to-low-level output

### recommended operating conditions

|                                                            |                                                               | SI  | N54LS1 | 70  | SN74LS170 |     |      | TINU |

|------------------------------------------------------------|---------------------------------------------------------------|-----|--------|-----|-----------|-----|------|------|

|                                                            |                                                               | MIN | NOM    | MAX | MIN       | NOM | MAX  | UNII |

| Supply voltage, V <sub>CC</sub>                            |                                                               | 4.5 | 5      | 5.5 | 4.75      | 5   | 5.25 | ٧    |

| High-level output voltage, VOH                             | •                                                             |     |        | 5.5 |           |     | 5.5  | V    |

| Low-level output current, IOL                              |                                                               |     |        | 4   |           |     | 8    | mA   |

| Width of write-enable or read-enable pulse, t <sub>W</sub> |                                                               | 25  |        |     | 25        |     |      | ns   |

| Setup times, high- or low-level data (see Figure 2)        | Data input with respect to write enable, t <sub>su(D)</sub>   | 10  |        |     | 10        |     |      | ns   |

|                                                            | Write select with respect to write enable, t <sub>su(W)</sub> | 15  |        |     | 15        |     |      | ns   |

| Hold times, high- or low-level data                        | Data input with respect to write enable, th(D)                | 15  |        |     | 15        |     | -    | ns   |

| (see Note 3 and Figure 2)                                  | Write select with respect to write enable, th(W)              | 5   |        |     | 5         |     |      | ns   |

| Latch time for new data, t <sub>latch</sub> (see Note 4)   |                                                               | 25  |        |     | 25        |     |      | ns   |

| Operating free-air temperature range, TA                   |                                                               | -55 |        | 125 | 0         |     | 70   | °c   |

NOTES: 3. Write-select setup time will protect the data written into the previous address. If protection of data in the previous address is not required, t<sub>su(W)</sub> can be ignored as any address selection sustained for the final 30 ns of the write-enable pulse and during t<sub>h(W)</sub> will result in data being written into that location. Depending on the duration of the input conditions, one or a number of previous addresses may have been written into.

4. Latch time is the time allowed for the internal output of the latch to assume the state of new data. See Figure 2. This is important only when attempting to read from a location immediately after that location has received new data.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|     |                           |                                  | Trop coupirioust                                                |                                                     | SN54LS170 |      |      | SN74LS170 |      |      |       |    |

|-----|---------------------------|----------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|-----------|------|------|-----------|------|------|-------|----|

|     | PARAMETER                 |                                  | IEST CON                                                        | EST CONDITIONS†                                     |           | TYP‡ | MAX  | MIN       | TYP‡ | MAX  | UNIT  |    |

| VIH | High-level input voltage  |                                  |                                                                 |                                                     | 2         |      |      | 2         |      |      | V     |    |

| VIL | Low-level input voltage   |                                  |                                                                 |                                                     |           |      | 0.7  |           |      | 8.0  | V     |    |

| VIK | Input clamp voltage       |                                  | V <sub>CC</sub> = MIN,                                          | I <sub>1</sub> = -18 mA                             |           |      | -1.5 |           |      | -1.5 | V     |    |

| ЮН  | High-level output current |                                  | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max | V <sub>OH</sub> = 5.5 V,<br>, V <sub>IH</sub> = 2 V |           |      | 100  |           |      | 100  | μА    |    |

|     |                           | V <sub>CC</sub> = MIN,           | I <sub>OL</sub> = 4 mA                                          |                                                     | 0.25      | 0.4  |      | 0.25      | 0.4  |      |       |    |

| VOL |                           |                                  | V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = V <sub>IL</sub> max | I <sub>OL</sub> = 8 mA                              |           |      |      |           | 0.35 | 0.5  | ľ     |    |

|     | Input current at          | Any D, R, or W                   |                                                                 | V MAY                                               |           |      |      | 0.1       |      |      | 0.1   | mA |

| 11  | maximum input voltage     | GR or GW                         | V <sub>CC</sub> = MAX,                                          | V <sub>1</sub> = 7 V                                |           |      | 0.2  |           |      | 0.2  | ] "'' |    |

|     |                           | Any D, R, or W                   |                                                                 | 27.4                                                |           |      | 20   |           |      | 20   |       |    |

| ЧH  | High-level input current  | G <sub>R</sub> or G <sub>W</sub> | $V_{CC} = MAX$ , $V_1 = 2.7 V$                                  |                                                     |           |      | 40   | 1         |      | 40   | μΑ    |    |

|     |                           | Any D, R, or W                   |                                                                 |                                                     |           | -    | -0.4 |           |      | -0.4 |       |    |

| ΙΙL | Low-level input current   | GR or GW                         | V <sub>CC</sub> = MAX,                                          | $V_1 = 0.4 V$                                       |           |      | -0.8 |           |      | -0.8 | mA    |    |

| Icc | Supply current            |                                  | V <sub>CC</sub> = MAX,                                          | See Note 5                                          |           | 25   | 40   |           | 25   | 40   | mA    |    |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

$\pm$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

NOTE 5: I<sub>CC</sub> is measured under the following worst-case conditions: 4.5 V is applied to all data inputs and both enable inputs, all address inputs are ground, and all outputs are open.

# SN54LS170, SN74LS170 4-BY-4 REGISTER FILES WITH OPEN-COLLECTOR OUTPUTS

SDLS065 - MARCH 1974 - REVISED MARCH 1988

### recommended operating conditions

|                                                            |                                                               | SI  | N54LS1 | 70  | SN74LS170 |     |      | UNIT |

|------------------------------------------------------------|---------------------------------------------------------------|-----|--------|-----|-----------|-----|------|------|

|                                                            | •                                                             | MIN | NOM    | MAX | MIN       | NOM | MAX  | ONLI |

| Supply voltage, V <sub>CC</sub>                            |                                                               | 4.5 | 5      | 5.5 | 4.75      | 5   | 5.25 | ٧    |

| High-level output voltage, VOH                             |                                                               |     |        | 5.5 |           |     | 5.5  | V    |

| Low-level output current, IOL                              |                                                               |     |        | 4   |           |     | 8    | mA   |

| Width of write-enable or read-enable pulse, t <sub>W</sub> |                                                               | 25  |        |     | 25        |     |      | ns   |

| Setup times, high- or low-level data (see Figure 2)        | Data input with respect to write enable, t <sub>su(D)</sub>   | 10  |        |     | 10        |     |      | ns   |

|                                                            | Write select with respect to write enable, t <sub>su(W)</sub> | 15  |        |     | 15        |     |      | กร   |

| Hold times, high- or low-level data                        | Data input with respect to write enable, th(D)                | 15  |        |     | 15        |     |      | ns   |

| (see Note 3 and Figure 2)                                  | Write select with respect to write enable, th(W)              | 5   |        |     | 5         |     |      | ns   |

| Latch time for new data, t <sub>latch</sub> (see Note 4)   |                                                               | 25  |        |     | 25        |     |      | ns   |

| Operating free-air temperature range, TA                   |                                                               | -55 |        | 125 | 0         |     | 70   | °c   |

- NOTES: 3. Write-select setup time will protect the data written into the previous address. If protection of data in the previous address is not required, t<sub>su(W)</sub> can be ignored as any address selection sustained for the final 30 ns of the write-enable pulse and during t<sub>h(W)</sub> will result in data being written into that location. Depending on the duration of the input conditions, one or a number of previous addresses may have been written into.

- 4. Latch time is the time allowed for the internal output of the latch to assume the state of new data. See Figure 2. This is important only when attempting to read from a location immediately after that location has received new data.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| D. C. M. C. C.  |                           |                | TEST CONDITIONS†                                                 |                                                   | V54LS1 | 70   | SN74LS170 |     |              |      |       |

|-----------------|---------------------------|----------------|------------------------------------------------------------------|---------------------------------------------------|--------|------|-----------|-----|--------------|------|-------|

|                 | PARAMETER                 |                | TEST CON                                                         | DITIONS                                           | MIN    | TYP‡ | MAX       | MIN | MIN TYP# MAX |      | TINU  |

| VIH             | High-level input voltage  |                |                                                                  |                                                   | 2      |      |           | 2   |              |      | V     |

| VIL             | Low-level input voltage   |                |                                                                  |                                                   |        |      | 0.7       |     |              | 0.8  | V     |

| VIK             | Input clamp voltage       |                | V <sub>CC</sub> = MIN,                                           | I <sub>1</sub> = -18 mA                           |        |      | -1.5      |     |              | -1.5 | V     |

| ЮН              | High-level output current |                | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max, | V <sub>OH</sub> = 5.5 V,<br>V <sub>IH</sub> = 2 V |        |      | 100       |     |              | 100  | μА    |

|                 |                           |                | V <sub>CC</sub> = MIN,                                           | I <sub>OL</sub> = 4 mA                            |        | 0.25 | 0.4       |     | 0.25         | 0.4  | V     |

| VOL             | Low-level output voltage  |                | V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = V <sub>IL</sub> max  | IOL = 8 mA                                        |        |      |           |     | 0.35         | 0.5  |       |

|                 | Input current at          | Any D, R, or W | 1/ - MAY                                                         | M = 7M                                            |        |      | 0.1       |     |              | 0.1  | mA    |

| H               | maximum input voltage     | GR or GW       | V <sub>CC</sub> = MAX,                                           | V <sub>1</sub> = 7 V                              |        |      | 0.2       |     |              | 0.2  | ] ""  |

|                 |                           | Any D, R, or W |                                                                  | V - 0.7.V                                         |        |      | 20        |     |              | 20   |       |

| чн              | High-level input current  | GR or GW       | V <sub>CC</sub> = MAX,                                           | $V_1 = 2.7 V$                                     |        |      | 40        |     |              | 40   | μA    |

|                 |                           | Any D, R, or W |                                                                  |                                                   |        |      | -0.4      |     |              | -0.4 | mA    |

| IL              | Low-level input current   | GR or GW       | V <sub>CC</sub> = MAX,                                           | $V_1 = 0.4 V$                                     |        |      | 0.8       |     |              | -0.8 | ] ""A |

| 1 <sub>CC</sub> | Supply current            |                | V <sub>CC</sub> = MAX,                                           | See Note 5                                        |        | 25   | 40        |     | 25           | 40   | mA    |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX, use the appropriate **√a**lue specified under recommended operating conditions.

‡All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

NOTE 5: I<sub>CC</sub> is measured under the following worst-case conditions: 4.5 V is applied to all data inputs and both enable inputs, all address inputs are ground, and all outputs are open.

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ} \text{C}$

| PARAMETER <sup>†</sup> | FROM<br>(INPUT) | TO<br>(OUTPUT)                 | TEST CONDITIONS                                   | MIN | TYP | MAX | UNIT |

|------------------------|-----------------|--------------------------------|---------------------------------------------------|-----|-----|-----|------|

| tPLH                   | Do-do-do        | A O                            | 0 15 - 5                                          |     | 20  | 30  | ns   |

| tPHL                   | Read enable     | Any Q                          | $C_L = 15 \text{ pF},$ $R_L = 2 \text{ k}\Omega,$ |     | 20  | 30  | '''  |

| <sup>t</sup> PLH       | Bood coloot     | Any Q                          | See Figures 1 and 2                               |     | 25  | 40  | ns   |

| <sup>†</sup> PHL       | Read select     | Ally C                         |                                                   |     | 24  | 40  | ] "  |

| tPLH .                 | Write enable    | Any Q                          | C <sub>L</sub> = 15 pF,                           |     | 30  | 45  | ns   |

| <sup>†</sup> PHL       | AALITE EURDIE   | Anya                           | $R_L = 2 k\Omega$ ,                               |     | 26  | 40  | ] "" |

| tPLH                   | D-4-            | A= O                           | See Figures 1 and 3                               |     | 30  | 45  | ns   |

| <sup>t</sup> PHL       | Data            | Data Any Q See Figures 1 and 3 |                                                   | 22  | 35  | ] " |      |

$<sup>^{\</sup>dagger} t_{PLH} = propagation delay time, low-to-high-level output$

# schematics of inputs and outputs

'LS170

'LS170

tpHL = propagation delay time, high-to-low-level output

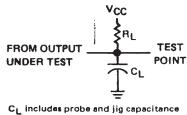

#### PARAMETER MEASUREMENT INFORMATION

C<sub>L</sub> includes probe and jig capacitance

LOAD CIRCUIT

#### FIGURE 1

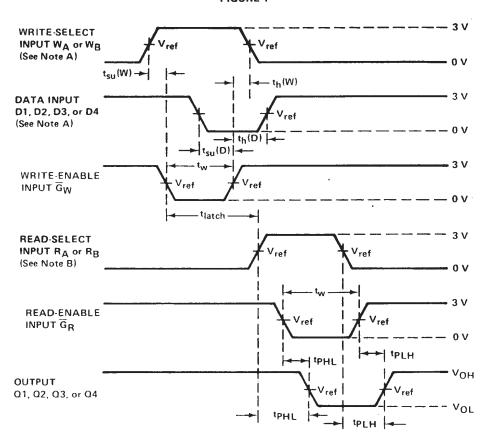

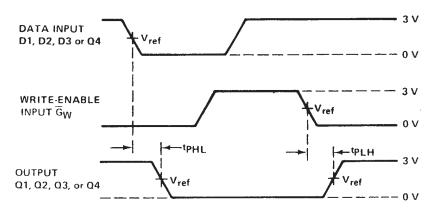

#### **VOLTAGE WAVEFORMS**

### FIGURE 2

NOTES: A. High-level input pulses at the select and data inputs are illustrated in Figure 2; however, times associated with low-level pulses are measured from the same reference points.

- B. When measuring delay times from a read-select input, the read-enable input is low. When measuring delay times from the read-enable input, both read-select inputs have been established at steady states.

- C. In Figure 3, each select address is tested. Prior to the start of each of the above tests, both write and read address inputs are stablized with W<sub>A</sub> = R<sub>A</sub> and W<sub>B</sub> = R<sub>B</sub>. During the test G<sub>B</sub> is low.

- D. Input waveforms are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_{out} \approx 50 \Omega$ , duty cycle  $\leq$  50%,  $t_r \leq$  10 ns and  $t_f \leq$  10 ns for '170, and  $t_r \leq$  15 ns and  $t_f \leq$  6 ns for 'LS170.

- E. For '170,  $V_{ref} = 1.5 \text{ V}$ ; for 'LS170,  $V_{ref} = 1.3 \text{ V}$ .

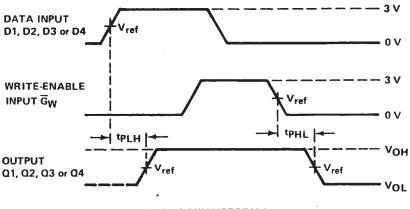

#### PARAMETER MEASUREMENT INFORMATION.

**VOLTAGE WAVEFORM 1**

**VOLTAGE WAVEFORM 2**

### FIGURE 3

- NOTES: A. High-level input pulses at the select and data inputs are illustrated in Figure 2; however, times associated with low-level pulses are measured from the same reference points.

- B. When measuring delay times from a read-select input, the read-enable input is low. When measuring delay times from the read-enable input, both read-select inputs have been established at steady states.

- C. In Figure 3, each select address is tested. Prior to the start of each of the above tests, both write and read address inputs are stabilized with  $W_A = R_A$  and  $W_B = R_B$ . During the test  $G_R$  is low.

- D. Input waveforms are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_{out} \approx 50 \Omega$ , duty cycle  $\leq$  50%,  $t_r \leq$  10 ns and  $t_f \leq$  10 ns for '170, and  $t_r \leq$  15 ns and  $t_f \leq$  6 ns for 'LS170.

- E. For '170,  $V_{ref} = 1.5 \text{ V}$ ; for 'LS170,  $V_{ref} = 1.3 \text{ V}$ .

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.