### PmodALS™ Reference Manual

Revised April 15, 2016 This manual applies to the PmodALS rev. A

#### **Overview**

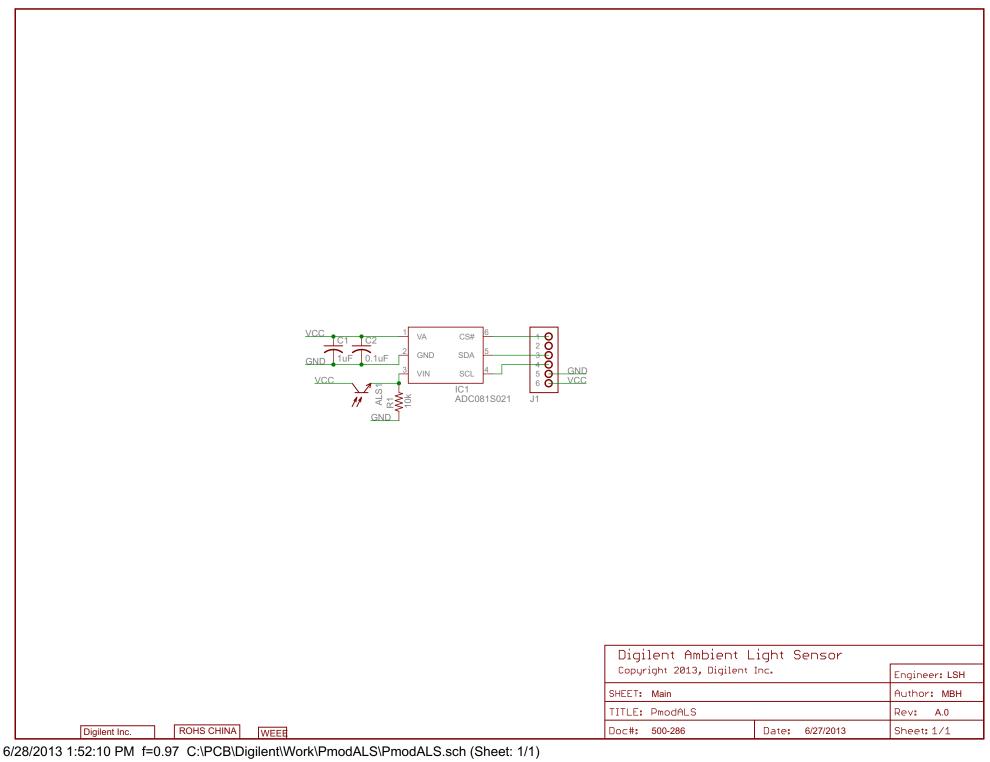

The Digilent PmodALS demonstrates light-to-digital sensing through a single ambient light sensor. Digilent engineers designed this Pmod™ around the Texas Instruments® ADC081S021 analog-to-digital converter and Vishay® Semiconductor's TEMT6000X01.

The PmodALS

#### Features include:

- Simple ambient light sensor

- Convert light to digital date with 8-bit resolution

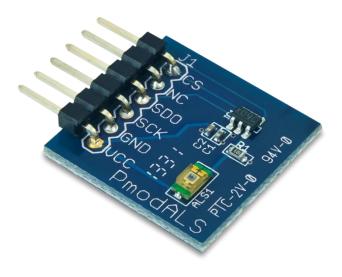

- Small PCB size for flexible designs 0.8 in ×  $0.8 \text{ in } (2.0 \text{ cm} \times 2.0 \text{ cm})$

- 6-pin Pmod port with SPI interface

- Follows Digilent Pmod Interface Specification Type 2

- Example code available in resource center

# **Functional Description**

The PmodALS utilizes a single ambient light sensor (ALS) for user input. The amount of light the ALS is exposed to determines the voltage level passed into the ADC, which converts it to 8-bits of data. A value of 0 indicates a low light level and a value of 255 indicates a high light level.

## 2 Interfacing with the Pmod

The PmodALS communicates with the host board via the SPI protocol. Since the on-board analog-to-digital converter is a read-only module, the only wires in the SPI protocol that are required are the Chip Select, Master-In-Slave-Out, and Serial Clock lines. The location of each of these lines on the Pmod header are shown in the table below.

#### 2.1 Pinout Description Table

| Pin | Signal | Description            |

|-----|--------|------------------------|

| 1   | CS     | Chip Select            |

| 2   | NC     | Not Connected          |

| 3   | SDO    | Master-In-Slave_out    |

| 4   | SCK    | Serial Clock           |

| 5   | GND    | Power Supply Ground    |

| 6   | VCC    | Power Supply (3.3V/5V) |

Table 1. Connector J1: Pin descriptions as labeled on the Pmod.

The PmodALS reports to the host board when the ADC081S021 is placed in normal mode by bringing the CS pin low, and delivers a single reading in 16 SCLK clock cycles. The PmodALS requires the frequency of the SCLK to be between 1 MHz and 4 MHz. The bits of information, placed on the falling edge of the SCLK and valid on the subsequent rising edge of SCLK, consist of three leading zeroes, the eight bits of information with the MSB first, and four trailing zeroes.

Any external power applied to the PmodALS must be within 2.7V and 5.25V; however, it is recommended that Pmod is operated at 3.3V.

# 3 Physical Dimensions

The pins on the pin header are spaced 100 mil apart. The PCB is 0.8 inches long on the sides parallel to the pins on the pin header and 0.8 inches long on the sides perpendicular to the pin header.