#### PmodGYRO™ Reference Manual

Revised April 12, 2016

This manual applies to the PmodGYRO rev. A

#### **Overview**

The PmodGYRO is a 3-axis gyroscope powered by the STMicroelectronics L3G4200D. By communicating with the chip through SPI or I<sup>2</sup>C, users may configure the module to report angular momentum at a resolution of up to 2000 dps at an output rate up to 800Hz.

The PmodGYRO.

#### Features include:

- 3-axis MEMS digital gyroscope with high shock survivability

- Get angular momentum data with user selectable resolution (250/500/2000dps)

- Two customizable interrupt pins

- User configurable signal filtering

- Power-down and Sleep modes

- Small PCB size for flexible designs 1.0 in × 0.8 in (2.5 cm × 2.0 cm)

- 12-pin Pmod port with SPI interface and additional I<sup>2</sup>C interface

- Library and example code available in <u>resource</u> center

## 1 Functional Description

The PmodGYRO utilizes <u>ST L3G4200D gyroscope</u> to provide motion sensing data on each of the three Cartesian axes. Users may configure both the resolution and filtering options for the measured data.

# 2 Interfacing with the Pmod

The PmodGYRO communicates with the host board via the SPI or I<sup>2</sup>C protocols. By driving the Chip Select (CS) line to a logic low voltage state, SPI mode is enabled. The first byte sent over SPI informs the on-board chip if a read or write command is going to be issued, if the register address should be incremented after a particular command has been completed, and the 5 bit address of the register that is to be written to.

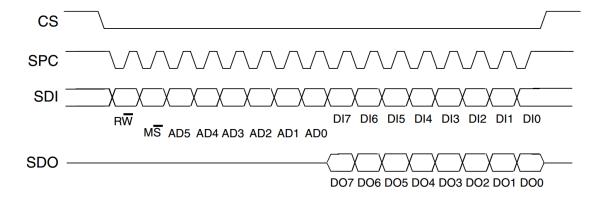

An example timing diagram for SPI read and writes from the L3G4200D datasheet is provided below:

Figure 1. Timing diagram.

Correspondingly, if the CS line is left at a high voltage state by an internal pull-up resistor, the I<sup>2</sup>C mode of the PmodGYRO is enabled. The on-board chip has two possible slave address in the form of 110100x where x is the voltage state of the Master-In-Slave-Out (MISO) pin on the SPI header. After the slave address and the read or write bit has been transmitted and the message was acknowledged, a 7-bit register address can then be transmitted. The most significant bit (the first bit of the 8-bit of the transfer) indicates if multiple bytes of information are to be transferred.

An example transfer scheme for a master device reading multiple bytes of data from the PmodGYRO is provided below:

| Master                              | Slave |

|-------------------------------------|-------|

| Start                               |       |

| Slave address and<br>Write bit      |       |

|                                     | ACK   |

| Multi-byte bit and register address |       |

|                                     | ACK   |

| Restart                             |       |

| Slave address and read bit          |       |

|                                     | ACK   |

|                                     | Data  |

| ACK                                 |       |

|                                     | Data  |

| ACK                                 |       |

|                                     | Data  |

| NACK                                |       |

| Stop                                |       |

Table 1. Example transfer scheme.

Data is recorded and stored within the registers of the L3G4200D in degrees per second (dps). Correspondingly, a measured value of 360 dps is equivalent to 60 rpm. Users can retrieve data from the PmodGYRO by following the provided code example.

### 2.1 Pinout Description Table

| Header J1 |        |                                 |     |        |                                 |  |

|-----------|--------|---------------------------------|-----|--------|---------------------------------|--|

| Pin       | Signal | Description                     | Pin | Signal | Description                     |  |

| 1         | ~CS    | Chip Select                     | 7   | INT1   | Interrupt 1                     |  |

| 2         | MOSI   | Master-Out-Slave-<br>In         | 8   | INT2   | Interrupt 2                     |  |

| 3         | MISO   | Master-In-Slave-<br>Out         | 9   | (NC)   | Not Connected                   |  |

| 4         | SCLK   | Serial Clock                    | 10  | (NC)   | Not Connected                   |  |

| 5         | GND    | Power Supply<br>Ground          | 11  | GND    | Power Supply<br>Ground          |  |

| 6         | VCC    | Positive Power<br>Supply (3.3V) | 12  | VCC    | Positive Power<br>Supply (3.3V) |  |

| Header J2 |        |                                 |  |  |

|-----------|--------|---------------------------------|--|--|

| Pin       | Signal | Description                     |  |  |

| 1,<br>5   | SCL    | Serial Clock                    |  |  |

| 2,<br>6   | SDA    | Serial Data                     |  |  |

| 3,<br>7   | GND    | Power Supply<br>Ground          |  |  |

| 4,<br>8   | VCC    | Positive Power<br>Supply (3.3V) |  |  |

|           |        |                                 |  |  |

|           |        |                                 |  |  |

Table 2. Pinout description table.

Any external power applied to the PmodGYRO must be within 2.4V and 3.6V; however, it is recommended that Pmod is operated at 3.3V.

# 3 Physical Dimensions

The pins on the pin header are spaced 100 mil apart. The PCB is 1 inch long on the sides parallel to the pins on the pin header and 0.8 inches long on the sides perpendicular to the pin header.

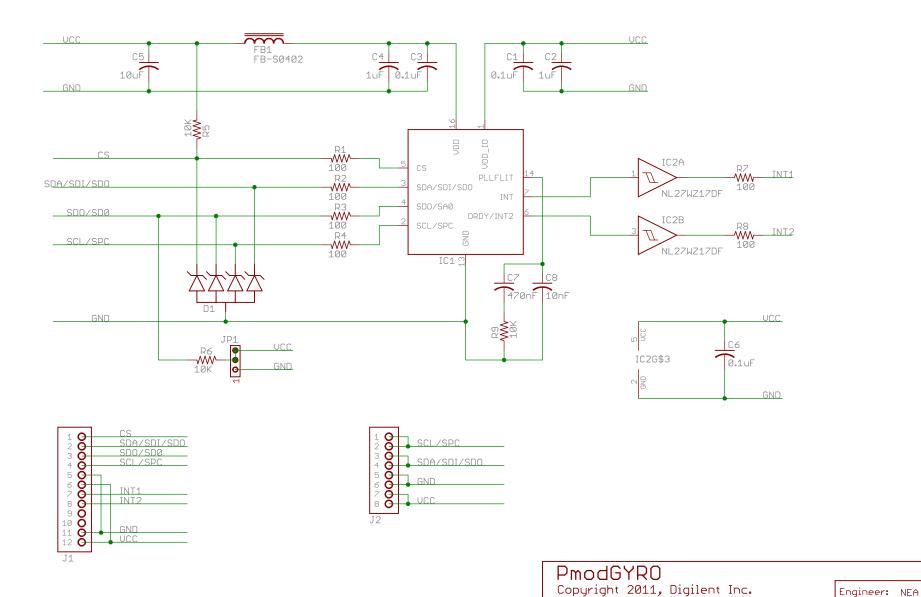

SHEET:

TITLE: PmodGYRO

Date:

3/31/2011

Doc#: 500-215

Author:

Sheet: 1/1

Rev:

PΑ

Α