# PCI-9524

# 24-Bit Precision Load Cell Input Card

# **User's Manual**

**Manual Revision: 2.02**

Revision Date: August 26, 2008

**Part No:** 50-11236-1010

Recycled Pape

**Advance Technologies; Automate the World.**

# **Revision History**

| Revision | Release Date | Description of Change(s)            |

|----------|--------------|-------------------------------------|

| 2.00     | 2008/04/09   | Document Created<br>Initial Release |

| 2.01     | 2008/05/30   | Minor revision                      |

| 2.02     | 2008/08/26   | Correct typo                        |

# **Preface**

# Copyright 2008 ADLINK TECHNOLOGY INC.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### **Disclaimer**

The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

# **Environmental Responsibility**

ADLINK is committed to fulfill its social responsibility to global environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE) directive. Environmental protection is a top priority for ADLINK. We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little impact on the environment as possible. When products are at their end of life, our customers are encouraged to dispose of them in accordance with the product disposal and/or recovery programs prescribed by their nation or company.

#### **Trademarks**

PC, PS/2, and VGA are registered trademarks of International Business Machines Corp. Borland<sup>®</sup>, Borland<sup>®</sup> C, C++ Builder<sup>®</sup>, and Delphi<sup>®</sup> are registered trademarks of the Borland Software Corporation. LabVIEW<sup>TM</sup> is a trademark of National Instruments Corporation. Microsoft<sup>®</sup>, Visual Basic<sup>®</sup>, Visual C++<sup>®</sup>, Windows<sup>®</sup>

Preface iii

98, Windows<sup>®</sup> NT, Windows<sup>®</sup> 2000, Windows<sup>®</sup> XP, and Windows<sup>®</sup> Vista<sup>®</sup> are registered trademarks of Microsoft<sup>®</sup> Corporation. PCI™, is a registered trademark of the Peripheral Component Interconnect Special Interest Group (PCI-SIG).

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

iv Preface

# **Using this Manual**

### **Audience and Scope**

The PCI-9524 User's Manual is intended for hardware technicians and systems operators with knowledge of installing, configuring and operating industrial grade PCI cards.

#### **Manual Organization**

This manual is organized as follows:

**Preface:** Presents important copyright notifications, disclaimers, trademarks, and associated information on the proper understanding and usage of this document and its associated product(s).

**Chapter 1, Introduction:** Introduces the PCI-9524, its features, applications, specifications and operating software environment.

**Chapter 2, Installation:** Describes how to install the PCI-9524 into your chassis and basic PCI configuration settings.

**Chapter 3, Signal Connections:** Describes signal connections between PCI-9524 and external devices.

**Chapter 4, Operation Theory:** Describes A/D and D/A conversions, pulse-commands, encoder inputs and isolated digital I/O signals to assist users in understanding how to configure and program the cPCI-9524.

**Chapter 5, Calibration:** Presents the calibration process to minimize measurement and output errors.

**Important Safety Instructions:** Presents safety instructions all users must follow for the proper setup, installation and usage of equipment and/or software.

**Warranty Information:** Presents important warranty information for users/manufacturers rights and responsibilities regarding ADLINK products and services.

Preface v

#### Conventions

Take note of the following conventions used throughout this manual to make sure that users perform certain tasks and instructions properly.

Additional information, aids, and tips that help users perform tasks.

Information to prevent *minor* physical injury, component damage, data loss, and/or program corruption when trying to complete a task.

Information to prevent **serious** physical injury, component damage, data loss, and/or program corruption when trying to complete a specific task.

vi Preface

## **Getting Service**

Contact us should you require any service or assistance.

#### ADLINK TECHNOLOGY INC. (HEADQUARTERS)

Web Site: http://www.adlinktech.com Sales & Service: service@adlinktech.com

Telephone No.: +886-2-8226-5877 Fax No.: +886-2-8226-5717

Mailing Address: 9F No. 166 Jian Yi Road, Chungho City,

Taipei 235, Taiwan

#### ADLINK TECHNOLOGY AMERICA INC.

Sales & Service: info@adlinktech.com Toll-Free: +1-866-4 ADLINK Fax No.: +1-949-727-2099

Mailing Address: 8900 Research Drive, Irvine,

CA 92618, USA

#### **ADLINK TECHNOLOGY CO. LTD. (BEIJING)**

Sales & Service: market@adlinktech.com Telephone No.: +86-10-5885-8666 Fax No.: +86-10-5885-8625

Mailing Address: Rm. 801, Power Creative E, No. 1, B/D

Shang Di East Rd. Beijing, 100085 China

# ADLINK TECHNOLOGY CO. LTD. (SHANGHAI)

Sales & Service: market@adlinktech.com Telephone No.: +86-21-6495-5210 Fax No.: +86-21-5450-0414

Mailing Address: 4F, Bldg. 39, No.333 Qinjiang Road,

Cao He Jing High-Tech Park Shanghai, 200233 China

# **ADLINK TECHNOLOGY CO. LTD. (SHENZHEN)**

Sales & Service: market@adlinktech.com

Telephone No.: +86-755-2643-4858

Fax No.: +86-755-2664-6353

Mailing Address: 2F, C Block, Bld. A1,

Cyber-Tech Zone, Gao Xin Ave. Sec. 7,

High-Tech Industrial Park S., Shenzhen, 518054 China

Preface vii

#### **ADLINK TECHNOLOGY INC. (EUROPEAN Liaison Office)**

Sales & Service: emea@adlinktech.com Telephone No.: +49-211-495-5552 Fax No.: +49-211-495-5557 Mailing Address: Nord Carree 3, 40477

Düsseldorf, Germany

#### ADLINK TECHNOLOGY JAPAN CORP.

Sales & Service japan@adlinktech.com

Telephone No. +81-3-4455-3722

Fax No. +81-3-5333-6040

Mailing Address Asahiseimei Hatagaya Bld. 8Fl. 1-1-2

Hatagaya Shibuya-ku, Tokyo, Japan

#### ADLINK TECHNOLOGY INC. (SOUTH KOREA Liaison Office)

Sales & Service: korea@adlinktech.com

Telephone No.: +82-2-2057-0565

Fax No.: +82-2-2057-0563

Mailing Address: #402, Dongsung B/D, 60-12,

Nonhyeon-dong Gangnam-gu, Seoul, 135-010, South Korea

#### ADLINK TECHNOLOGY SINGAPORE PTE. LTD.

Sales & Service: singapore@adlinktech.com

Telephone No.: +65-6844-2261 Fax No.: +65-6844-2263

Mailing Address: 84 Genting Lane #07-02A,

Cityneon Design Center,

Singapore 349584

# ADLINK TECHNOLOGY SINGAPORE PTE. LTD. (INDIA Liaison Office)

Sales & Service: india@adlinktech.com

Telephone No.: +91-80-6560-5817

Fax No.: +91-80-2244-3548

Mailing Address: No. 1357, Ground Floor, "Anupama",

Aurobindo Marg JP Nagar (Ph-1) Bangalor, Karnataka 560078, India

viii Preface

# **Table of Contents**

| P  | CI-95  | 24      |                                      | i    |

|----|--------|---------|--------------------------------------|------|

| R  | evisi  | on H    | istory                               | ii   |

| Pı | refac  | е       |                                      | iii  |

| Ta | able ( | of Co   | ntents                               | ix   |

| Li | st of  | Figu    | res                                  | xiii |

| Li | st of  | Tabl    | es                                   | xv   |

| 1  | Intro  | oduc    | tion                                 | 1    |

|    | 1.1    | Fea     | itures                               | 2    |

|    | 1.2    | App     | lications                            | 2    |

|    | 1.3    | Spe     | ecifications                         | 3    |

|    | 1.4    | Sof     | tware Support                        | 19   |

| 2  | Get    | ting \$ | Started                              | 21   |

|    | 2.1    | Inst    | allation Environment                 | 21   |

|    | 2.2    | Pac     | kage Contents                        | 22   |

|    | 2.3    | PCI     | -9524 Layout                         | 23   |

|    | 2.4    | Inst    | alling the Card                      | 24   |

|    | 2.5    | PCI     | Configuration                        | 25   |

| 3  | Sign   | nal C   | onnections                           | 27   |

|    | 3.1    | Cor     | nnectors & Pin Assignments           | 27   |

|    | 3.2    | Ana     | log Input Signal Connections         | 33   |

|    | 3      | .2.1    | Signal Sources                       | 33   |

|    | 3      | .2.2    | Input Configurations                 | 33   |

|    | 3      | .3.1    | Signal Sources and Terminal Devices  | 38   |

|    | 3      | .3.2    | Connecting to/from External Encoders | 40   |

|   | 3.3.5     | Interfacing Isolated DI with External Devices | 45 |

|---|-----------|-----------------------------------------------|----|

| 4 | Operation | on Theory                                     | 47 |

|   | 4.1 PC    | I-9524 Function Diagram                       | 47 |

|   | 4.2 Ana   | alog Input Channels                           | 48 |

|   | 4.2.1     | Signal Acquisition and Processing Flow        | 48 |

|   | 4.2.2     | How to Define a 1 in 200,000 Count Resolution |    |

|   | 4.2.3     | Data Rate versus Sampling Rate                | 51 |

|   | 4.2.4     | Auto-scan, Multiplexing and Settling Time     | 51 |

|   | 4.2.5     | Power Line Noise Rejection                    | 53 |

|   | 4.2.6     | Excitation and Remote-sensing                 | 54 |

|   | 4.2.7     | Thermal EMF, 1/f Noise and Auto-zero          | 55 |

|   | 4.2.8     | Warm-up Requirement                           | 58 |

|   | 4.2.9     | Post-processing IIR Digital Filter            | 58 |

|   | 4.2.10    | RAW Data Format                               | 61 |

|   | 4.2.11    | AD Data Format                                | 62 |

|   | 4.2.12    | Data Transfer Modes                           | 64 |

|   | 4.2.13    | Trigger Modes                                 | 66 |

|   | 4.3 D/A   | A Conversion                                  | 67 |

|   | 4.4 Iso   | lated Encoder Input Channels                  | 67 |

|   | 4.5 Iso   | lated Pulse-Command Generator                 | 69 |

|   | 4.6 Iso   | lated Digital I/O                             | 69 |

|   | 4.6.1     | Isolated Digital Inputs                       | 70 |

|   | 4.6.2     | Isolated Digital Outputs                      | 70 |

|   | 4.7 Trig  | gger Sources                                  | 70 |

|   | 4.7.1     | Software-Trigger                              | 70 |

|   | 4.7.2     | External Digital Trigger                      | 70 |

|   | 4.7.3     | Pulse Comparator Trigger                      | 71 |

|   | 4.7.4     | Position Comparator Trigger                   | 72 |

| 5 | Calibrati | ion                                           | 73 |

| _ |           | ading Calibration Constants                   |    |

|   |           | G =                                           | •  |

| ADLINK Technology Inc.<br>Copyright 2008 |                              | User's Manu |

|------------------------------------------|------------------------------|-------------|

| 5.2                                      | Auto-calibration             | 74          |

| 5.3                                      | Saving Calibration Constants | 74          |

| Importa                                  | ant Safety Instructions      | 75          |

Table of Contents xi

This page intentionally left blank.

xii Table of Contents

# **List of Figures**

| Figure 1-1:  | PCI-9524 Product Image                             | 1    |

|--------------|----------------------------------------------------|------|

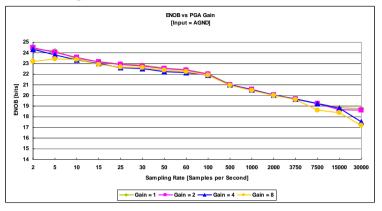

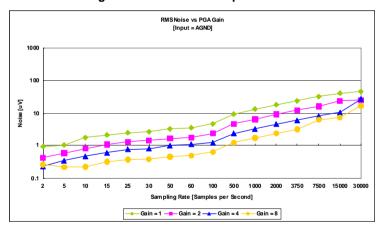

| Figure 1-2:  | Effective-number-of-bits vs. Gain                  | 9    |

| Figure 1-3:  | RMS Noise in µV vs. Gain                           | 9    |

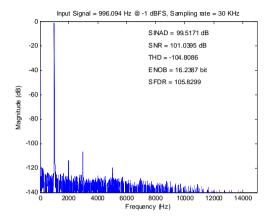

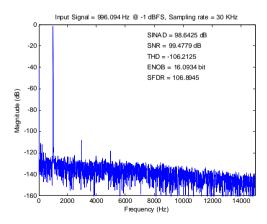

| Figure 1-4:  | Spectral Response ±10 V range,                     |      |

|              | 0.996094 Hz sine wave, -1 dB FS                    | . 10 |

| Figure 1-5:  | Spectral Response ±5 V range,                      |      |

|              | 0.996094 Hz sine wave, -1 dB FS                    | . 10 |

| Figure 1-6:  | Spectral Response ±2.5 V range,                    |      |

|              | 0.996094 Hz sine wave, -1 dB FS                    | . 11 |

| Figure 1-7:  | Spectral Response ±1.25 V range,                   |      |

|              | 0.996094 Hz sine wave, -1 dB FS                    |      |

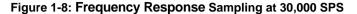

| Figure 1-8:  | Frequency Response Sampling at 30,000 SPS          |      |

| Figure 1-9:  | Frequency Response Sampling at 15,000 SPS          | . 12 |

| Figure 1-10: | Frequency Response Sampling below 15,000 SPS       | . 13 |

| Figure 2-1:  | PCI-9524 PCB Layout and Mechanical Drawing         | . 23 |

| Figure 3-1:  | CN1 Connector & Pin Assignments                    | . 28 |

| Figure 3-4:  | Connecting to a four-terminal load-cell transducer |      |

|              | using a four-wire connection                       | . 34 |

| Figure 3-5:  | Connecting to a six-terminal load-cell transducer  |      |

|              | using a six-wire connection                        | . 35 |

| Figure 3-6:  | Connecting to a four-terminal load-cell transducer |      |

|              | using a six-wire connection                        |      |

| Figure 3-7:  | Ground-referenced source and differential input    | . 36 |

| Figure 3-8:  | Floating source and differential input             | . 37 |

| Figure 3-9:  | Connecting to an external encoder                  |      |

|              | with NPN sink drivers                              | . 40 |

| Figure 3-10: | Connecting to an external encoder                  |      |

|              | with PNP source drivers                            | . 40 |

| Figure 3-11: | Connecting to an external encoder                  |      |

|              | with push-pull source drivers                      | . 41 |

| Figure 3-12: | Connecting to an external encoder                  |      |

|              | with differential line-drivers                     | . 41 |

| Figure 3-13: | Connecting to an external servo-amplifier          |      |

|              | with opto-coupler inputs                           | . 42 |

| Figure 3-14: | Connecting to an external servo-amplifier          |      |

|              | with differential line-receivers                   | . 42 |

| Figure 3-15: | Connecting to an external resistive load           |      |

|              | from the isolated DO sink driver                   | . 43 |

List of Figures xiii

| Figure 3-16 | 6: Connecting to an external inductive load  |    |

|-------------|----------------------------------------------|----|

|             | from an isolated DO sink driver              | 44 |

| Figure 3-17 | 7: Connecting to a low-side push button      | 45 |

| Figure 3-18 | 3: Connecting to an external sink driver     | 46 |

| Figure 4-1: | PCI-9524 Function Diagram                    | 47 |

| Figure 4-2: | Signal acquisition and data processing flow  |    |

|             | for transducer input channels                | 48 |

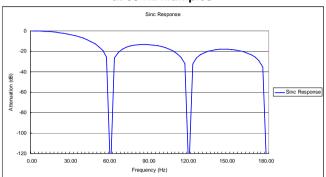

| Figure 4-3: | SINC Filter Power Line Noise Rejection       |    |

|             | at 60 Hz Multiples                           | 54 |

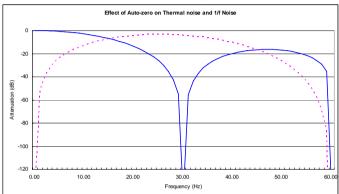

| Figure 4-4: | The Effect of Auto-zero on Thermal Noise and |    |

|             | 1/f Noise, ADC running at 60 SPS             | 57 |

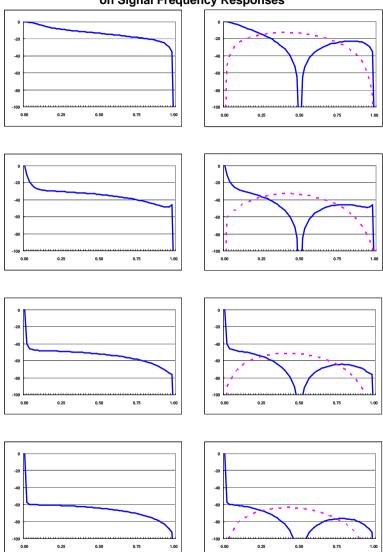

| Figure 4-5: | Digital Filter Tap Length Effects            |    |

|             | on Signal Frequency Responses                | 59 |

| Figure 4-6: | Linked List of PCI address DMA descriptors   | 65 |

| Figure 4-7: | Post trigger                                 | 66 |

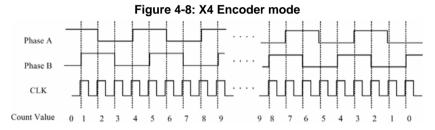

| Figure 4-8: | X4 Encoder mode                              | 68 |

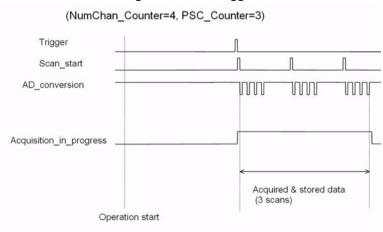

| Figure 4-9: | External digital trigger                     | 71 |

|             |                                              |    |

xiv List of Figures

# **List of Tables**

| Table | 1-1:  | -3dB small signal bandwidth: (Typical, 25°C)         | . 4 |

|-------|-------|------------------------------------------------------|-----|

| Table | 1-2:  | System Noise (including Quantization, Typical, 25°C) | . 4 |

| Table | 1-3:  | Transducer Input Impedance                           |     |

| Table | 1-4:  | Transducer CMRR (DC to 60 Hz, Typical 25°C)          | . 5 |

| Table | 1-5:  | Settling Error: (Typical, 25°C)                      |     |

| Table | 1-6:  | Programmable input range and gain                    | . 7 |

| Table | 1-7:  | -3dB small signal bandwidth vs. input range          | . 7 |

| Table | 1-8:  | -3dB small signal bandwidth vs. sampling rates,      |     |

|       |       | in ±10V range                                        | . 8 |

|       |       | General Purpose Input Impedance                      |     |

| Table | 1-10: | General Purpose CMRR (DC to 60 Hz, Typical, 25°C).   | 13  |

| Table | 1-11: | Settling Error: (Typical, 25°C)                      | 14  |

| Table | 3-1:  | I/O Signal Descriptions                              | 31  |

| Table | 4-1:  | Data Rates vs. Multiplexing, Auto-zero &             |     |

|       |       | ADC Sampling Rates, in Samples-per-second (SPS)      |     |

| Table | 4-2:  | Temperature Coefficient of different metal junctions | 56  |

| Table | 4-3:  | Default Threshold Values (ADC counts) vs. ADC        |     |

|       |       | Sampling Rates                                       |     |

| Table |       | RAW Data Format                                      | 61  |

| Table | 4-5:  | Bipolar analog input ranges and                      |     |

|       |       | output digital codes for transducer input channels   | 63  |

| Table | 4-6:  | Bipolar analog input ranges and                      |     |

|       |       | AD codes for general purpose input channels          |     |

| Table | 4-7:  | Bipolar output code table                            | 67  |

List of Tables xv

This page intentionally left blank.

xvi List of Tables

# 1 Introduction

The ADLINK PCI-9524 is a 24-bit high-resolution multifunction DAQ card capable of up to 30 kS/s sampling rate, providing 4-CH load-cell transducer input channels, and 4-CH general purpose analog input. In addition, the PCI-9524 comes with a 2-CH 16-bit analog output, isolated motion I/O and digital I/O. The highly integrated function makes the PCI-9524 the ideal solution for combined data acquisition and motion control functionalities. Ideal for manufacturing, laboratory research, and factory automation, the PCI-9524 comes with all the features and performance you need at an affordable price.

Figure 1-1: PCI-9524 Product Image

#### 1.1 Features

PCI-9524 24-bit multifunction DAQ card provides the following advanced features:

- ► Supports 32-bit 3.3 V or 5V PCI bus

- ▶ Load-cell transducer input channels

- Auto-zero capability

- □ Up to 30 kS/s sampling rate without auto-zero

- ▷ IIR digital filter for post-processing

- ► General purpose analog input channels

- > 4-CH differential analog input

- □ Up to 30 kS/s sampling rate

- ▶ 2-CH 16-bit analog output

- ▶ 3-CH opto-isolated pulse-command output, supporting AB phase, CW/CCW, CLK/DIR modes

- ➤ 3-CH opto-isolated encoder input, supports AB phase inputs in quadrature mode

- ▶ 8-CH opto-isolated digital inputs

- ▶ 8-CH opto-isolated digital outputs with N-MOS sink drivers

- Auto-calibration

# 1.2 Applications

- ▶ Materials Testing Systems

- ▶ Precision Weighting Systems

- ▶ Automotive Testing

- ▶ Process Control

- Laboratory Automation

- Biotech Measurements

# 1.3 Specifications

## **Analog Input (AI) for Transducers**

- ▶ Number of channels: (programmable)

- A/D converter:

- Maximum sampling rate:

#### Without Auto-zero

## With Auto-zero

- ≥ 819 samples/s (single channel or multiplexed/scanning)

- ▶ Resolution:

- ≥ 24-bit

- ► Input coupling: DC

- Input range and gain:

- A fixed gain of 25x

- ▶ Operational common-mode input range:

- $\triangleright$  -2 V to +6 V

- ► Transducer Excitation Voltage Sources:

- > 4-CH differential output

- > 10 V or 2.5 V selectable (all 4-CH share same settings)

- ▷ Driving up to four 120-ohm load-cells

- Short-circuit protection

- ▶ Remote-sense input:

- 4-CH differential input

- V to 10 V operating input range

- Overvoltage protection:

# Transducer inputs

- Power on: +28.7 V to -35.7 V (continuous)

- Power off: ±15 V (continuous)

## Remote-sense inputs:

$\triangleright$  Power on: -40 V to +55 V (continuous)

Power off: -40 V to +55 V (continuous)

► FIFO buffer size: 1024 samples (1024 x 32 bits)

▶ Data transfers:

▷ Programmed I/O

Table 1-1: -3dB small signal bandwidth: (Typical, 25°C)

| Input Range | Bandwidth (-3dB) |

|-------------|------------------|

| ±200 mV     | 2,730 Hz         |

Table 1-2: System Noise (including Quantization, Typical, 25°C)

| Input<br>Range | Data<br>Rate in<br>SPS | System<br>Noise in<br>LSB <sub>rms</sub> | RMS<br>Res. in<br>Bits<br>(ENOB) | Peak<br>Res. in<br>Bits | RMS Res<br>in µV | Peak<br>Res. in<br>μV |

|----------------|------------------------|------------------------------------------|----------------------------------|-------------------------|------------------|-----------------------|

|                | 1.25                   | 0.5                                      | 23.0                             | 21.0                    | 0.013            | 0.053                 |

|                | 2.5                    | 0.6                                      | 22.8                             | 20.4                    | 0.014            | -0.079                |

|                | 5.0                    | 0.6                                      | 22.7                             | 20.4                    | 0.016            | 0.079                 |

|                | 7.5                    | 0.7                                      | 22.6                             | 20.0                    | 0.017            | 0.079                 |

| ±200 mV        | 12                     | 0.9                                      | 22.2                             | 19.7                    | 0.023            | 0.159                 |

| ±200 IIIV      | 15                     | 0.8                                      | 22.3                             | 19.7                    | 0.020            | 0.132                 |

|                | 24                     | 1.2                                      | 21.8                             | 19.2                    | 0.031            | 0.212                 |

|                | 29                     | 1.1                                      | 21.9                             | 19.0                    | 0.030            | 0.185                 |

|                | 47                     | 1.9                                      | 21.1                             | 18.6                    | 0.037            | 0.291                 |

|                | 194                    | 2.9                                      | 20.5                             | 17.7                    | 0.078            | 0.583                 |

| Input<br>Range | Data<br>Rate in<br>SPS | System<br>Noise in<br>LSB <sub>rms</sub> | RMS<br>Res. in<br>Bits<br>(ENOB) | Peak<br>Res. in<br>Bits | RMS Res<br>in µV | Peak<br>Res. in<br>µV |

|----------------|------------------------|------------------------------------------|----------------------------------|-------------------------|------------------|-----------------------|

|                | 316                    | 3.7                                      | 20.1                             | 17.1                    | 0.101            | 0.742                 |

|                | 463                    | 5.5                                      | 19.6                             | 16.4                    | 0.146            | 1.113                 |

| ±200 mV        | 595                    | 6.9                                      | 19.2                             | 16.4                    | 0.185            | 1.351                 |

| ±200 111V      | 704                    | 8.9                                      | 18.9                             | 15.9                    | 0.243            | 1.748                 |

|                | 768                    | 10.9                                     | 18.6                             | 15.5                    | 0.306            | 2.305                 |

|                | 819                    | 12.6                                     | 18.4                             | 15.4                    | 0.328            | 2.331                 |

Test conditions: Rice Lake Load-cell Simulator IV set at 0mV/V output, 10V excitation and six-wire remote-sense connection, auto-zero enabled. The RMS resolution and peak resolution are calculated relative to full-scale input range of ±200mV.

Table 1-3: Transducer Input Impedance

| Normal Power On | Power Off | Overload |

|-----------------|-----------|----------|

| 1 GΩ    3 pF    | 1 ΚΩ      | 1 ΚΩ     |

Table 1-4: Transducer CMRR (DC to 60 Hz, Typical 25°C)

| Input Range | CMRR                       |

|-------------|----------------------------|

| ±200 mV     | 90 dB (Auto-zero Disabled) |

| ±200 IIIV   | 102 dB (Auto-zero Enabled) |

Table 1-5: Settling Error: (Typical, 25°C)

| Input Range | Condition            | Settling Error |

|-------------|----------------------|----------------|

| ±200 mV     | Scanning 200 mV step | max 0.01%      |

► Time-base source: Internal 40 MHz

▶ Trigger mode: post-trigger

▶ Offset error:

▷ Before calibration: ±0.5 mV typical

After calibration: ±0.001 mV typical (auto-zero disabled),

< ±0.001 mV typical (auto-zero enabled)

</p>

▶ Transfer Linearity:

Gain error:

Before calibration: ±1% typical

After calibration: ±0.5% typical

# Analog Input (AI) for General Purpose

► Number of channels: (programmable)

A/D converter:

► Maximum sampling rate:

> 30,000 samples/s (single channel)

Resolution:

≥ 24-bit

▶ Input coupling: DC

Table 1-6: Programmable input range and gain

| Bipolar Input Range | Gain |

|---------------------|------|

| ±10 V               | 1    |

| ±5 V                | 2    |

| ±2.5 V              | 4    |

| ±1.25 V             | 8    |

▶ Operational common-mode input range: ±13V

▶ Overvoltage protection:

Power on: ±30 V (continuous)

► FIFO buffer size: 1024 samples (1024 x 32 bits)

▶ Data transfers:

▷ Programmed I/O

► -3dB small signal bandwidth (Typical, 25°C)

Table 1-7: -3dB small signal bandwidth vs. input range

| Input Range | Bandwidth (-3dB) |

|-------------|------------------|

| ±10 V       | 5,800 Hz         |

| ±5 V        | 5,900 Hz         |

| ±2.5 V      | 5,900 Hz         |

| ±1.25 V     | 5,900 Hz         |

Table 1-8: -3dB small signal bandwidth vs. sampling rates, in ±10V range

| Sampling Rate<br>In Samples-per-second<br>(SPS) | Bandwidth (-3 dB) |

|-------------------------------------------------|-------------------|

| 2.5                                             | 1.1 Hz            |

| 5                                               | 2.2 Hz            |

| 10                                              | 4.4 Hz            |

| 15                                              | 6.6 Hz            |

| 25                                              | 11 Hz             |

| 30                                              | 13 Hz             |

| 50                                              | 22 Hz             |

| 60                                              | 26 Hz             |

| 100                                             | 44 Hz             |

| 500                                             | 220 Hz            |

| 1,000                                           | 440 Hz            |

| 2,000                                           | 880 Hz            |

| 3,750                                           | 1,600 Hz          |

| 7,500                                           | 3,000 Hz          |

| 15,000                                          | 4,800 Hz          |

| 30,000                                          | 5,800 Hz          |

# System Noise (LSBrms, including Quantization, Typical, 25°C)

Figure 1-2: Effective-number-of-bits vs. Gain

Figure 1-3: RMS Noise in µV vs. Gain

Test conditions: RMS resolution and peak resolution are calculated relative to the full-scale range of their gain settings, using internal calibration voltage references.

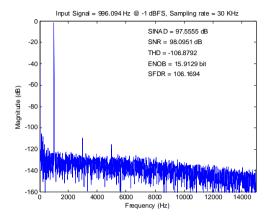

# Spectral Response (At 30,000-SPS, Typical, 25°C)

Figure 1-4: Spectral Response ±10 V range, 0.996094 Hz sine wave, -1 dB FS

Figure 1-5: Spectral Response ±5 V range, 0.996094 Hz sine wave, -1 dB FS

Figure 1-6: Spectral Response ±2.5 V range, 0.996094 Hz sine wave, -1 dB FS

Figure 1-7: Spectral Response ±1.25 V range, 0.996094 Hz sine wave, -1 dB FS

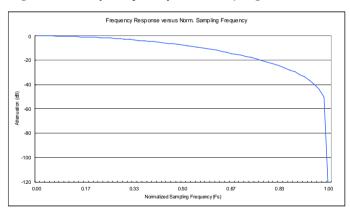

# Frequency Response (vs. normalized sampling frequencies):

Figure 1-9: Frequency Response Sampling at 15,000 SPS

Figure 1-10: Frequency Response Sampling below 15,000 SPS

Table 1-9: General Purpose Input Impedance

| Normal Power On | Power Off | Overload |

|-----------------|-----------|----------|

| 1 GΩ    3 pF    | 1 ΚΩ      | 1 ΚΩ     |

Table 1-10: General Purpose CMRR (DC to 60 Hz, Typical, 25°C)

| Input Range | CMRR  |

|-------------|-------|

| ±10 V       | 80 dB |

| ±5 V        | 86 dB |

| ±2.5 V      | 94 dB |

| ±1.25 V     | 98 dB |

Table 1-11: Settling Error: (Typical, 25°C)

| Input Range | Condition        | Settling Error |

|-------------|------------------|----------------|

| ±10 V       | Scanning 20 Vpp  | <0.0005%       |

| ±5 V        | Scanning 10 Vpp  | <0.0005%       |

| ±2.5 V      | Scanning 5 Vpp   | <0.0005%       |

| ±1.25 V     | Scanning 2.5 Vpp | <0.0005%       |

► Time-base source: Internal 40 MHz

► Trigger mode: post-trigger

Offset error:

▷ Before calibration: ±2 mV typical 25°C

▷ After calibration: ±0.1 mV typical 25°C

▶ Gain error:

▷ Before calibration: ±0.5% typical 25°C

▷ After calibration: ±0.01% typical 25°C

### **Analog Output (AO)**

▶ Number of channels: 2 analog voltage outputs

▶ D/A converter: DAC8812

Maximum update rate: 10 K sample/s

▶ Resolution: 16-bit

Data transfers: Programmed I/O

▶ Output range: ±10 V

► Settling time (0.1% of full scale): 2 µs

Slew rate: 15 V/µS

▶ Output coupling: DC

▶ Protection: Short-circuit to ground, indefinitely

Output impedance: 0.1 Ω max

Output driving: ±5 mA max.

▶ Stability: Any passive load, up to 1500 pF

▶ Power-on state: Around 0 V steady-state

Offset error:

Gain error:

▷ Before calibration: ±0.8% of output max.

After calibration: ±0.015% of output max.

### **Isolated Pulse Command Outputs**

- ▶ Number of channels: 3

- ▶ Output type: AM26LS31 differential line-driver

- Compliant to ANSI TIA/EIA-422-B and ITU Recommendation V.11 standards

- ▶ Logic Compatibility: 5V TTL with complementary output

- Output voltage:

- ► Programmable duty cycle: 1% to 99%

- ▶ Maximum pulse frequency: 1 MHz

- Direction control modes: CLK/DIR & CW/CCW

- ▶ Pulse counter: 1 to 16777215

- Pulse Comparator Trigger to initiate AI acquisition once condition is met

- ▶ Data transfers: Programmed I/O

#### Isolated Quadrature Encoder Inputs

- Number of channels: 3

- Input type: AB-Phase differential inputs

- Input impedance: 249 Ω || 220 pF

- Input voltage:

- Logic high: VIH = 3.8 V min.

- Maximum Encoder frequency: 1 MHz

- Decoder type: Quadrature, 4X resolution

- Decoder counts: -8388608 to +8388607

- Positional Comparator Trigger to initiate AI acquisition once condition is met

- Data transfers: Programmed I/O

### **Isolated Digital Inputs**

- Number of channels: 8

- ▶ Input type: Bipolar, resistive differential

- Input impedance: 2.7 KΩ || 250 pF

- Input voltage:

- Maximum input frequency: 5 KHz

- ▶ Data transfers: Programmed I/O

- ▶ Digital Trigger to initiate AD conversion on DI channel 0, with programmable detection polarity

### **Isolated Digital Outputs**

- ▶ Number of channels: 8

- Output type: N-Type MOSFET current sinker with a command ground

- ▶ Maximum external power-supply voltage: 60 V DC

- Drain-off leakage current: 10 μA

- Drain-on resistance: 75 mΩ

- Maximum drain current: 5 A DC

- Maximum toggling frequency: 5 KHz

- Data transfers: Programmed I/O

#### **Isolated Power Supplies**

▶ Number of channels: 2

Nominal output voltage

▷ ISO5VDD: 5 V ±0.05V

▷ ISOPWR: 5 V ±0.15V

► Output current (Pulse Command channels are unused)

ightharpoonup ISO5VDD: 160 mA max.

▷ ISOPWR: 16 mA max.

► Maximum output current (n<sup>th</sup> channel of Pulse Command channel is used)

▷ ISOPWR:1 6mA max.

### **Physical**

▶ Dimensions: 156 mm x 116 mm

▶ I/O connectors: two 68-pin SCSI-VHDCI connectors

# Power Requirement (typical, 25°C)

▶ +5 V DC: 2A

# **Operating Environment**

► Ambient temperature: 0°C to 45°C

▶ Relative humidity: 10% to 90% non-condensing

# **Storage Environment**

► Ambient temperature: -20°C to 80°C

▶ Relative humidity: 5% to 95% non-condensing

# 1.4 Software Support

#### **Software Support**

ADLINK provides versatile software drivers and packages to suit various user approach to building a system. Aside from programming libraries, such as DLLs, for most Windows-based systems, ADLINK also provides drivers for other application environment such as LabVIEW<sup>®</sup>.

All software options are included in the ADLINK All-in-One CD. Commercial software drivers are protected with licensing codes. Without the code, you may install and run the demo version for trial/demonstration purposes only up to two hours. Contact your ADLINK dealers if you want to purchase the software license.

### **Programming Library**

For customers who want to write their own programs, ADLINK provides the PCIS-DASK function library that is compatible with various operating systems.

#### PCIS-DASK

The PCIS-DASK includes device drivers and DLL for Windows 98/NT/2000/XP/Vista. DLL is binary compatible across Windows 98/NT/2000/XP/Vista. This means all applications developed with PCIS-DASK are compatible with these Windows operating systems. The developing environment may be VB, VC++, Delphi, BC5, or any Windows programming language that allows calls to a DLL. The PCIS-DASK user's and function reference manuals are in the ADLINK All-in-One CD. (\\Manual\\Software Package\\PCIS-DASK).

This page intentionally left blank.

# 2 Getting Started

This chapter further describes the PCI-9524; a proper installation environment, its package contents and basic information users should be aware of.

#### 2.1 Installation Environment

Whenever unpacking and preparing to install any equipment described in this manual, please refer to the *Important Safety Instructions* chapter of this manual.

Only install equipment in well lit areas on flat, sturdy surfaces with access to basic tools such as flat and cross head screwdrivers, preferably with magnetic heads as screws and standoffs are small and easily misplaced.

#### **Recommended Installation Tools**

- ▶ Phillips (cross-head) screwdriver

- Flat-head screwdriver

- ▶ Anti-static Wrist Strap

- Anti-static mat

ADLINK PCI-9524 DAQ cards are electro-static sensitive equipment that can be easily damaged by static electricity. The equipment must be handled on a grounded anti-static mat. The operator must wear an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the carton and packaging for damage. Shipping and handling could cause damage to the equipment inside. Make sure that

the equipment and its associated components have no damage before installing.

The equipment must be protected from static discharge and physical shock. Never remove any of the socketed parts except at a static-free workstation. Use the anti-static bag shipped with the product to handle the equipment and wear a grounded wrist strap when servicing.

## 2.2 Package Contents

Before continuing, check the package contents for any damage and check if the following items are included in the packaging:

- ▶ PCI-9524 Multi-function Data Acquisition Card

- ADLINK All-in-one Compact Disc

- ▶ Software Installation Guide

- ▶ PCI-9524 User's Manual

If any of these items are missing or damaged, contact the dealer from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the future.

**DO NOT** install or apply power to equipment that is damaged or if there is missing/incomplete equipment. Retain the shipping carton and packing materials for inspection. Please contact your ADLINK dealer/vendor immediately for assistance. Obtain authorization from your dealer before returning any product to ADLINK.

## 2.3 PCI-9524 Layout

CN<sub>2</sub> CN1 100.3 PCI Bus Interface Controller 0 11111111111 **FPGA** SSI Connector 98.42 106.68

Figure 2-1: PCI-9524 PCB Layout and Mechanical Drawing

## 2.4 Installing the Card

To install the card:

- 1. Turn off the system/chassis and disconnect the power plug from the power source.

- 2. Remove the system/chassis cover.

- 3. Select the PCI slot that you intend to use, then remove the bracket opposite the slot, if any.

- 4. Align the card connectors (golden fingers) with the slot, then press the card firmly until the card is completely seated on the slot.

- 5. Secure the card to the chassis with a screw.

- 6. Replace the system/chassis cover.

- 7. Connect the power plug to a power source, then turn on the system/chassis.

## 2.5 PCI Configuration

#### 1. Plug and Play:

As a plug and play component, the card requests an interrupt number via its PCI controller. The system BIOS responds with an interrupt assignment based on the card information and on known system parameters. These system parameters are determined by the installed drivers and the hardware load recognized by the system. Users can use the PCI\_SCAN software utility on the ADLINK All-in-One CD to read/check the system configuration.

#### 2. Configuration:

The board configuration is done on a board-by-board basis for all PCI boards on your system. Because configuration is controlled by the system and software, there is no jumper setting required for base-address, DMA, and interrupt IRQ.

The configuration is subject to change with every boot of the system as new boards are added or removed.

## 3. Trouble shooting:

If your system doesn't boot or if you experience erratic operation with your PCI board in place, it's likely caused by an interrupt conflict (perhaps the BIOS Setup is incorrectly configured). In general, the solution, once you determine it is not a simple oversight, is to consult the BIOS documentation that comes with your system.

This page intentionally left blank.

# 3 Signal Connections

This chapter describes the connectors of PCI-9524, and the signal connections between PCI-9524 and external devices. Please see Figure 3-1, Figure 3-2 and Figure 3-3 for details.

- ► CN1/CN2 68-pin VHDCI Connector

- ▶ SSI SSI Connector

## 3.1 Connectors & Pin Assignments

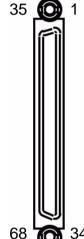

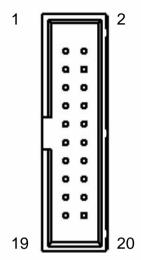

PCI-9524 is equipped with two 68-pin VHDCI connectors. They are used for digital input/output, analog input/output, etc. The SSI connector is used for system synchronization.

Figure 3-1: CN1 Connector & Pin Assignments

|                |           | Pin# | Pin# |           |

|----------------|-----------|------|------|-----------|

|                | AIO+      | 34   | 68   | AIO-      |

|                | VEX0+     | 33   | 67   | VEX0-     |

|                | VEX_SEN0+ | 32   | 66   | VEX_SEN0- |

|                | NC        | 31   | 65   | NC        |

|                | AI1+      | 30   | 64   | Al1-      |

|                | VEX1+     | 29   | 63   | VEX1-     |

|                | VEX_SEN1+ | 28   | 62   | VEX_SEN1- |

|                | NC        | 27   | 61   | NC        |

|                | Al2+      | 26   | 60   | Al2-      |

| 35 🔞 1         | VEX2+     | 25   | 59   | VEX2-     |

|                | VEX_SEN2+ | 24   | 58   | VEX_SEN2- |

|                | NC        | 23   | 57   | NC        |

|                | AI3+      | 22   | 56   | AI3-      |

|                | VEX3+     | 21   | 55   | VEX3-     |

|                | VEX_SEN3+ | 20   | 54   | VEX_SEN3- |

|                | NC        | 19   | 53   | NC        |

|                | AGND      | 18   | 52   | AGND      |

|                | AIH4      | 17   | 51   | AIL4      |

|                | AIH5      | 16   | 50   | AIL5      |

|                | AIH6      | 15   | 49   | AIL6      |

|                | AIH7      | 14   | 48   | AIL7      |

|                | AGND      | 13   | 47   | AGND      |

|                | AGND      | 12   | 46   | AGND      |

| 68 34          | AGND      | 11   | 45   | AGND      |

| 00 <b>6</b> 01 | AGND      | 10   | 44   | AGND      |

|                | AGND      | 9    | 43   | AGND      |

|                | AGND      | 8    | 42   | AGND      |

|                | AGND      | 7    | 41   | AGND      |

|                | AGND      | 6    | 40   | AGND      |

|                | AGND      | 5    | 39   | AGND      |

|                | AO0       | 4    | 38   | AGND      |

|                | AGND      | 3    | 37   | AGND      |

|                | AO1       | 2    | 36   | AGND      |

|                | AGND      | 1    | 35   | AGND      |

Figure 3-2: CN2 Connector & Pin Assignments

|    |     |            | Pin # | Pin# |           |

|----|-----|------------|-------|------|-----------|

|    |     | PULSE0_A+  | 34    | 68   | PULSE0_A- |

|    |     | PULSE0_B+  | 33    | 67   | PULSE0_B- |

|    |     | ISO5VDD    | 32    | 66   | ISOGND    |

|    |     | PULSE1_A+  | 31    | 65   | PULSE1_A- |

|    |     | PULSE1_B+  | 30    | 64   | PULSE1_B- |

|    |     | ISO5VDD    | 29    | 63   | ISOGND    |

|    |     | PULSE2_A+  | 28    | 62   | PULSE2_A- |

|    |     | PULSE2_B+  | 27    | 61   | PULSE2_B- |

|    |     | ISO5VDD    | 26    | 60   | ISOGND    |

| 35 | 1   | ENC0_A+    | 25    | 59   | ENC0_A-   |

|    | ' ' | ENC0_B+    | 24    | 58   | ENC0_B-   |

|    |     | ISOPWR     | 23    | 57   | ISOGND    |

|    |     | ENC1_A+    | 22    | 56   | ENC1_A-   |

|    |     | ENC1_B+    | 21    | 55   | ENC1_B-   |

|    |     | ISOPWR     | 20    | 54   | ISOGND    |

|    |     | ENC2_A+    | 19    | 53   | ENC2_A-   |

|    |     | ENC2_B+    | 18    | 52   | ENC2_B-   |

|    |     | ISOPWR     | 17    | 51   | ISOGND    |

|    |     | IDI0+      | 16    | 50   | IDI0-     |

|    |     | IDI1+      | 15    | 49   | IDI1-     |

|    |     | IDI2+      | 14    | 48   | IDI2-     |

|    |     | IDI3+      | 13    | 47   | IDI3-     |

|    |     | ISOPWR     | 12    | 46   | ISOGND    |

| 68 | 34  | IDI4+      | 11    | 45   | IDI4-     |

|    | 34  | IDI5+      | 10    | 44   | IDI5-     |

|    |     | IDI6+      | 9     | 43   | IDI6-     |

|    |     | IDI7+      | 8     | 42   | IDI7-     |

|    |     | ISOPWR     | 7     | 41   | ISOGND    |

|    |     | IDO0       | 6     | 40   | IDO1      |

|    |     | IDO2       | 5     | 39   | IDO3      |

|    |     | EXT_ISOPWR | 4     | 38   | ISOGND    |

|    |     | ISOPWR     | 3     | 37   | ISOGND    |

|    |     | IDO4       | 2     | 36   | IDO5      |

|    |     | IDO6       | 1     | 35   | IDO7      |

|    |     |            | •     |      |           |

Figure 3-3: SSI Connector & Pin Assignments

| PIN                   | Signal Name    |

|-----------------------|----------------|

| 11                    | SSI_AD_TRIG_IN |

| 1, 3, 5, 7, 9, 13, 15 | RSV            |

| 17                    | NC             |

| 19                    | NC             |

| 2, 4, 6,, 20          | DGND           |

Table 3-1: I/O Signal Descriptions

| Signal Name        | Reference          | Direction | Description                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------|--------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal Name        | Reference          | Direction |                                                                                                                                                                                                                                                                                                                                                     |  |

| AI <i>n</i> +      | AI <i>n</i> -      | Input     | Differential analog input channels.  Channels 0 to 3 are for load-cell transducer inputs (1) (2), and channels 4 to 7 are for general purpose analog inputs.                                                                                                                                                                                        |  |

| VEX <i>n</i> +     | VEX <i>n</i> -     | Output    | Analog outputs for transducer voltage excitation, in selectable ranges of 2.5V or 10V.  Connect one excitation source to only one load-cell transducer; sharing a common wiring between transducers will degrade gain accuracy.  Up to four 120-ohm load-cells can be connected to one PCI-9524. Load-cells with larger impedance can also be used. |  |

| VEX_SEN <i>n</i> + | VEX_SENn+          | Input     | Remote-sense analog inputs for transducer excitation sensing.  Always connect VEX_SENn+ to VEXn+, VEX_SENn- to VEXn-, and as close as possible to transducers excitation terminals.                                                                                                                                                                 |  |

| AGND               |                    |           | Analog ground.                                                                                                                                                                                                                                                                                                                                      |  |

| AOn                | AGND               | Output    | Single-ended analog output channel.                                                                                                                                                                                                                                                                                                                 |  |

| PULSE <i>n_</i> A+ | PULSE <i>n</i> _A- | Output    | Pulse-command differential voltage outputs. As Clock signal in single phase mode. As Clock signal in CLK/DIR mode. As CW signal in CW/CCW mode.                                                                                                                                                                                                     |  |

| PULSE <i>n_</i> B+ | PULSE <i>n</i> _B- | Output    | Pulse-command differential voltage outputs. Unused in single phase mode. As DIR signal in CLK/DIR mode. As CWW signal in CW/CCW mode.                                                                                                                                                                                                               |  |

| ENCn_A+            | ENC <i>n</i> _A-   | Input     | Encoder phase A inputs.                                                                                                                                                                                                                                                                                                                             |  |

| ENCn_B+            | ENC <i>n</i> _B-   | Input     | Encoder phase B inputs.                                                                                                                                                                                                                                                                                                                             |  |

| IDI <i>n</i> +     | IDI <i>n</i> -     | Input     | Isolated digital inputs. Accepts bipolar input signal.                                                                                                                                                                                                                                                                                              |  |

| IDO <i>n</i> +     | IDO <i>n</i> -     | Output    | Isolated digital outputs. Using N-MOS as current sinker.                                                                                                                                                                                                                                                                                            |  |

| ISO5VDD    | ISOGND | Output | Isolated 5V output from internal regulator. Insignificant driving capacity, used for resistor pull-ups only.                                                 |

|------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISOPWR     | ISOGND | Output | Isolated 5V output from internal regulator. Insignificant driving capacity, used for resistor pull-ups only. May be modified to have 12 V output capability. |

| EXT_ISOPWR | ISOGND | Input  | Use in conjunction with IDOn and external power supply, to provide current return path for fly-wheel diodes.                                                 |

| ISOGND     |        |        | Isolated digital ground.                                                                                                                                     |

| NC         |        |        | Shall be left unconnected.                                                                                                                                   |

- 1) Short Aln+ and Aln- to AGND for unused transducer input channels

- 2) Exceeding the maximum input voltage range may permanently degrade performance, or damage the input amplifier.

## 3.2 Analog Input Signal Connections

PCI-9524 provides eight differential analog input channels. To avoid ground loops and to achieve accurate low-level-signal measurements the PCI-9524 provides only differential input mode.

## 3.2.1 Signal Sources

#### **Ground-Referenced Signal Sources**

A ground-referenced signal is connected in some way to the buildings power system. That is, the signal source is already connected to a common ground point with respect to PCI-9524, assuming that the computer is plugged into the same power system. Non-isolated outputs of instruments and devices that plug into the buildings power system are ground-referenced signal sources.

#### Floating Signal Sources

A floating signal source is not connected in any way to the buildings ground system. A device with an isolated output is a floating signal source, such as optical isolator outputs, batteries, transformer outputs, load-cells and thermocouples.

## 3.2.2 Input Configurations

## Differential input mode for transducer input channels

Al channels 0 to 3 are dedicated to connecting to load-cell transducers in differential mode.

A load-cell is comprised of four resistive strain-gauges connected in Wheatstone bridge form, and is inherently a floating differential output device. Since a load-cell transducer is a passive device, it requires voltage excitation in order to transform the resistive change into electrical signals. A typical four-wire connection is shown on Figure 3-4.

+Vex VEXn+ VEX SENn+ -Vex VEX SENn-0 0 Aln+ ΔIn-0 NC 0 +Vo NC -Vo Load-cell Transducer PCI-9524

Figure 3-4: Connecting to a four-terminal load-cell transducer using a four-wire connection

It is recommended to enable the remote-sense function, and loop-back the VEXn+/- to VEX\_SENn+/- on the terminal board you're using when connecting to the transducer. A lengthy extension cable between PCI-9524 and the terminal board inevitably has some lead resistance that results in voltage drop; looping-back the excitation on the terminal board creates a six-wire connection and compensates for voltage drop.

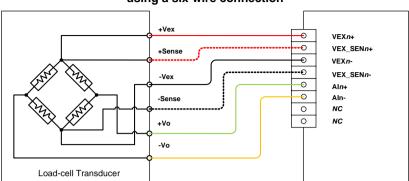

A better approach is to use specially designed load-cell transducers having two additional SENSE terminals. The voltage difference across the bridge excitation junctions is fed back to the voltage excitation circuitry by two separate 'sense-wires', to further correct the voltage drops due to the resistance in the excitation wiring. Be sure to enable the remote-sense function to take full advantage of a six-wire connection. A typical six-wire connection is shown in Figure 3-5.

Figure 3-5: Connecting to a six-terminal load-cell transducer using a six-wire connection

Whether to use a six-wire connection is dependent on the impedance of the load-cell transducers you are using, length of the wiring cable, wire-gauge inside the cable, and the required measurement accuracy. We recommend you to use a six-wire connection as the default connection method for high-accuracy load-cell transducers

To add remote-sense capability to a four-terminal load-cell transducer, simply run two separate sense-wires, and join them together with the excitation wires at the transducer's excitation terminals.

+Vex VEXn+ • • VEX SENn+ VFYn-• -Vex € VEX SENn-0 Aln+ Aln-0 NC +Vo 0 NC -Vo Load-cell Transducer PCI-9524

Figure 3-6: Connecting to a four-terminal load-cell transducer using a six-wire connection

#### Differential input mode for general purpose input channels

Al channels 4 to 7 are designed for connecting to ground-referenced or floating sources in differential mode.

The differential input mode provides two inputs that respond to signal voltage difference between them. If the signal source is ground-referenced, the differential mode can be used for the common-mode noise rejection. Figure 3-7 presents an example of ground-referenced signal source connections under differential input mode.

Input Multipexer n = 4, ..., 7Instrumentation Amplifier AIn+ Ground Referenced To A/D Signal Converter Source AIn-Commonmode noise & Ground potential

Figure 3-7: Ground-referenced source and differential input

Figure 3-8 shows how to connect a floating signal source to PCI-9524 in differential input mode. For floating signal sources, you need to add a resistor at each channel to provide a bias return path. The resistor value should be about 100 times the equivalent source impedance. If the source impedance is less than  $100\Omega$ , you can simply connect the negative side of the signal to AIGND as well as the negative input of the Instrumentation Amplifier without any resistors. In differential input mode, less noise couples into the signal connections than in single-ended mode.

Ground Referenced Signal Source Instrumentation Amplifier To A/D Converter

Figure 3-8: Floating source and differential input

## 3.3 Isolated Digital Signal Connection

PCI-9524 provides three opto-isolated encoder input channels, three opto-isolated pulse-command outputs, eight channel opto-isolated digital inputs as well as eight channel isolated digital outputs. Also, a built-in isolated power supply can be used as a resistors pull-up source.

## 3.3.1 Signal Sources and Terminal Devices

#### Open-collector and open-drain outputs

Open-collector or open-drain output stages are commonly used in industrial I/O. Open-collector/open-drain output stages made of NPN or N-MOS type transistors are for sink-type drivers, while those made of PNP or P-MOS type are for source-type drivers. A sink-driver sinks current from the external pull-up resistor when it is activated, and floats when it is inactivated; conversely, a source-driver sources current to the external pull-down resistor when it is activated, and floats when it is inactivated. High-side voltage can usually go as high as the output transistor can tolerate, and hence offers a wider, more versatile output voltage selection. The drawback is that when the output stage is inactivated, either the signal fall-time of a source-driver or the rise-time of a sink-driver, is determined by the RC time-constant formed by the pull-up/pull-down resistor and the stray capacitance. The asymmetrical rise/fall-time somehow limits the frequency response of the output stage.

## **Push-pull outputs**

Push-pull output stages are comprised of a complementary transistor pair, say, a PNP plus a PNP, or a P-MOS plus an N-MOS. Unlike open-collector output stages, they can sink or source current and hence a symmetrical rise/fall-time that is independent of the external load resistance. Push-pull output stages can generally toggle at a much faster speed than open-collector output stages.

#### **Line-driver outputs**

A Line-driver output stage is of differential output type, providing a normal output and a complementary output for each signal port. A Line-driver usually works at a much lower supply voltage and can toggle quickly. By utilizing differential transmission topology, the transmission distance can be extended considerably and with relatively low EMI.

The line-driver used on PCI-9524 is of voltage-driving type AM26LS31, compliant with ANSI TIA/EIA-422-B requirements. Either one of the two complementary outputs can be regarded as a single-ended push-pull output, and can be connected to an opto-isolated input or a TTL input.

#### **Opto-coupler Inputs**

Opto-coupler inputs are of current input type devices, made of a light-emitting-diode (LED) and an integrated light-sensitive transistor. They accept wide input voltage ranges, provided that the input current is limited by a series external resistor in order to protect the integrated LED device.

## Line-receiver inputs

The line-receiver, as its name implies, is used to accept signals from line-drivers. It's of differential input type, providing a normal input and a complementary input for each signal port.

- 1) The isolated ground (ISOGND) is shared between all isolated functions in PCI-9524. Make sure the ISOGND is connected to a known ground potential, only at one point in the system.

- 2) Do not let the ISOGND float, nor connect it directly to a chassis, as it may cause EMI and/or accumulate a charge that lead to safety hazards.

- 3) Shield the exposed ISOGND pins, connectors, and wiring, if possible to run a ground potential that is greater then 30-VDC.

- 4) Do not connect the ISOGND to analog ground (AGND), the noise on ISOGND will ruin analog performance.

## 3.3.2 Connecting to/from External Encoders

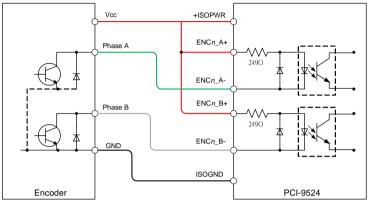

Figure 3-9: Connecting to an external encoder with NPN sink drivers

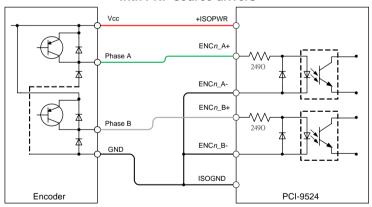

Figure 3-10: Connecting to an external encoder with PNP source drivers

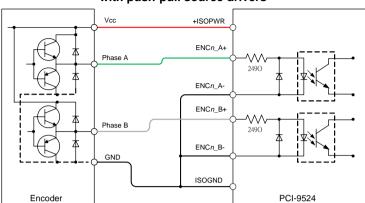

Figure 3-11: Connecting to an external encoder with push-pull source drivers

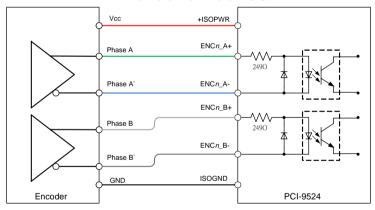

Figure 3-12: Connecting to an external encoder with differential line-drivers

## 3.3.3 Connecting to External Servo Amplifiers

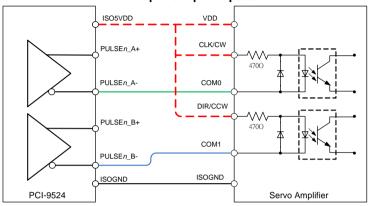

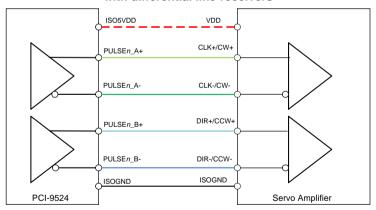

Figure 3-13: Connecting to an external servo-amplifier with opto-coupler inputs

Figure 3-14: Connecting to an external servo-amplifier with differential line-receivers

## 3.3.4 Interfacing Isolated DO with External Loads

### Connecting to external resistive loads

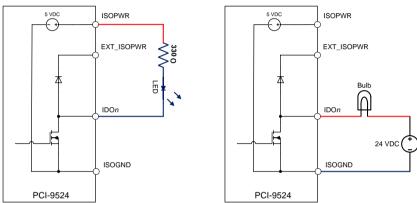

Figure 3-15 presents connecting to external resistive loads. The left side illustrates driving an external LED using the internal ISOPWR source; the right side illustrates driving an external 5W, 24-VDC Bulb using an external power supply.

Figure 3-15: Connecting to an external resistive load from the isolated DO sink driver

## Connecting to external inductive loads

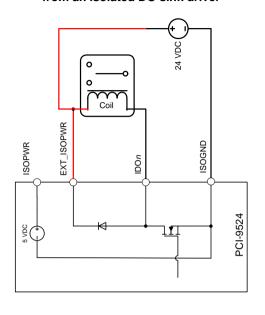

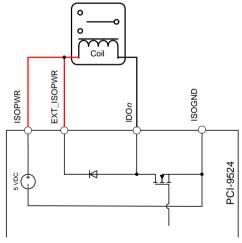

Figure 3-16 presents connecting to external resistive loads. The left side illustrates driving a 5-VDC relay coil using the internal ISOPWR source; the right side illustrates driving an external 12-VDC relay coil using an external power supply.

Figure 3-16: Connecting to an external inductive load from an isolated DO sink driver

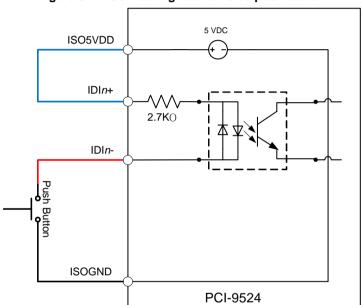

# 3.3.5 Interfacing Isolated DI with External Devices

## Connecting to a low-side push button

Alternatively, the push button can be connected at the high-side, i.e. between the ISOVDD and IDn+ pins. Also, the IDIn+ and IDIn-can be interchanged, since the opto-coupler accepts bipolar input signals.

Figure 3-17: Connecting to a low-side push button

## Connecting to an external sink driver

The sink driver can also be replaced by a mechanical switch, a proximity-sensor, etc. An external power-supply can be used instead of the internal isolated power source.

ISOSVDD

IDIn

Open Collector /

Open Drain

GND

ISOGND

PCI-9524

Figure 3-18: Connecting to an external sink driver

# 4 Operation Theory

The operation theory of the functions of PCI-9524 are described in this chapter. The functions include A/D conversion, D/A conversion, pulse-commands, encoder inputs, and isolated digital I/O. Operation theory helps users understand how to configure and program PCI-9524.

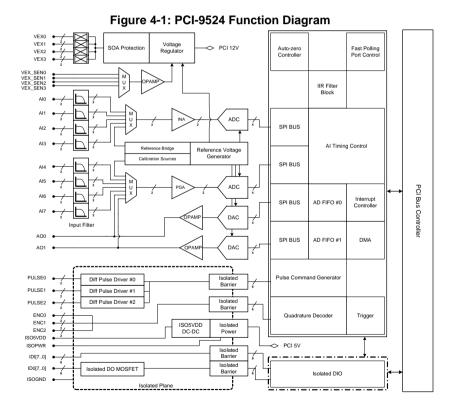

## 4.1 PCI-9524 Function Diagram

**Operation Theory**

## 4.2 Analog Input Channels

The following sub-sections depict the internal operations of signal amplification, conversion, post-processing, and calibration.

## 4.2.1 Signal Acquisition and Processing Flow

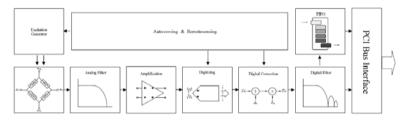

PCI-9524 was designed to detect weak signals through proper signal conditioning, amplification and digital post filtering, as depicted.

Figure 4-2: Signal acquisition and data processing flow for transducer input channels

At the first stage, the voltage excitation applied to the load-cell transducer transforms the resistive change into an electric signal, in the range of tens of milli-volts. Before entering amplification stage, the signal passes through a passive filter stage to filter out unwanted interference. A custom-made, low temperature coefficient instrumentation amplifier provides a fixed gain of 25, and the necessary level-shift (1). The amplified signal is fed into a sigmadelta modulator running at 1.92 MHz, pushing the in-band quantization noise to a higher frequency, and filtering most of which out using a 5-order SINC filter. The filtered digital data passes through an averager to tune down the data rate to a specific sampling rate. A built-in correction algorithm automatically calibrates the output data, which can then be pushed into the on-board FIFO for data transfer to PC memory, or sent to the next DSP stage described below.

There are four programmable post-processing IIR digital filter banks (2), one for each load-cell transducer input channel. Each bank is a fixed-coefficient, variable-length IIR digital filter, and can be instructed to flush itself once a large input-step is observed. The processed data are pushed into the on-board FIFO for DMA data transfer to PC memory; otherwise, they are read by user applications directly, without buffering, through fast-polling data transfers.

The software driver utilizes a look-up-table to correct the null offset and gain error of the analog front-end, using a built-in  $1.25 \mathrm{k}\Omega$  bridge, to provide adequate absolute accuracy for applications that do not calibrate load-cell transducers in the field. For applications that always perform null and gain calibrations in the field, users can manipulate the 2's complementary binary code directly.

Throughout the acquisition and processing flow, remote-sensing (3) and auto-zeroing (4) are working simultaneously to compensate voltage drops over excitation wires, and to remove thermal drift and 1/f noise in signal paths. The dynamic error compensation is essential to achieve high-stability measurements; otherwise the output will drift at a very low frequency that is difficult to be reconstructed using any other post-filtering method.

1) For general purpose analog input channels, i.e. channels 4 to 7, the available gain ranges are 1, 2, 4, and 8.

2), 3), 4) The general purpose analog input channels, i.e. channel 4 to 7, do not support the remote-sensing and auto-zeroing functions.

## 4.2.2 How to Define a 1 in 200,000 Count Resolution

It is common in the weight-scaling or material-testing industries to specify the resolution capability of a measurement device such as PCI-9524, in Counts or Digits, rather than in bits.

For example, a measurement device that is capable of resolving 1 in 1000 counts, can successfully register a 1-gram change on a 1-kg capacity load-cell transducer. Consequently, a measurement device that is capable of resolving 1 in 200,000 counts, can successfully register a 1-gram change on a 200-kg capacity load-cell transducer.

In practical applications, the sensitivity of load-cell transducers vary from model to model (typically form 1 to 4mV/V), and the full-scale output range of a transducer is usually only a fraction of the full-scale input range of a measurement device. The convenience of using Counts rather than Bits, is that the specified Count achievable by a measurement device, is relative to the transducers full-scale output, rather than the full-scale input range of the analog input amplifier. Thus, theoretically, no matter what the sensitivity of the 200-kg capacity load-cell transducer you are using, a 200,000 count measurement device can always resolve a 1-gram measurement.

Please also note, as a weight/force indicator, the displayed Counts or Digits shall be flicker-free while the applied force is in steady state. Therefore, a measurement device specified to have a 200,000 count resolution, must guarantee peak-to-peak system noise and short-term drift to below 1 / 200,000, or 5-ppm of the full-scale output range of the transducer.

The specified 200,000 count resolution capacity of PCI-9524 is verified by a precision load-cell simulator utilizing 3mV/V sensitivity, under 10-V excitation and using a six-wire remote-sense connection. The auto-zero function is enabled throughout acquisition, while the ADC sampling rate is set to 60 samples-per-second (the equivalent data rate is 29 samples-per-second, see Section 4.2.3 for details), and using an IIR post digital filter of 32-taps (see Section 4.2.9 for details). Under these conditions, the peak-to-peak system noise and drift are well below 150-nano-Volts, the limit of 1 in 200,000 count resolution. The recording duration is 30

minutes, and the ambient temperature fluctuation is within  $\pm$  1°C throughout.

## 4.2.3 Data Rate versus Sampling Rate

Due to the internal delay time and manipulations required for autozeroing and remote-sensing functions, the 'Sampling Rate' that the ADC is actually running at can be different from the actual 'Data Rate'.

In the following sections, the term 'Sampling Rate' and 'Data Rate' are of different meaning. The 'Sampling Rate' stands for the ADC's internal conversion speed set by users, whereas the 'Data Rate' stands for the output rate of the processed data.

See Table 4-1 for equivalent data rates versus ADC actual sampling rates, under different operating modes. When programming through a software API, users must set the desired ADC sampling rate, and the actual 'Data Rate' will be looked-up and returned by the software API for your reference.

## 4.2.4 Auto-scan, Multiplexing and Settling Time

PCI-9524 uses multiplexing for transducer input channels, and up to four transducers can be attached. When the Auto-scan feature is enabled, the hardware multiplexes and scans the four transducers in sequence; AlO, Al1, Al2, Al3, and AlO...etc.

Multiplexing increases the number of transducers that a single amplifier can deal with, it does however require additional time for the signal to rise/fall and propagate through the circuit stages. The time delay therefore required is called 'Settling Time'. Besides the propagation delay within PCI-9524, the parasitic in the cabling, the impedance of the transducers, and the amplitude difference between channels, affect final settling time figures.

PCI-9524 is programmed to have 400-µs default settling time, and this works best with low impedance transducers, such as 120 or 350-ohm load-cells. Insufficient settling time may causes interchannel crosstalk; the new signal will not be able to fully settle to its final value, and some 'residual' signals in the previous measurement will be present in the current measurement. Users may increase the hardware settling time, to check if a lesser inter-channel crosstalk is perceived. See Table 4-1 for the equivalent Data Rates versus ADC actual Sampling Rates, under different operating modes.

| ADC Sampling Rates, in Samples-per-second (SFS) |                 |           |             |           |

|-------------------------------------------------|-----------------|-----------|-------------|-----------|

| ADC                                             | Non-multiplexed |           | Multiplexed |           |

| Sampling                                        | Auto-zero       | Auto-zero | Auto-zero   | Auto-zero |

| Rate                                            | Disabled        | Enabled   | Disabled    | Enabled   |

| 30,000                                          | 30,000          | 818.73    | 1637.47     | 818.73    |

| 15,000                                          | 15,000          | 768.40    | 1536.81     | 768.40    |

| 7,500                                           | 7,500           | 703.53    | 1407.06     | 703.53    |

| 3,750                                           | 3,750           | 594.74    | 1189.48     | 594.74    |

| 2,000                                           | 2,000           | 462.66    | 925.33      | 462.66    |

| 1,000                                           | 1,000           | 316.32    | 632.63      | 316.32    |

| 500                                             | 500             | 193.75    | 387.49      | 193.75    |

| 100                                             | 100             | 47.26**   | 94.51       | 47.26**   |

| 60*                                             | 60              | 29.00     | 58.00       | 29.00     |

| 50**                                            | 50              | 24.29     | 48.59       | 24.29     |

| 30*                                             | 30              | 14.74     | 29.49       | 14.74     |

| 25**                                            | 25              | 12.32     | 24.64       | 12.32     |

| 15*                                             | 15              | 7.44      | 14.87       | 7.44      |

| 10***                                           | 10              | 4.97      | 9.94        | 4.97      |

| 5***                                            | 5               | 2.49      | 4.99        | 2.49      |

| 2.5***                                          | 2.5             | 1.25      | 2.5         | 1.25      |

Table 4-1: Data Rates vs. Multiplexing, Auto-zero & ADC Sampling Rates, in Samples-per-second (SPS)

- 1) For the equivalent data rate per channel, divide the multiplexed data rate figures by four.

- 2) \*60 Hz Rejection, \*\*50 Hz Rejection, \*\*\*Simultaneous 50 and 60 Hz Rejection.

- 3) Auto-zero function is always disabled for general purpose input channels, i.e. channels 4 to 7.

## 4.2.5 Power Line Noise Rejection

The SINC filter built into the PCI-9524 works best for suppressing power line noise, if the ADC sampling rate is set to match power line frequency. The harmonics of the power line noise can also be suppressed as well, see Table 4-3 for illustration. For applications demanding high-stability, low-drifting measurements, selecting a sampling rate that provides inherent power line noise rejection is recommended.

Figure 4-3: SINC Filter Power Line Noise Rejection at 60 Hz Multiples

The power line frequency is either 50 or 60-HZ in most countries. For sampling rates supporting power line noise rejection, please refer to the notes after Table 4-1 for your reference.

The SINC filter cannot suppress power line noise for a sampling rate above 60 SPS (or 100 SPS with auto-zero). Under such conditions, power line noise rejection relies on the inherent common-mode rejection ability of the input amplifier. Under this circumstance, using the post-processing IIR digital filter can attenuate power line noise somewhat, at the cost of increased signal settling time. See Section 4.2.9 for details.

## 4.2.6 Excitation and Remote-sensing

Users can select excitation voltages from either 2.5V or 10V sources. For most load-cell transducers, 10V is recommended. The higher the excitation, the higher the resolution will generally be; since the signal is larger at the beginning of the signal chain and hence a better overall 'signal-to-noise ratio' (SNR).

The remote-sensing function requires users to connect all the excitation voltage driving pins to the corresponding remote-sens-

ing pins. For channels that are not connected to a transducer, feedback the excitation voltage to the corresponding remote-sensing pins directly on the terminal board. Please refer to section 3.2 for details.

PCI-9524 applies simulated AC excitation to the load-cell transducers and must respond quickly toward the excitation voltage change, otherwise amplitude attenuation will occur. In general, calibrating your system and working at a fixed sampling rate not exceeding 100-SPS is preferred for most high accuracy applications. Also, using a lower impedance transducer, shortening the connecting cable, and increasing the wiring gauge will help to improve the response time.

Load-cell transducers with inductive properties are not recommended to be used with PCI-9524.

#### 4.2.7 Thermal EMF, 1/f Noise and Auto-zero

Thermal electromotive force (Thermal EMF) is the most common error in a low-level signal measurement system. A junction made of dissimilar metals develops some voltage difference across it. Working like a tiny thermal-couple, this phenomenon is also known as the Seebeck effect. Common lead-tin solder junctions can have 1 to  $3\mu V/^{\circ}C$  temperature coefficients, and even tight connected cooper-cooper junctions without oxidation will have as much as  $0.3\mu V/^{\circ}C$  temperature coefficients. For high-resolution load-cell applications calling for a voltage resolution higher than 100 nano-Volts, obviously, a 1°C fluctuation in temperature will bury the signal of interest.

Table 4-2: Temperature Coefficient of different metal junctions

| Junction Type          | Temperature Coefficient ( μV/ºC ) |

|------------------------|-----------------------------------|