# DM-TFT50-415

# 5.0" IPS 480× 854 TFT LCD DISPLAY Panel with Capacitive Touch - RGB

## Contents

- 1 Revision History

- 2 Main Features

- 3 Pin Description

- 3.1 Panel Pin Description

- 3.2 CTP Pin Description

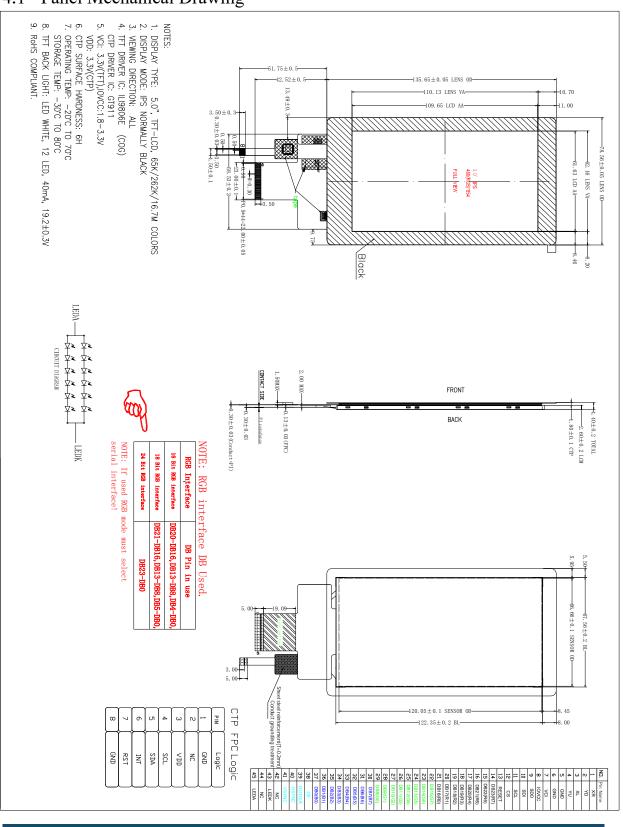

- 4 Mechanical Drawing

- 4.1 Panel Mechanical Drawing

- 5 Function Block Diagram

- 6 Optics & Electrical Characteristics

- 6.1 Optical Characteristics

- 6.2 Absolute Maximum Ratings (Ta=25 VSS=0V)

- 6.3 DC Characteristics

- 6.4 LED Backlight Characteristics

- 6.5 AC Characteristics

- 6.5.1 Serial Interface Characteristics (3-line serial):

- 6.5.2 Parallel 24/18/16-bit RGB Interface Timing Characteristics

- 6.5.3 DPI Interface Timing

- 6.5.4 Display RESET Timing Characteristics

#### 7 CTP Specification

- 7.1 Electrical Characteristics

- 7.1.1 Absolute Maximum Rating

- 7.1.2 DC Electrical Characteristics(Ta=25 °C)

- 7.1.3 AC Characteristics

- 7.2 I2C Timing

- 8 Reliability

- 9 Warranty and Conditions

## 1 Revision History

| Date      | Changes       |

|-----------|---------------|

| 2020-4-16 | First release |

## 2 Main Features

| Item                  | Specification               | Unit    |

|-----------------------|-----------------------------|---------|

| Diagonal Size         | 5.0                         | inch    |

| Driver element        | TFT active matrix           | -       |

| TFT Pixel arrangement | RGB vertical stripe         | -       |

| Display mode          | Transmissive/Normally Black | -       |

| Viewing angle         | ALL                         | o'clock |

| Display Colors        | 65K/262K/16.7M              | Colors  |

| Resolution            | 480 x 854                   | pixel   |

| Controller IC         | ILI9806E                    | -       |

| CTP Driver IC         | GT911                       | -       |

| Interface             | 3-SPI+16/18/24-bits RGB     | -       |

| Active Area           | 61.63 x 109.65              | mm      |

| Panel Dimension       | 78.56 x 135.65 x 4.40       | mm      |

| Pixel Pitch           | 0.128 x 0.128               | mm      |

| Touch mode            | 5-point and Gestures        | -       |

| Weight                | TBD                         | g       |

## 3 Pin Description

## 3.1 Panel Pin Description

| Pin No.SymbolFunction Description1XR(NC)Touch panel Right Glass Terminal2YD(NC)Touch panel Bottom Film Terminal3XL(NC)Touch panel LIFT Glass Terminal4YU(NC)Touch panel Top Film Terminal5GNDGround.6GNDGround.7VCISupply voltage (3.3V).8IOVCCI/O power supply voltage.9SDOSPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.10SDIData lane in 1 data lane serial interface.<br>The data is latched on the rising edge of the SCL signal.11SCLWhen D/CX = '1', data is selected.<br>When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.12CSChip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.13RESETReset pin. Setting either pin low initializes the LSI.<br>Must be reset after power is supplied.  |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2YD(NC)Touch panel Bottom Film Terminal3XL(NC)Touch panel LIFT Glass Terminal4YU(NC)Touch panel Top Film Terminal5GNDGround.6GNDGround.7VCISupply voltage (3.3V).8IOVCCI/O power supply voltage.9SDOSPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.10SDIData lane in 1 data lane serial interface.<br>The data is latched on the rising edge of the SCL signal.11SCLWhen D/CX = '1', data is selected.<br>When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.<br>fix this pin at VCI or GND when not in use.12CSChip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.13PESETReset pin. Setting either pin low initializes the LSI.                                                                     |     |

| 3   XL(NC)   Touch panel LIFT Glass Terminal     4   YU(NC)   Touch panel Top Film Terminal     5   GND   Ground.     6   GND   Ground.     7   VCI   Supply voltage (3.3V).     8   IOVCC   I/O power supply voltage.     9   SDO   SPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface.     10   SDI   The data is latched on the rising edge of the SCL signal.     11   SCL   When D/CX = '1', data is selected.     11   SCL   When D/CX = '0', command is selected.     12   CS   Chip select input pin ("Low" enable).     12   Reset pin. Setting either pin low initializes the LSI.                                                                                                                                                                      |     |

| 4   YU(NC)   Touch panel Top Film Terminal     5   GND   Ground.     6   GND   Ground.     7   VCI   Supply voltage (3.3V).     8   IOVCC   I/O power supply voltage.     9   SDO   SPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface. The data is latched on the rising edge of the SCL signal.     11   SCL   This pin is used to select "Data or Command" in the parallel interface. When D/CX = '1', data is selected.     11   SCL   When D/CX = '0', command is selected.     12   CS   Chip select input pin ("Low" enable). fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable). fix this pin at VCI or GND when not in use.                                                                                  |     |

| 5   GND   Ground.     6   GND   Ground.     7   VCI   Supply voltage (3.3V).     8   IOVCC   I/O power supply voltage.     9   SDO   SPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface.<br>The data is latched on the rising edge of the SCL signal.     11   SCL   This pin is used to select "Data or Command" in the parallel interface.<br>When D/CX = '1', data is selected.     11   SCL   When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.<br>fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.     13   PESET   Reset pin. Setting either pin low initializes the LSI. |     |

| 6   GND   Ground.     7   VCI   Supply voltage (3.3V).     8   IOVCC   I/O power supply voltage.     9   SDO   SPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface.<br>The data is latched on the rising edge of the SCL signal.     11   SCL   This pin is used to select "Data or Command" in the parallel interface.<br>When D/CX = '1', data is selected.     11   SCL   When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.<br>fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.     13   PESET   Reset pin. Setting either pin low initializes the LSI.                       |     |

| 7   VCI   Supply voltage (3.3V).     8   IOVCC   I/O power supply voltage.     9   SDO   SPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface. The data is latched on the rising edge of the SCL signal.     11   SCL   This pin is used to select "Data or Command" in the parallel interface. When D/CX = '1', data is selected.     11   SCL   When D/CX = '0', command is selected.     12   CS   Chip select input pin ("Low" enable). fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable). fix this pin at VCI or GND when not in use.                                                                                                                                                                             |     |

| 8   IOVCC   I/O power supply voltage.     9   SDO   SPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface.<br>The data is latched on the rising edge of the SCL signal.     11   SCL   This pin is used to select "Data or Command" in the parallel interface.<br>When D/CX = '1', data is selected.<br>When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.<br>fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.     13   PESET   Reset pin. Setting either pin low initializes the LSI.                                                                                              |     |

| 9   SDO   SPI interface output pinThe data is output on the falling edge of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface.<br>The data is latched on the rising edge of the SCL signal.     11   SCL   This pin is used to select "Data or Command" in the parallel interface.<br>When D/CX = '1', data is selected.<br>When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.<br>fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.     13   PESET   Reset pin. Setting either pin low initializes the LSI.                                                                                                                                        |     |

| 9   SDO   of the SCL signalIf not used, let this pin open.     10   SDI   Data lane in 1 data lane serial interface.<br>The data is latched on the rising edge of the SCL signal.     11   SCL   This pin is used to select "Data or Command" in the parallel interface.<br>When D/CX = '1', data is selected.<br>When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.<br>fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.     13   PESET   Reset pin. Setting either pin low initializes the LSI.                                                                                                                                                                                                       |     |

| 10   SDI   The data is latched on the rising edge of the SCL signal.     11   This pin is used to select "Data or Command" in the parallel interface.     11   SCL   This pin is used to select "Data or Command" in the parallel interface.     11   SCL   When D/CX = '1', data is selected.     11   SCL   When D/CX = '0', command is selected.     This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.   fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable).     13   PESET   Reset pin. Setting either pin low initializes the LSI.                                                                                                                                                                                                                                                          |     |

| 11   SCL   This pin is used to select "Data or Command" in the parallel interface.<br>When D/CX = '1', data is selected.<br>When D/CX = '0', command is selected.<br>This pin is used serial interface clock in 3-wire 9-bit / 4- wire 8-bit serial da interface.<br>fix this pin at VCI or GND when not in use.     12   CS   Chip select input pin ("Low" enable).<br>fix this pin at VCI or GND when not in use.     13   PESET   Reset pin. Setting either pin low initializes the LSI.                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 12 CS fix this pin at VCI or GND when not in use.   13 PESET Reset pin. Setting either pin low initializes the LSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | a   |

| 13 Reset pin. Setting either pin low initializes the LSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| intust of reset after porter is supplied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 14-37 DB23-DB0 24-bit parallel bi-directional data bus for MCU system and RGB interfamode .Fix to GND level when not in use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ice |

| 38     DE     Data enable signal for RGB interface peration.<br>fix this pin at VCI or GND when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 39DOTCLKDot clock signal for RGB interface operation.<br>Fix this pin at VCI or GND when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 40 HSYNC Line synchronizing signal for RGB interface operation.<br>fix this pin at VCI or GND when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Frame synchronizing signal for RGB interface operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 41 VSYNC fix this pin at VCI or GND when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 42 NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 43 LEDK Cathode pin of backlight.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 44 NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 45 LEDA Anode pin of backlight.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

## 3.2 CTP Pin Description

| Pin No. | Symbol | Function Description            |  |

|---------|--------|---------------------------------|--|

| 1       | GND    | Ground.                         |  |

| 2       | NC     |                                 |  |

| 3       | VDD    | Supply voltage.                 |  |

| 4       | SCL    | I2C clock input.                |  |

| 5       | SDA    | I2C data input and output       |  |

| 6       | INT    | External interrupt to the host. |  |

| 7       | RST    | External Reset, Low is active.  |  |

| 8       | GND    | Ground.                         |  |

## 4 Mechanical Drawing

### 4.1 Panel Mechanical Drawing

Copyright © 2020

www.displaymodule.com

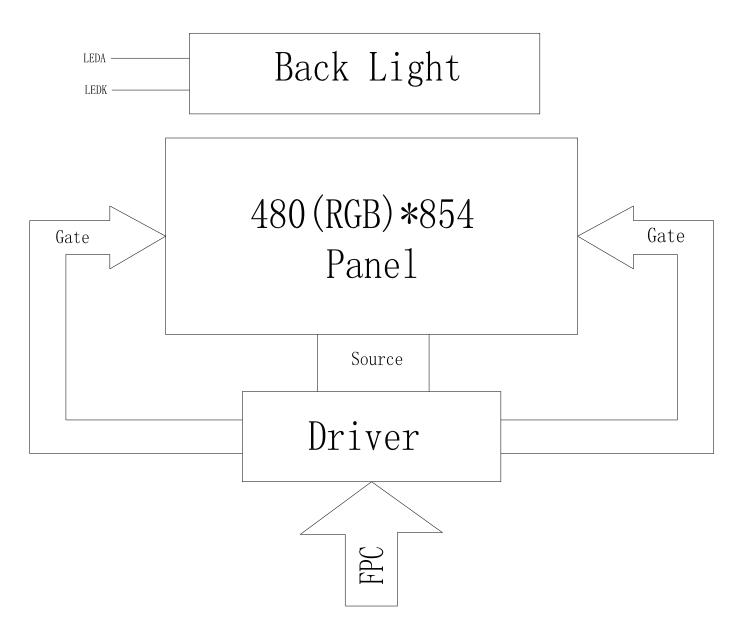

## 5 Function Block Diagram

## 6 Optics & Electrical Characteristics

### 6.1 Optical Characteristics

| Item             |         | Symbol         | Min  | Тур            | Max | Unit | Remark        |

|------------------|---------|----------------|------|----------------|-----|------|---------------|

| View Angles      |         |                | -    | 80             | -   | 0    | CR>10         |

| C.I.E. (White)   |         | (x)<br>(y)     | -    | 0.305<br>0.340 | -   | -    |               |

| C.I.E(Red)       |         | (x)<br>(y)     | -    | -              | -   | -    | Θ=0<br>Normal |

| C.I.E(Green)     |         | (x)<br>(y)     | -    | -              | -   | -    | viewing angle |

| C.I.E(Blue)      |         | (x)<br>(y)     | -    | -              | -   | -    |               |

| Contrast Ratio   |         | CR             | 640  | 800            | -   | -    | -             |

| Desmanae time    | Rising  | T <sub>R</sub> | -    | 16             | 21  | Msec | -             |

| Response time    | Falling | T <sub>F</sub> | -    | 19             | 24  | Msec | -             |

| Color gamut      |         | S(%)           | -    | 70             | -   | %    | C-light       |

| Option View Dire |         |                | Free |                |     | -    |               |

| Nota             |         |                |      |                |     |      |               |

Note:

- Measuring surrounding: dark room

- Ambient temperature:  $25\pm2$ °C

- 15min. warm-up time.

### 6.2 Absolute Maximum Ratings (Ta=25 VSS=0V)

| Parameter                        | Symbol           | Min  | Max | Unit | Remark |

|----------------------------------|------------------|------|-----|------|--------|

| Digital Supply Voltage           | V <sub>DD</sub>  | -0.3 | 4.6 | V    | -      |

| Digital interface supple Voltage | Iovcc            | -0.3 | 4.6 | V    | -      |

| Operating Temperature            | T <sub>OP</sub>  | -20  | 70  | °C   | -      |

| Storage Temperature              | T <sub>STG</sub> | -30  | 80  | °C   | -      |

Note : If the absolute maximum rating of even is one of the above parameters is exceeded even momentarily, the quality of the product may be degraded. Absolute maximum ratings, therefore, specify the values exceeding which the product may be physically damaged. Be sure to use the product within the range of the absolute maximum ratings.SSS

### 6.3 DC Characteristics

| Item                             | Symbol | Condition | Min                     | Тур. | Max                     | Unit |

|----------------------------------|--------|-----------|-------------------------|------|-------------------------|------|

| Digital Supply Voltage           | VDD    | 2.5       | 2.8/3.3                 | .6   | V                       | V    |

| Digital interface supple Voltage | IOVCC  | 1.65      | 1.8                     | 3.6  | V                       | V    |

| Normal mode Current consumption  | IDD    | -         | 30                      | -    | mA                      | V    |

| Low Level Input Voltage          | VIL    | -         | -0.3                    | -    | 0.3 * V <sub>DDIO</sub> | V    |

| High Level Input Voltage         | VIH    | -         | 0.7 * V <sub>DDIO</sub> | -    | V <sub>DDIO</sub>       | V    |

| Low Level Output Voltage         | VOL    | -         | GND                     | -    | 0.2 * V <sub>DDIO</sub> | V    |

| High Level Output Voltage        | VOH    | -         | 0.8 * V <sub>DDIO</sub> | -    | V <sub>DDIO</sub>       | V    |

Note : The VCC input must be kept in a stable value; ripple and noise are not allowed.

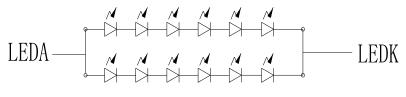

### 6.4 LED Backlight Characteristics

The back-light system is edge-lighting type with 12 chips White LED

| Parameter       | Symbol | Min   | Тур  | Max | Unit              | Remark  |

|-----------------|--------|-------|------|-----|-------------------|---------|

| Forward voltage | VF     | -     | 19.2 | -   | V                 | -       |

| Forward current | IF     | 30    | 40   | -   | mA                | -       |

| LCM Luminance   | Lv     | 430   | -    | -   | cd/m <sup>2</sup> | Note3   |

| LED life time   | Hr     | 50000 |      |     | Hour              | Note1,2 |

| Uniformity      | AVg    | 80    |      |     | %                 | Note3   |

Note 1: LED life time (Hr) can be defined as the time in which it continues to operate under the condition: Ta=25±3 °C, typical IL value indicated in the above table until the brightness becomes less than 50%.

Note 2:The "LED life time" is defined as the module brightness decrease to 50% original brightness at Ta=25°C and IL=40mA. The LED lifetime could be decreased if operating IL is larger than 40mA. The constant current driving method is suggested.

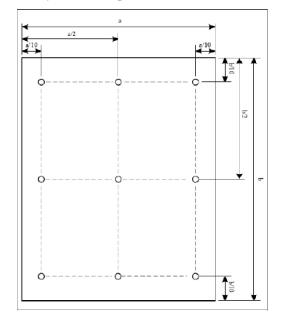

CIRCUIT DIAGRAM

NOTE 3: Luminance Uniformity of these 9 points is defined as below:

Uniformity =  $\frac{\text{minimum luminance in 9 points}(1-9)}{\text{maximum luminance in 9 points}(1-9)}$

Lumiance =  $\frac{\text{Total lumincace of 9 points}}{9}$

Copyright © 2020

### 6.5 AC Characteristics

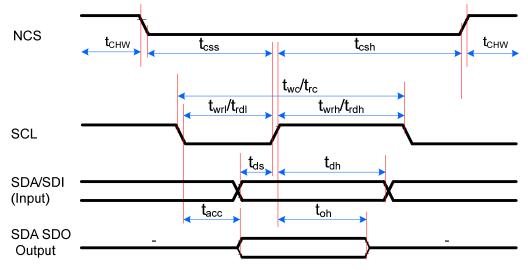

### 6.5.1 Serial Interface Characteristics (3-line serial):

#### *IOVCC*=1.8*V*,*VCI*=2.8*V*,*Ta*=25°*C*

| Signal   | Symbol           | Description                  | Min | Max | Unit | Remark              |

|----------|------------------|------------------------------|-----|-----|------|---------------------|

|          | T <sub>CSS</sub> | Chip select time (Write)     | 15  | -   | ns   |                     |

| CSX      | T <sub>CSH</sub> | Chip select hold time (Read) | 15  | -   | ns   |                     |

|          | T <sub>CHW</sub> | CS "H" pulse width           | 40  | -   | ns   |                     |

|          | T <sub>WC</sub>  | Serial clock cycle (Write)   | 30  | -   | ns   |                     |

|          | T <sub>WRH</sub> | SCL "H" pulse width (Write)  | 10  | -   | ns   |                     |

| SCL      | T <sub>WRL</sub> | SCL "L" pulse width (Write)  | 10  | -   | ns   |                     |

| SCL      | T <sub>RC</sub>  | Serial clock cycle (Read)    | 150 | -   | ns   |                     |

|          | T <sub>RDH</sub> | SCL "H" pulse width (Read)   | 60  | -   | ns   |                     |

|          | T <sub>RDL</sub> | SCL "L" pulse width (Read)   | 60  | -   | ns   |                     |

| SDA/SDO  | T <sub>ACC</sub> | Access time (Read)           | 10  | 100 | ns   | For maximum CL=30pF |

| (Output) | Тон              | Output disable time (Read)   | 15  | 100 | ns   | For minimum CL=8pF  |

| SDA      | T <sub>DS</sub>  | Data setup time (Write)      | 10  | _   | ns   |                     |

| (DIN)    | T <sub>DH</sub>  | Data hold time (Write)       | 10  | -   | ns   |                     |

Note:

1. Ta = -30 to 70 °C, IOVCC=1.65V to 3.6V, VCI=2.5V to 3.6V, T=10+/-0.5ns.

2. Does not include signal rise and fall times.

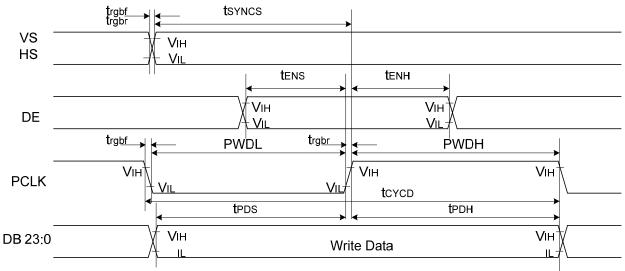

## 6.5.2 Parallel 24/18/16-bit RGB Interface Timing Characteristics

Ta = -30 to 70°C, IOVCC=1.65V to 3.6V, VCI=2.5V to 3.6V, DGND=0V

| Signal   | Symbol                               | Description               | Min | Max | Unit | Remark               |

|----------|--------------------------------------|---------------------------|-----|-----|------|----------------------|

| VS/HS    | T <sub>SYNCS</sub>                   | VS/HS setup time          | 5   | -   | ns   |                      |

| v 5/H5   | T <sub>SYNCH</sub>                   | VS/HS hold time           | 5   | -   | ns   |                      |

| DE       | T <sub>ENS</sub>                     | DE setup time             | 5   | -   | ns   |                      |

| DE       | T <sub>ENH</sub>                     | DE hold time              | 5   | -   | ns   |                      |

| DB[23:0] | T <sub>POS</sub>                     | Data setup time           | 5   | -   | ns   | 24/18/16-bit bus RGB |

| DB[23.0] | T <sub>PDH</sub>                     | Data hold time            | 5   | -   | ns   | interface mode       |

|          | P <sub>WDH</sub>                     | PCLK high-level period    | 13  | -   | ns   |                      |

| PCLK     | P <sub>WDL</sub>                     | PCLK low-level period     | 13  | -   | ns   |                      |

| FULK     | T <sub>CYCD</sub>                    | PCLK cycle time           | 28  | -   | ns   |                      |

|          | t <sub>rgbr</sub> ,t <sub>rgbf</sub> | PCLK,HS,VS rise/fall time | -   | 15  | ns   |                      |

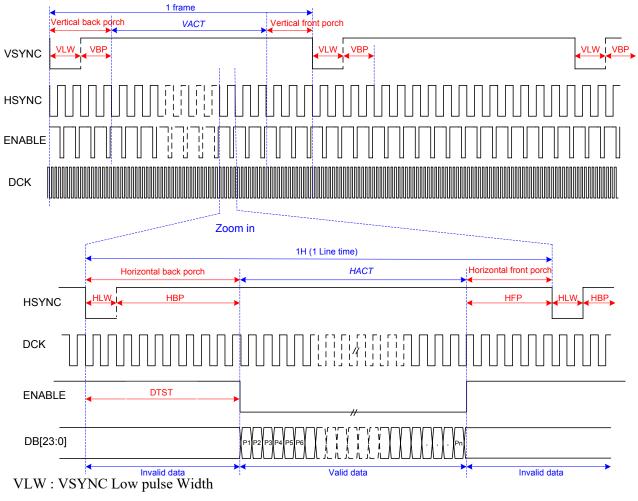

### 6.5.3 DPI Interface Timing

HLW : HSYNC Low pulse Width

DTST : Data Transfer Startup Time

Pn : pixel 1, pixel 2..., pixel n.

#### The timing chart of 24-/18-/16-bit DPI (RGB) interface mode

| Symbol | Description                | Min  | Тур. | Max  | Unit   |

|--------|----------------------------|------|------|------|--------|

| FR     | Frame Rate                 | 54   |      | 66   | fps    |

| HLW    | Horizontal Low Pulse width | 1    |      | -    | DOTCLK |

| HBP    | Horizontal Back Porch      | 2    |      | 126  | DOTCLK |

| HACT   | Horizontal Address         |      | 480  |      | DOTCLK |

| HFP    | Horizontal Front Porch     | 2    |      | -    | DOTCLK |

| VLW    | Vertical Low Pulse width   | 1    |      | 126  | Line   |

| VBP    | Vertical Back Porch        | 1    |      | 126  | Line   |

| VACT   | Vertical Address           |      |      | 864  | Line   |

| VFP    | Vertical Front Porch       | 1    |      | 255  | Line   |

| DCLK   | Data Clock                 | 16.6 |      | 41.7 | MHz    |

Note 1: HLW+HBP+HFP  $\geq$  2us.

Note 2: VSPL='0', HSPL='0', DPL='0' and EPL='0' of "(Interface Mode Control 21h of the Page 1)" command.

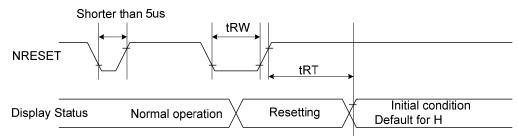

## 6.5.4 Display RESET Timing Characteristics

#### **Timing Parameters**

| Siganl | Symbol              | Parameter            | Min | Max                | Unit |

|--------|---------------------|----------------------|-----|--------------------|------|

|        | TRW                 | Reset pulse duration | 10  | -                  | μs   |

| RESX   | X TDT Deset several | Deast served         | -   | 5 (Note 1, 5)      | ms   |

|        | TRT Reset cancel    |                      |     | 120 (Note 1, 6, 7) | ms   |

Note 1:The reset cancel includes also required time for loading ID bytes, VCOM setting and other settings from OTP to registers. This loading is done every time when there is H/W reset cancel time (tRT) within 5 ms after a rising edge of RESX.

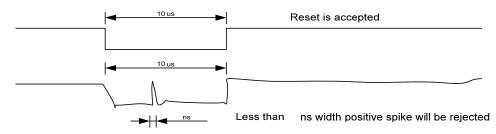

Note 2: 2.Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the Table 43.

| RESX Pulse          | Action         |

|---------------------|----------------|

| Shorter than 5µs    | Reset Rejected |

| Longer than 9µs     | Reset          |

| Between 5µs and 9µs | Reset starts   |

Note 3: 3.During the Resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out mode. The display remains the blank state in Sleep In mode.) and then return to Default condition for Hardware Reset.

Note 4: Spike Rejection also applies during a valid reset pulse as shown below:

Note 5: When Reset applied during Sleep In Mode.

Note 6: When Reset applied during Sleep Out Mode.

Note 7: It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

## 7 CTP Specification

### 7.1 Electrical Characteristics

#### 7.1.1 Absolute Maximum Rating

| Item                              | Symbol          | Min  | Max  | Unit | Note |

|-----------------------------------|-----------------|------|------|------|------|

| Digital Supply Voltage            | VDD             | 2.66 | 3.47 | V    |      |

| Operating Temperature             | Top             | -30  | +85  | °C   |      |

| Storage Temperature               | T <sub>ST</sub> | -30  | +85  | °C   |      |

| ESD protection voltage (HB Model) | -               | -    | ±2   | KV   |      |

#### 7.1.2 DC Electrical Characteristics(Ta=25 °C)

(Ambient temperature:25°C, VDD=2.8V, VDDIO=1.8V or VDDIO=VDD)

| Item                            | Min      | Туре | Max      | Unit | Note |

|---------------------------------|----------|------|----------|------|------|

| Normal mode operating current   | -        | 8    | 14.5     | mA   |      |

| Green mode operating current    | -        | 3.3  | -        | mA   |      |

| Sleep mode operating current    | 70       | -    | 120      | uA   |      |

| Doze mode operating current     | -        | 0.78 | -        | mA   |      |

| Digital Input low voltage/VIL   | -0.3     | -    | 0.25*VDD | V    |      |

| Digital Input high voltage/VIH  | 0.75*VDD | -    | VDD+0.3  | V    |      |

| Digital Output low voltage/VOL  | -        | -    | 0.15*VDD | V    |      |

| Digital Output high voltage/VOH | 0.85*VDD | -    | -        | V    |      |

#### 7.1.3 AC Characteristics

(Ambient temperature:25°C, VDD=2.8V, VDDIO=1.8V)

| Parameter                          | Min | Тур | Max | Unit | Note |

|------------------------------------|-----|-----|-----|------|------|

| OSC oscillation frequency          | 59  | 60  | 61  | MHz  |      |

| I/O output rise time, low to high  | -   | 14  | -   | ns   |      |

| I/O output rfall time, high to low | -   | 14  | -   | ns   |      |

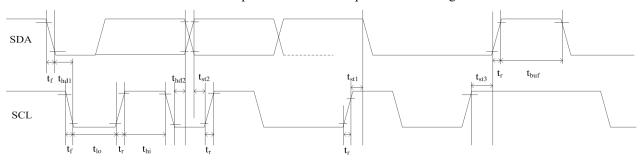

## 7.2 I2C Timing

GT911 provides a standard I2C interface for SCL and SDA to communicate with the host. GT911 always serves as slave device in the system with all communication being initialized by the host. It is strongly recommended that transmission rate be kept at or below 400Kbps. The I2C timing is shown below:

| Item                               | Symbol           | Min | Max | Unit |

|------------------------------------|------------------|-----|-----|------|

| SCL low period                     | t <sub>lo</sub>  | 1.3 | -   | μs   |

| SCL high period                    | t <sub>hi</sub>  | 0.6 | -   | μs   |

| SCL setup time for Start condition | t <sub>st1</sub> | 0.6 | -   | μs   |

| SCL setup time for Stop condition  | t <sub>st3</sub> | 0.6 | -   | μs   |

| SCL hold time for Start condition  | t <sub>hd1</sub> | 0.6 | -   | μs   |

| SDA setup time                     | t <sub>st2</sub> | 0.1 | -   | μs   |

| SDA hold time                      | t <sub>hd2</sub> | 0   | -   | μs   |

#### Test condition 1: 1.8V host interface voltage, 400Kbps transmission rate, 2K pull-up resistor

#### Test condition 2: 3.3V host interface voltage, 400Kbps transmission rate, 2K pull-up resistor

| Item                               | Symbol           | Min | Max | Unit |

|------------------------------------|------------------|-----|-----|------|

| SCL low period                     | t <sub>lo</sub>  | 1.3 | -   | μs   |

| SCL high period                    | t <sub>hi</sub>  | 0.6 | -   | μs   |

| SCL setup time for Start condition | t <sub>st1</sub> | 0.6 | -   | μs   |

| SCL setup time for Stop condition  | t <sub>st3</sub> | 0.6 | -   | μs   |

| SCL hold time for Start condition  | t <sub>hd1</sub> | 0.6 | -   | μs   |

| SDA setup time                     | t <sub>st2</sub> | 0.1 | -   | μs   |

| SDA hold time                      | t <sub>hd2</sub> | 0   | -   | μs   |

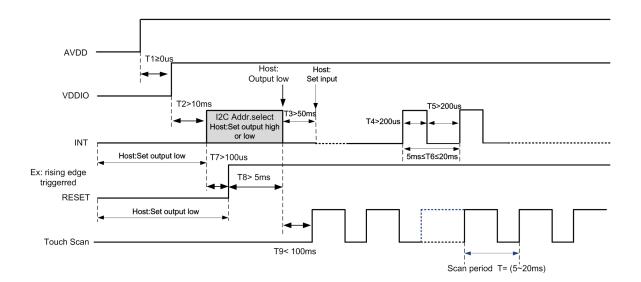

GT911 supports two I<sup>2</sup>C slave addresses: 0xBA/0xBB and 0x28/0x29. The host can select the address by changing the status of Reset and INT pins during the power-on initialization phase. See the diagram below for configuration methods and timings:

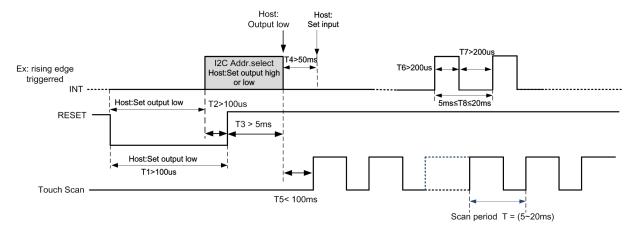

#### **Power-on Timing:**

#### Timing for host resetting GT911:

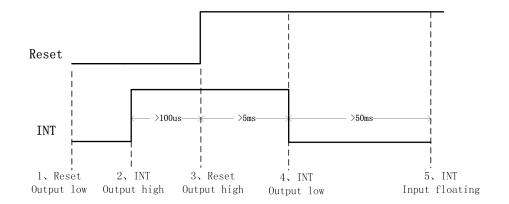

#### Timing for setting slave address to 0x28/0x29:

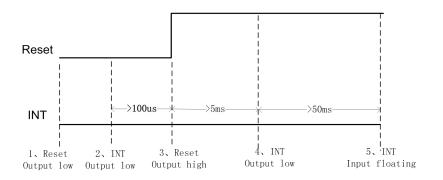

#### Timing for setting slave address to 0xBA/0xBB:

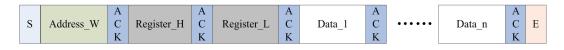

#### a) Data Transmission

(For example: device address is 0xBA/0xBB)

Communication is always initiated by the host. Valid Start condition is signaled by pulling SDA line from "high" to "low" when SCL line is "high". Data flow or address is transmitted after the Start condition.

All slave devices connected to I 2 C bus should detect the 8-bit address issued after Start condition and send the correct ACK. After receiving matching address, GT911 acknowledges by configuring SDA line as output port and pulling SDA line low during the ninth SCL cycle. When receiving unmatched address, namely, not 0XBA or 0XBB, GT911 will stay in an idle state.

For data bytes on SDA, each of 9 serial bits will be sent on nine SCL cycles. Each data byte consists of 8 valid data bits and one ACK or NACK bit sent by the recipient. The data transmission is valid when SCL line is "high".

When communication is completed, the host will issue the STOP condition. Stop condition implies the transition of SDA line from "low" to "high" when SCL line is "high".

#### b) Writing Data to GT911

(For example: device address is 0xBA/0xBB)

#### **Timing for Write Operation**

The diagram above displays the timing sequence of the host writing data onto GT911. First, the host issues a Start condition. Then, the host sends 0XBA (address bits and R/W bit; R/W bit as 0 indicates Write operation) to the slave device.

After receiving ACK, the host sends the 16-bit register address (where writing starts) and the 8-bit data bytes (to be written onto the register).

The location of the register address pointer will automatically add 1 after every Write Operation.

Therefore, when the host needs to perform Write Operations on a group of registers of continuous addresses, it is able to write continuously. The Write Operation is terminated when the host issues the Stop condition.

#### c) Reading Data from GT911

#### (For example: device address is 0xBA/0xBB)

| s | Address_W | A<br>C<br>K | Register_H  | A<br>C<br>K | Register_L | A<br>C<br>K | E | s | Address_R | A<br>C<br>K | Data_1 | A<br>C<br>K | •••••   | Data_n | N<br>A<br>C<br>K | Е |

|---|-----------|-------------|-------------|-------------|------------|-------------|---|---|-----------|-------------|--------|-------------|---------|--------|------------------|---|

|   |           | •           | Set address | poi         | nter       |             |   |   |           |             | ►Rea   | ıd da       | ata ┥ 👘 |        |                  |   |

#### **Timing for Read Operation**

The diagram above is the timing sequence of the host reading data from GT911. First, the host issues a Start condition and sends 0XBA (address bits and R/W bit; R/W bit as 0 indicates Write operation) to the slave device.

After receiving ACK, the host sends the 16-bit register address (where reading starts) to the slave device. Then the host sets register addresses which need to be read.

Also after receiving ACK, the host issues the Start condition once again and sends 0XBB (Read Operation). After receiving ACK, the host starts to read data.

GT911 also supports continuous Read Operation and, by default, reads data continuously. Whenever receiving a byte of data, the host sends an ACK signal indicating successful reception. After receiving the last byte of data, the host sends a NACK signal followed by a STOP condition which terminates communication.

## 8 Reliability

| Test Item                  | Content of Test                                | Test Condition | Note |

|----------------------------|------------------------------------------------|----------------|------|

| Low Temperature Storage    | Endurance test applying the high storage       | -30°C          | 1,2  |

| Low Temperature Storage    | temperature for a long time.                   | 96hrs          | 1,2  |

|                            | Endurance test applying the electric stress    | 70°C           |      |

| High Temperature Operation | (Voltage & Current) and the thermal stress to  | 96hrs          | -    |

|                            | the element for a long time.                   | 901118         |      |

| Low Temperature Operation  | Endurance test applying the electric stress    | -20 °C         | 1    |

| Low Temperature Operation  | under low temperature for a long time.         | 96hrs          | 1    |

|                            | The module should be allowed to stand at       |                |      |

| High Temperature/          | 60°C,90%RH max, for 96hrs under no-load        | 70°C,90%RH     | 1.2  |

| Humidity Operation         | condition excluding the polarizer. Then taking | 96hrs          | 1,2  |

|                            | it out and drying it at normal temperature.    |                |      |

| Thermal Sheelt Desistence  | The sample should be allowed stand the         | -20°C/70°C     |      |

| Thermal Shock Resistance   | following 10 cycles of operation               | 20 cycles      | -    |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal. Temperature and humidity after remove from the rest chamber.

## 9 Warranty and Conditions

<u>http://www.displaymodule.com/pages/faq</u> HYPERLINK "http://www.displaymodule.com/pages/faq"