**PROPRIETARY NOTE :** THIS SPECIFICATION IS THE PROPERTY OF BOE AND SHALL NOT BE REPRODUCED OR COPIED WITHOUT THE WRITTEN PERMISSION OF BOE AND MUST BE RETURNED TO BOE UPON ITS REQUEST

# **Approval Sheet**

Preliminary specification

#### □ Final specification

| Customer Name       | *** ***                             |

|---------------------|-------------------------------------|

| Product Description | 2.1inch 1600RGB*1600 TFT-LCD Module |

| Version             | Pre.0                               |

| Supplier            | BOE                                 |

| Module Code         | VS021XRM-NW0-6KP0                   |

ORDOS YUANSHENG OPTOELECTRONICS TECHNOLOGY CO.,LTD.

P1

# **Product Specification**

Product Name : 2.1" TFT-LCD Module

Model Name : VS021XRM-NW0-6KP0

Description : 2.1" 1600RGB×1600 16.7M Color

| HECKED BY | APPROVALED BY |

|-----------|---------------|

|           |               |

|           |               |

# ORDOS YUANSHENG OPTOELECTRONICS TECHNOLOGY CO.,LTD.

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 2 OF 34 |

B2006-5006-O (3/3)

ISSUE DATE

2020.03.03

# **Revision History**

|      |         | <b>,</b>               |            |          |

|------|---------|------------------------|------------|----------|

| REV. | ECN NO. | DESCRIPTION OF CHANGES | DATE       | PREPARED |

| P0   | -       | Initial Release        | 2019.10.11 | GONG LEI |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         |                        |            |          |

|      |         | $\sim$                 |            |          |

|      | Å       |                        |            |          |

|      |         |                        |            |          |

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 3 OF 34 |

B2006-5006-O (3/3)

P1

ISSUE DATE

2020

2020.03.03

| NO. |             | ITEMS                                   | PAGE   |

|-----|-------------|-----------------------------------------|--------|

| 1.0 | General E   | Description                             | 6      |

| 1.1 | Introductio | on                                      | 6      |

| 1.2 | Feature     |                                         | 7      |

| 1.3 | Applicatio  | n                                       | 7      |

| 1.4 | General s   | pecification                            | 8      |

| 2.0 | Absolute    | Maximum Ratings                         | 9      |

| 3.0 | Electrical  | Specifications                          | 10     |

| 3.1 | TFT-LCD     | Panel                                   | 10     |

| 3.2 | Back-light  | Unit                                    | 11     |

| 4.0 | Optical S   | pecifications                           | 12     |

| 4.1 | Overview    |                                         | 12     |

| 4.2 | Optical sp  | ecifications                            | 12     |

| 5.0 | Interface   | Connection                              | 16     |

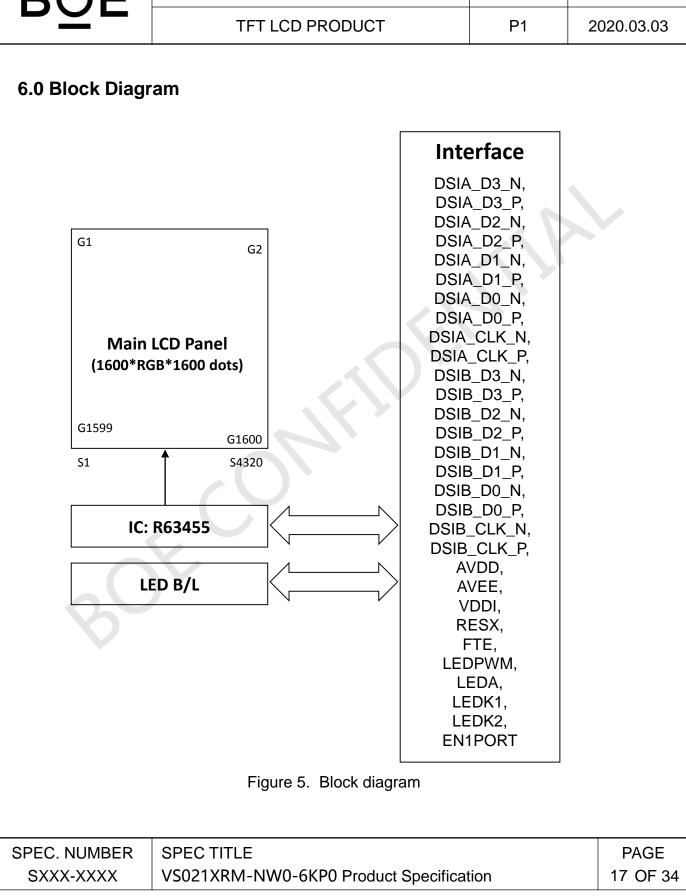

| 6.0 | Block Dia   | ıgram                                   | 17     |

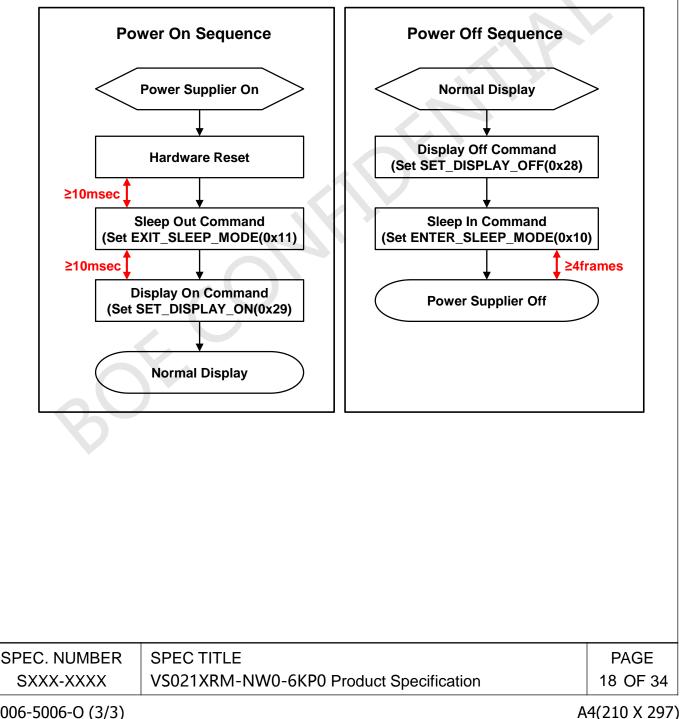

| 7.0 | Timing C    | haracteristics                          | 18     |

| 7.1 | Power on/   | off sequence                            | 18     |

| 7.2 | Reset Tim   | ing Sequence                            | 21     |

| 7.3 | Deep Star   | ndby Mode Timing                        | 22     |

| 7.4 | MIPI Inter  | face Characteristics                    | 23     |

| 7.5 | Operating   | Sequence                                | 27     |

| 7.6 | Initial Cod | e Setting                               | 28     |

|     | NUMBER      | SPEC TITLE                              | PAGE   |

| SXX | X-XXXX      | VS021XRM-NW0-6KP0 Product Specification | 4 OF 3 |

| В | <u>O</u> | Ε |

|---|----------|---|

|   |          |   |

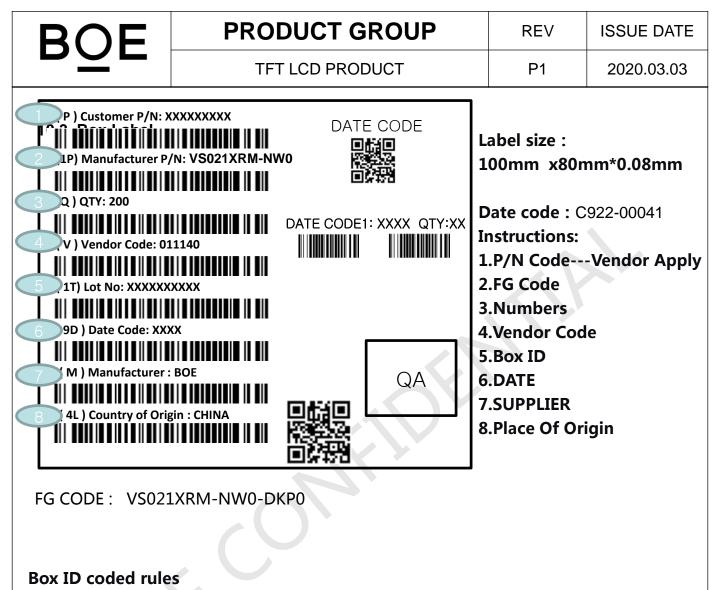

| PRODUCT GROUP   | REV | ISSUE DATE |

|-----------------|-----|------------|

| TFT LCD PRODUCT | P1  | 2020.03.03 |

| NO.  | ITEMS                      | PAGE |

|------|----------------------------|------|

| 8.0  | Mechanical Characteristics | 29   |

| 9.0  | Reliability Test           | 30   |

| 10.0 | Packing Information        | 31   |

| 10.1 | Packing Description        | 31   |

| 10.2 | Packing Procedure          | 32   |

| 10.3 | Box Label                  | 33   |

| 11.0 | Handing & Cautions         | 34   |

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 5 OF 34 |

B2006-5006-O (3/3)

2020.03.03

# **1.0 GENERAL DESCRIPTION**

## **1.1 Introduction**

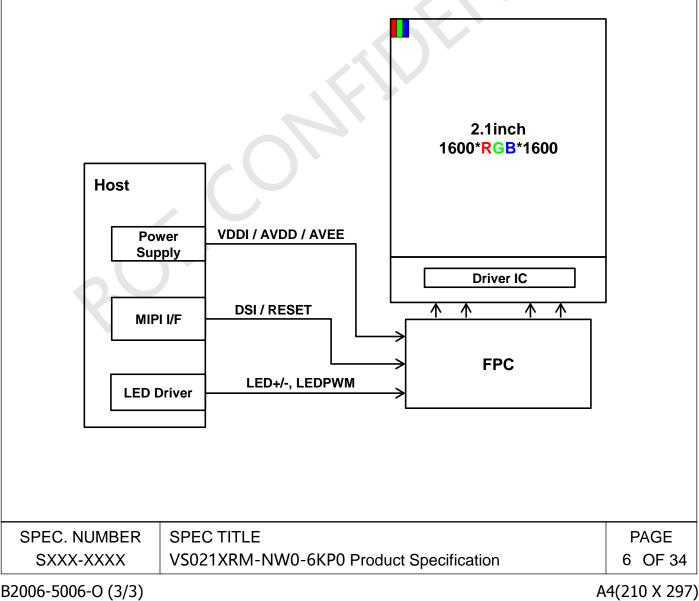

The 2.1inch TFT-LCD Module is a Color Active Matrix TFT LCD panel using LTPS (Low Temperature Poly-silicon) TFT's (Thin Film Transistors) as an active switching devices. This module has a 2.1 inch diagonally measured active area with 1600\*1600 resolutions (1600 horizontal by 1600 vertical pixel array). Each pixel is divided into RED, GREEN, BLUE dots which are arranged in vertical stripe and this module can display 16.7M colors. The TFT-LCD panel used for this module is adapted for a low reflection and higher color type.

| BOE | PRODUCT GROUP   | REV | ISSUE DATE |

|-----|-----------------|-----|------------|

|     | TFT LCD PRODUCT | P1  | 2020.03.03 |

#### 1.2 Features

- High PPI

- Fast response time

- High frame ratio

- High luminance, low reflection and wide viewing angle

- RoHS、Halogen Free Compliant

## **1.3 Application**

- Virtual Reality Device

- Augmented Reality Device

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 7 OF 34 |

P1

2020.03.03

## **1.4 General Specification**

< Table 1. General Specifications >

| Parameter             | Specification                        | Unit   | Remark     |

|-----------------------|--------------------------------------|--------|------------|

| Display method        | Active matrix TFT                    |        |            |

| Display mode          | Transmission mode, Normally<br>black |        |            |

| Screen size           | 2.1" (38.4mm)                        | inch   | diagonally |

| Number of pixels      | 1600(H) × 1600(V)                    | pixels | 1058 ppi   |

| Pixel pitch           | 8(H) × 24(V)                         | um     |            |

| Pixel arrangement     | RGB stripe                           |        |            |

| Display colors        | 16.7M                                | colors | 8bit       |

| NTSC Ratio            | 70.8%                                |        |            |

| LCM Outline Dimension | 41.2(H) × 45.3(V) × 1.66 (T)         | mm     | Note 1)    |

| LCM Weight            | 6.0 ±1.0                             | gram   | Note 1)    |

| Driver IC             | R63455                               |        |            |

| Interface             | MIPI DSI (Video Mode)                |        |            |

| Surface Treatment     | HC, ≥3H                              |        |            |

#### Note:

1) Protection film is not included.

| SPEC. NUMBER | SPEC TITLE                              | PAGE    |

|--------------|-----------------------------------------|---------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 8 OF 34 |

P1

# 2.0 ABSOLUTE MAXIMUM RATINGS

| < Table 2. Absolute Maximum Ratings> [ | Ta =25 ± 2 ℃] |

|----------------------------------------|---------------|

|----------------------------------------|---------------|

| Items                                   | Symbol               | Rating       | Unit | Remark                  |

|-----------------------------------------|----------------------|--------------|------|-------------------------|

| Logic voltage                           | VDDI                 | -0.3 to +1.8 | V    |                         |

| Positive Analog<br>Power Supply Voltage | AVDD                 | -0.3 to +6.0 | V    |                         |

| Negative Analog<br>Power Supply Voltage | AVEE                 | -6.0 to +0.3 | V    |                         |

| LED forward current                     | I <sub>LED</sub>     | 45           | mA   | each LED<br>20% on duty |

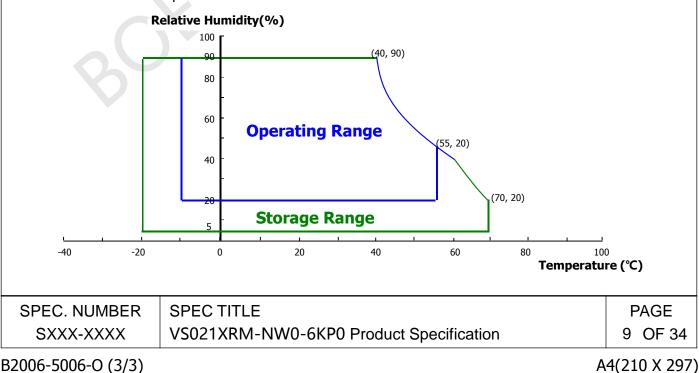

| Storage temperature                     | T <sub>STG</sub>     | -40 to +70   | °C   |                         |

| Operation temperature                   | T <sub>OPR</sub>     | -10 to +55   | °C   |                         |

| Humidity<br>(ambient temeprature=Ta)    | Ta≤60°C, 90% RH Max. |              |      |                         |

Note 1: If the module exceeds the absolute maximum ratings, it may be damaged permanently. Also, if the module operated with the absolute maximum ratings for a long time, its reliability may drop. It is not allowed for any of these ratings to be exceeded. Make sure all the design characte ristics are adequate before the panel is initialed.

Note 2: Temperature and relative humidity range are shown in the figure below. Wet bulb temperature should be 39 °C max. and no condensation of water.

< Table 3, I CD Panel Electrical Specifications >

P1

$[T_2 = 25 \pm 2 \circ 1]$

# 3.0 ELECTRICAL SPECIFICATIONS

## 3.1 TFT LCD Panel

| < Table 3. LCD Parlet Electrical Specifications > $[1a = 25 \pm 2 C]$ |                     |                   |          |       |          |      |        |

|-----------------------------------------------------------------------|---------------------|-------------------|----------|-------|----------|------|--------|

| Items                                                                 |                     | Symbol            | Min.     | Тур.  | Max.     | Unit | Remark |

| Logic vo                                                              | ltage               | VDDI              | 1.7      | 1.8   | 1.9      | V    |        |

| Positive A<br>Power Suppl                                             | •                   | AVDD              | 5.7      | 6.0   | 6.3      | V    | Note 1 |

| Negative<br>Power Supp                                                | 0                   | AVEE              | -6.3     | -6.0  | -5.7     | V    |        |

| Frame I                                                               | Ratio               | FPS               | -        | 70/90 |          | Hz   |        |

| Input signal H                                                        | High level          | V <sub>IH</sub>   | 0.7×VDDI |       | VDDI     | V    |        |

| voltage                                                               | Low level           | V <sub>IL</sub>   | VSSI     |       | 0.3×VDDI | V    |        |

| Output signal                                                         | High level          | V <sub>OH</sub>   | 0.8×VDDI | -     | VDDI     |      |        |

| voltage                                                               | Low level           | V <sub>OL</sub>   | VSSI     | -     | 0.2×VDDI |      |        |

|                                                                       |                     | I <sub>VDDI</sub> |          | 79.8  | 87.7     | mA   |        |

| Current con                                                           | Current consumption |                   | -        | 8.7   | 12       | mA   | Note 2 |

|                                                                       |                     | I <sub>AVEE</sub> | -        | -5.4  | -11      | mA   |        |

| Driver IC                                                             | FSD                 | НВМ               | - 2      | -     | +2       | kV   |        |

| Diverio                                                               | , LOD               | MM                | -200     | -     | +200     | V    |        |

#### Note 1:

The value can be adjusted by software to optimize display quality.

The operation is guaranteed under the recommended operating conditions only. The oper ation is not guaranteed if a quick voltage change occurs during operation. To prevent nois e, a bypass capacitor must be inserted into the line close to power pin. Please make sure all the design settings are used within this range before the panel is initialed.

Note 2:

Test pattern: All White Display

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 10 OF 34 |

2020.03.03

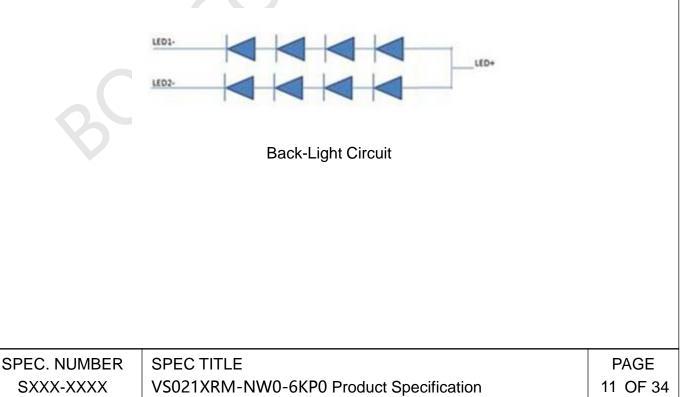

## 3.2 Back-light Unit

Ta=25+/-2°C

| Items             | Symbol          | Min. | Тур.             | Max. | Unit | Remark |  |

|-------------------|-----------------|------|------------------|------|------|--------|--|

| Forward Current   | lf              | -    | 45mA@2<br>0%duty | -    | mA   | Note1  |  |

| Forward Voltage   | Vf              | -    | 6.5              | -    | V    | Note1  |  |

| Power Consumption | P <sub>BL</sub> | -    | 468              | -    | mW   | Note2  |  |

| LED Q'ty          |                 |      | 8                |      | Ea   |        |  |

Note 1: The driving condition is defined for each LED chip.

Note 2: The B/L power consumption is defined for the backlight module. the schematic drawing of the backlight unit is as the figure. The B/L power consumption is based on 20% on duty mode

Ref. Total power consumption(max) depends on LED current/LED driver efficiency, etc.

B2006-5006-O (3/3)

# 4.0 OPTICAL SPECIFICATION

#### 4.1 Overview

The optical characteristics should be measured in a dark room (ambient luminance≤ 1 lux and temperature =  $25\pm2^{\circ}$ C) with the equipment of Konica Minolta CA-310 and CS-2000 and test unit shall be located at an approximate distance 50cm from the LCD surface at a viewing angle of  $\theta$  and  $\Phi$  equal to  $0^{\circ}$ . The center of the measuring spot on the display su rface should stay fixed.

The operation should be under the recommended operating conditions.

## **4.2 Optical Specifications**

| Item                     |             | Symbol          | Condition            | Min.      | Тур.        | Max.  | Unit              | Remark |

|--------------------------|-------------|-----------------|----------------------|-----------|-------------|-------|-------------------|--------|

|                          | Horizontal  | θ3              |                      | -         | 40          | -     |                   |        |

|                          | HUHZUHlai   | θ <sub>9</sub>  | CR > 100             | -         | 40          | -     | degree            | Note 1 |

| Viewing Angle            | Vertical    | θ <sub>12</sub> |                      | -         | 40          | -     |                   |        |

|                          | venical     | θ <sub>6</sub>  |                      | -         | 40          | -     |                   |        |

| Color Ga                 | amut (NTSC) |                 | $\theta = 0^{\circ}$ | -         | 70.8        | -     | %                 |        |

| Contrast Rat             | io          | CR              | $\theta = 0^{\circ}$ | 400       | 650         | -     |                   | Note 2 |

| Luminance of White       | Center      | Y <sub>w</sub>  | 0 00                 | 384       | 480         | -     | cd/m <sup>2</sup> | Note 3 |

| Luminance Uniformity     | 5 Points    | ΔΥ5             | $\theta = 0^{\circ}$ | 80%       | 85%         | -     |                   | Note 4 |

| 8                        |             | Rx              |                      | 0.615     | 0.640       | 0.665 |                   |        |

|                          | Red         | Ry              | $\theta = 0^{\circ}$ | 0.305     | 0.330       | 0.355 |                   | Note 5 |

|                          | Orean       | Gx              |                      | 0.309     | 0.334       | 0.359 |                   |        |

| Chromaticity             | Green       | Gy              |                      | 0.603     | 0.628       | 0.653 |                   |        |

| (CIE 1931)               | Dhua        | Bx              |                      | 0.125     | 0.150       | 0.175 |                   |        |

|                          | Blue        | Ву              |                      | 0.035     | 0.060       | 0.085 |                   |        |

|                          |             | Wx              |                      | 0.270     | 0.280       | 0.290 |                   |        |

|                          | White       | Wy              |                      | 0.280     | 0.290       | 0.300 |                   |        |

| Response Tir<br>(G to G) | ne          | Т               | $\theta = 0^{\circ}$ | -         | -           | 5.5   | ms                | Note 6 |

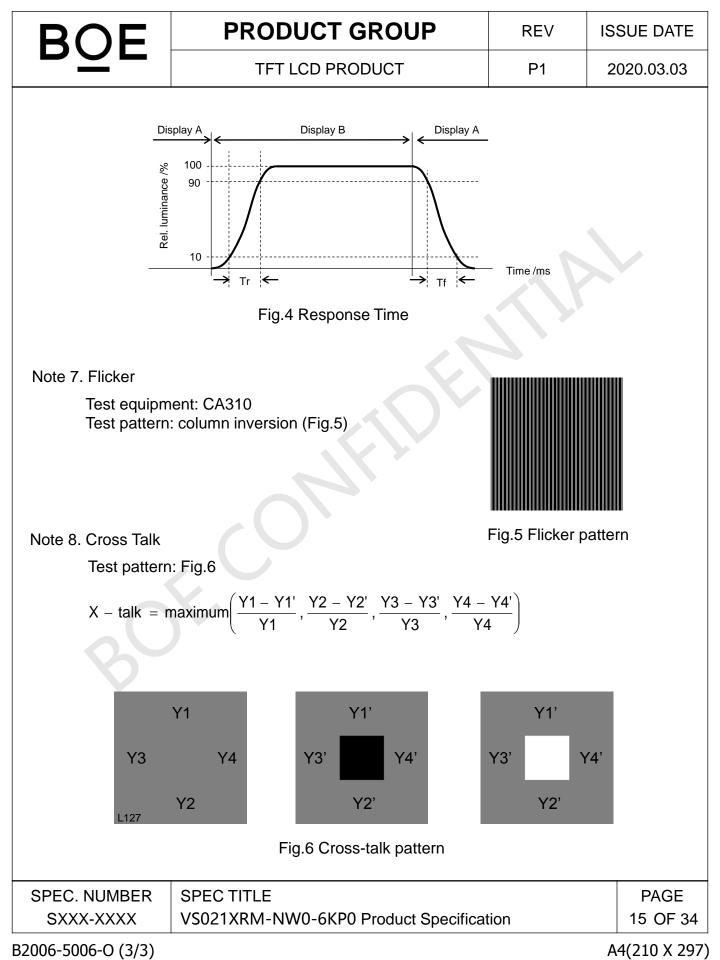

| Flicker                  |             |                 | $\theta = 0^{\circ}$ | -         | -           | -30   | db                | Note 7 |

| Cross Talk               |             | СТ              | $\theta = 0^{\circ}$ | -         | -           | 2.5   | %                 | Note 8 |

|                          |             |                 |                      |           |             |       |                   |        |

| SPEC. NUMBER             | R SPE       | C TITLE         |                      |           |             |       |                   | PAGE   |

| SXXX-XXXX                | VS0         | 21XRM-N         | W0-6KP0 P            | roduct Sp | pecificatio | on    |                   | 12 OF  |

### <Table 5. Optical Specifications>

B2006-5006-O (3/3)

| Β | Ο | Ε |

|---|---|---|

|   |   |   |

2020.03.03

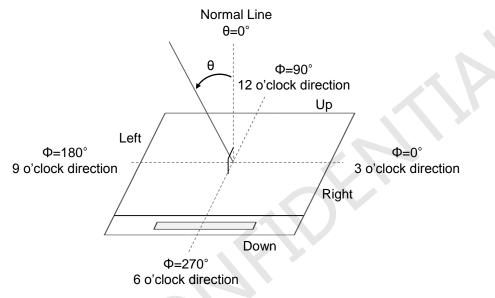

Note 1. Viewing angle is the angle at which the contrast ratio is greater than 10. The viewing angles are determined for the horizontal or 3, 9 o'clock direction and the vertical or 6, 12 o'clock direction with respect to the optical axis which is normal to the LCD surface (FIGURE 1).

Fig.1 Viewing angle measurement setup

Note 2. Contrast ratio measurements shall be made at viewing angle of  $\theta$ =0° and at the center of the LCD surface. Luminance shall be measured with all pixels in the view field set first to white, then to the dark (black) state (FIGURE 1). Contrast Ratio (CR) is defined mathematically.

CR = Luminance when displaying a white raster

Luminance when displaying a black raster

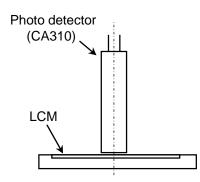

Note 3. Luminance of white is defined as luminance values of the center point across the LCD surface. Luminance shall be measured with all pixels in the view field set first to white. This measurement shall be taken at the locations shown in FIGURE 2 for a total of the measurements per display. The luminance is measured by CA310 when **the LED current is set at 9mA/ea and the backlight is under the 20% on duty mode.**

Note 4. The White luminance uniformity is then expressed as:

$\Delta Y$  = Minimum Luminance of 5 points / Maximum Luminance of 5 points (FIGURE 3).

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 13 OF 34 |

B2006-5006-O (3/3)

| 2020  | .03.03 |

|-------|--------|

| 2020. | .00.00 |

Fig.2 Luminance, uniformity & chromaticity measurement setup

Fig.3 Luminance uniformity measurement setup

- Note 5. The color chromaticity is measured with all pixels first in red, green, blue and white. Measurements should be made at the center of the panel.

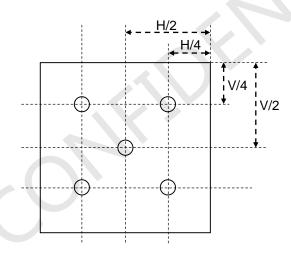

- Note 6. Definition of Response time.

The output signals of photo detector are measured when the input signals are switched between different display pattern (Gray-to-Gray). The response time is defined as the time interval **between the 10% and 90% of amplitudes** (Fig.4)

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 14 OF 34 |

B2006-5006-O (3/3)

## **5.0 INTERFACE CONNECTION**

The electronics interface connector is **Kyocera 145863050024829+** The connector interface pin assignments are listed in Table 6. <Table 6. Pin Assignments for the Interface Connector>

| Connector:145863050024829+ |            |                           |     |            |                     |  |  |  |  |

|----------------------------|------------|---------------------------|-----|------------|---------------------|--|--|--|--|

| NO.                        | Symbol     | Description               | NO. | Symbol     | Description         |  |  |  |  |

| 1                          | GND        | Ground                    | 2   | NC         | No Connection       |  |  |  |  |

| 3                          | PNSLV      | Main port select          | 4   | VSP        | Positive power      |  |  |  |  |

| 5                          | BLUPWM     | BLU duty control          | 6   | NC         | No Connection       |  |  |  |  |

| 7                          | TE         | TE signal output          | 8   | VSN        | Negative power      |  |  |  |  |

| 9                          | RESET      | DDIC reset signal         | 10  | GND        | Ground              |  |  |  |  |

| 11                         | GND        | Ground                    | 12  | DSIB_D3_P  | MIPI-DSI-Data lane  |  |  |  |  |

| 13                         | DSIB_D0_P  | MIPI-DSI-Data lane        | 14  | DSIB_D3_N  | MIPI-DSI-Data lane  |  |  |  |  |

| 15                         | DSIB_D0_N  | MIPI-DSI-Data lane        | 16  | GND        | Ground              |  |  |  |  |

| 17                         | GND        | Ground                    | 18  | DSIB_CLK_P | MIPI-DSI-Clock lane |  |  |  |  |

| 19                         | DSIB_D1_P  | MIPI-DSI-Data lane        | 20  | DSIB_CLK_N | MIPI-DSI-Clock lane |  |  |  |  |

| 21                         | DSIB_D1_N  | MIPI-DSI-Data lane 🥄      | 22  | GND        | Ground              |  |  |  |  |

| 23                         | GND        | Ground                    | 24  | DSIB_D2_P  | MIPI-DSI-Data lane  |  |  |  |  |

| 25                         | DSIA_D2_N  | MIPI-DSI-Data lane        | 26  | DSIB_D2_N  | MIPI-DSI-Data lane  |  |  |  |  |

| 27                         | DSIA_D2_P  | MIPI-DSI-Data lane        | 28  | GND        | Ground              |  |  |  |  |

| 29                         | GND        | Ground                    | 30  | DSIA_D1_N  | MIPI-DSI-Data lane  |  |  |  |  |

| 31                         | DSIA_CLK_N | MIPI-DSI-Clock lane       | 32  | DSIA_D1_P  | MIPI-DSI-Data lane  |  |  |  |  |

| 33                         | DSIA_CLK_P | MIPI-DSI-Clock lane       | 34  | GND        | Ground              |  |  |  |  |

| 35                         | GND        | Ground                    | 36  | DSIA_D0_N  | MIPI-DSI-Data lane  |  |  |  |  |

| 37                         | DSIA_D3_N  | MIPI-DSI-Data lane        | 38  | DSIA_D0_P  | MIPI-DSI-Data lane  |  |  |  |  |

| 39                         | DSIA_D3_P  | MIPI-DSI-Data lane        | 40  | GND        | Ground              |  |  |  |  |

| 41                         | GND        | Ground                    | 42  | NC         | No Connection       |  |  |  |  |

| 43                         | ID0        | ID Pin(low : 0)           | 44  | LED+       | LED Positive power  |  |  |  |  |

| 45                         | ID1        | ID Pin ( high : 1 )       | 46  | NC         | No Connection       |  |  |  |  |

| 47                         | IOVCC1     | Power for digital circuit | 48  | LED1-      | LED Negative power  |  |  |  |  |

| 49                         | IOVCC2     | Power for digital circuit | 50  | LED2-      | LED Negative power  |  |  |  |  |

Remark:

Pin 3 "PNSLV" is a Main Port select pin, which is should be connected to the 'L' level;

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 16 OF 34 |

BOE

B2006-5006-O (3/3)

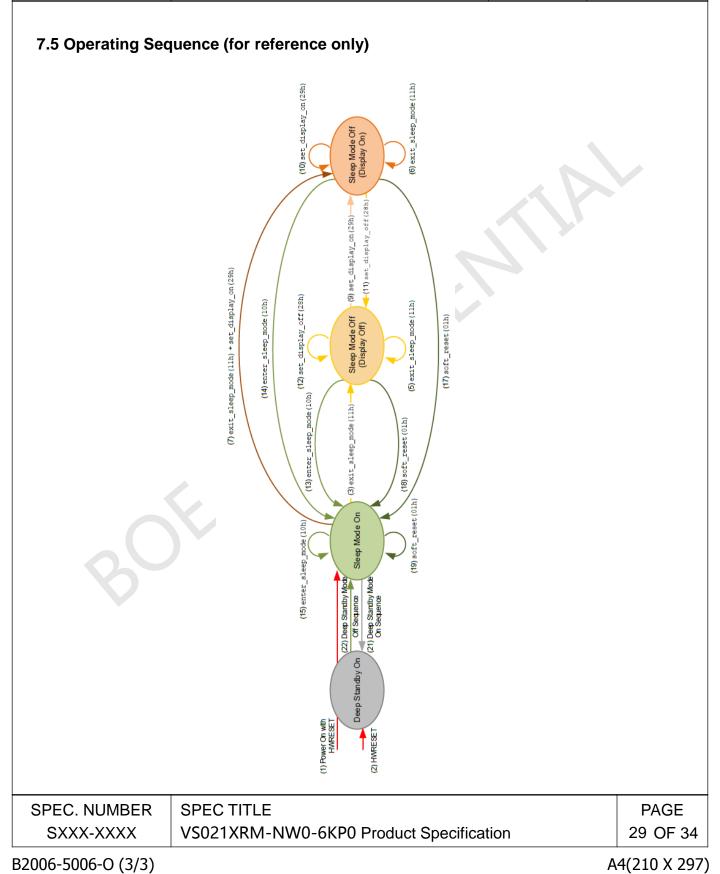

# 7.0 Timing Characteristics

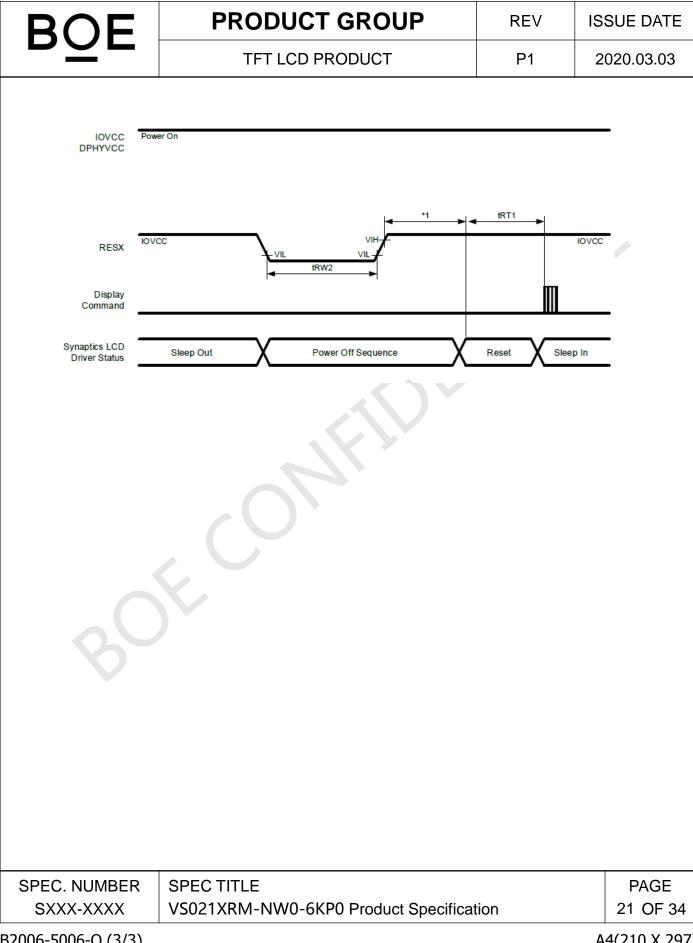

### 7.1 Power On/Off Sequence

The power supply ON/OFF setting for Display ON/OFF, Standby Set/Exit, and Sleep Set/Exit sequences is illustrated in figure below.

B2006-5006-O (3/3)

P1

2020.03.03

#### Power On/Off Sequence

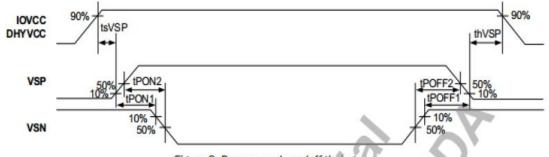

R63455 can be operated by supplying the VSP and VSN power supplies directly.

Figure 8. Power supply on/off timing

Table 23. Power supply timing specifications

| Item                             | Symbol | Unit | Test Condition | Minimum | Maximum |

|----------------------------------|--------|------|----------------|---------|---------|

| VSP-VSN delay time (10% to 10%)  | tPON1  | μs   | Power on       | 0       | -       |

| VSP-VSN delay time (50% to 50%)  | tPON2  | μs   | Power on       | 0       | -       |

| System power on to VSP ON time   | tsVSP  | ms   | Power on       | 1       | -       |

| VSN-VSP delay time (10% to 10%)  | tPOFF1 | μs   | Power off      | 0       | -       |

| VSN-VSP delay time (50% to 50%)  | tPOFF2 | μs   | Power off      | 0       | -       |

| VSP OFF to system power OFF time | thVSP  | μs   | Power off      | 0       | -       |

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 19 OF 34 |

B2006-5006-O (3/3)

P1

2020.03.03

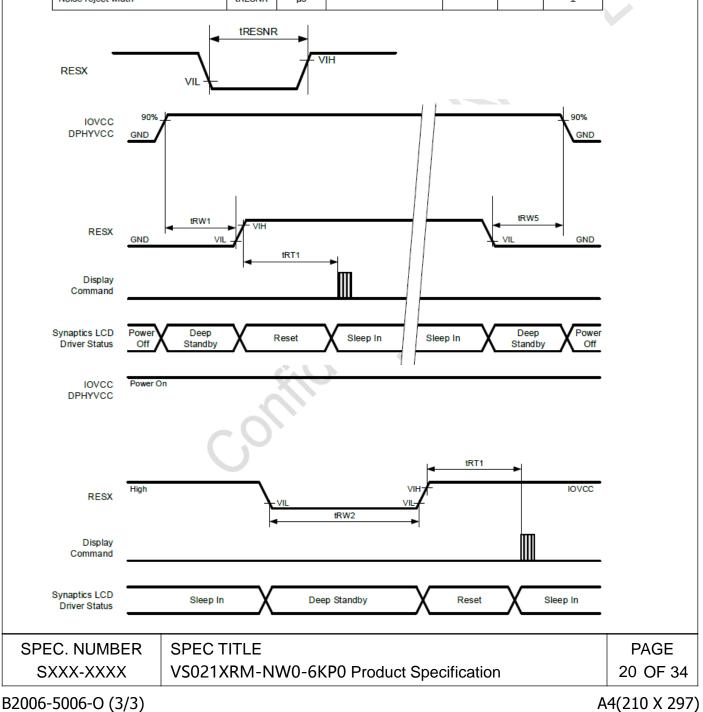

## 7.2 Reset Input Timing

| Item                   | Symbol | Unit | Test Condition   | Minimum | Typical | Maximum |

|------------------------|--------|------|------------------|---------|---------|---------|

| Reset low-level width1 | tRW1   | μs   | Power supply on  | 3000    | -       | -       |

| Reset low-level width2 | tRW2   | μs   | Operation        | 1000    | -       | -       |

| Reset low-level width3 | tRW5   | ms   | Power supply off | 25      | -       |         |

| Reset to MIPI command  | tRT1   | ms   | Sleep in         | 20      | -       | -       |

| Noise reject width     | tRESNR | μs   | -                | -       | -       | 1       |

B2006-5006-O (3/3)

P1

# 7.3 Deep Standby Mode Timing

B2006-5006-O (3/3)

|            | <b>6</b>                                        | Otamina d                                               | State                           | 9                               |  |

|------------|-------------------------------------------------|---------------------------------------------------------|---------------------------------|---------------------------------|--|

|            | Sequence                                        | Command                                                 | From                            | То                              |  |

| 1          | Power on sequence<br>with HWRESET               | $(\text{RESET_N} = \text{Low} \rightarrow \text{High})$ | Power off                       | Sleep mode on                   |  |

| 2-a        | HWRESET                                         | (RESET_N = Low)                                         | _                               | Deep standby on                 |  |

| <b>2-b</b> | HWRESET sequence                                | (RESET_N = High -> Low $\rightarrow$ High)              | All status                      | Sleep mode on                   |  |

| 3          |                                                 |                                                         | Sleep mode on                   | Sleep mode off                  |  |

| 5          | exit_sleep_mode<br>sequence                     | exit_sleep_mode(11h)                                    | Sleep mode off<br>(display off) | (Display off)                   |  |

| 6          |                                                 |                                                         | Sleep mode off<br>(display on)  | Sleep mode off<br>(Display on)  |  |

| 7          | exit_sleep_mode +<br>set_display_on<br>sequence | exit_sleep_mode(11h)<br>set_display_on(29h)             | Sleep mode on                   | Sleep mode off<br>(Display on)  |  |

| 9          | set_display_on                                  |                                                         | Sleep mode off<br>(display off) | Sleep mode off<br>(Display on)  |  |

| 10         | sequence                                        | set_display_on(29h)                                     | Sleep mode off<br>(display on)  | Sleep mode off<br>(Display on)  |  |

| 11         | set_display_off                                 |                                                         | Sleep mode off<br>(display on)  | Sleep mode off<br>(Display off) |  |

| 12         | sequence                                        | <pre>set_display_off(28h)</pre>                         | Sleep mode off<br>(display off) | Sleep mode off<br>(Display off) |  |

| 13         |                                                 |                                                         | Sleep mode off<br>(display off) |                                 |  |

| 14         | enter_sleep_mode<br>sequence                    | enter_sleep_mode(10h)                                   | Sleep mode off<br>(Display on)  | Sleep mode on                   |  |

| 15         |                                                 | C                                                       | Sleep mode on                   |                                 |  |

| 17         |                                                 |                                                         | Sleep mode off<br>(display on)  |                                 |  |

| 18         | soft_reset<br>sequence                          | <pre>soft_reset(01h)</pre>                              | Sleep mode off<br>(Display off) | Sleep mode on                   |  |

| 19         |                                                 |                                                         | Sleep mode on                   |                                 |  |

| 21         | Deep standby mode<br>on sequence                | (RESET_N = High $\rightarrow$ Low)                      | Sleep mode on                   | Deep standby on                 |  |

| 22         | Deep standby mode<br>off sequence               | $(\text{RESET_N} = \text{Low} \rightarrow \text{High})$ | Deep standby on                 | Sleep mode on                   |  |

| <u></u>    | EC. NUMBER                                      | SPEC TITLE                                              |                                 | PAGE                            |  |

|            | SXXX-XXXX                                       | VS021XRM-NW0-6KP0 Prod                                  | duct Specification              | 22 OF 34                        |  |

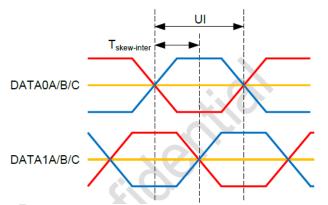

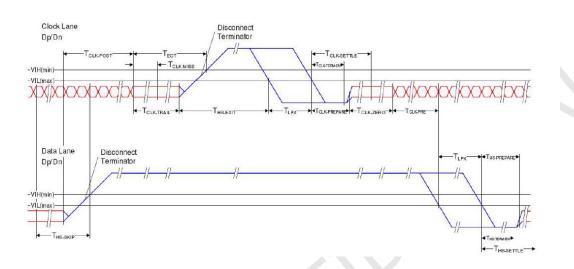

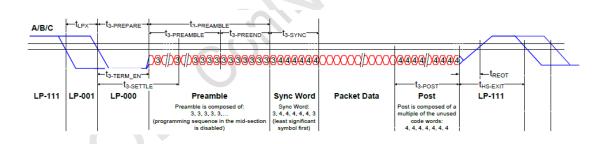

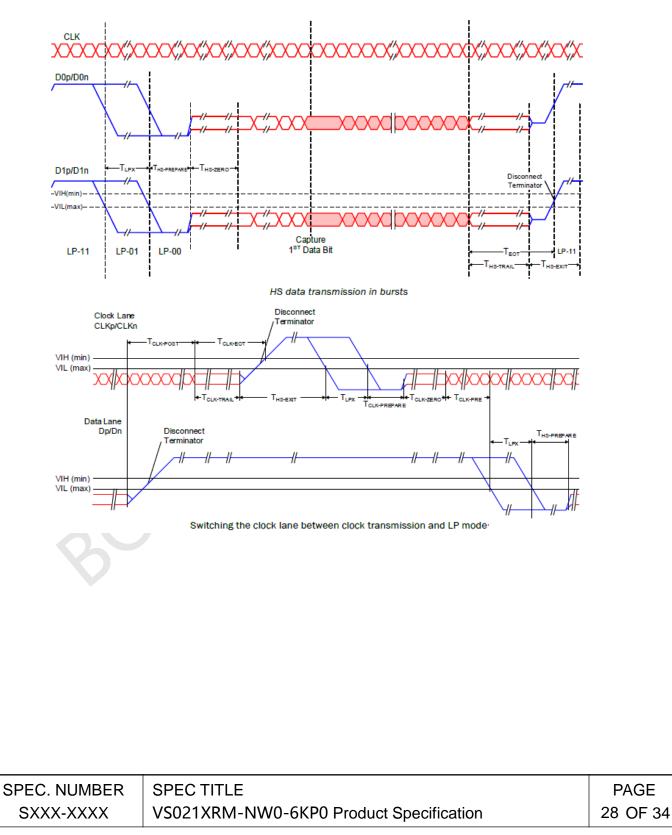

#### 7.4 MIPI Interface Characteristics

#### **MIPI DSI HS-RX Clock and Data-Clock Specifications**

| Item                   | Symbol          | Unit | Test Condition                               | Minimum | Typical | Maximu<br>m |

|------------------------|-----------------|------|----------------------------------------------|---------|---------|-------------|

| Symbol rate*           | fSYMBOL         | Msps | $IOVCC = DPHYVCC = 1.65 \sim \mathbf{1.95V}$ | 80      | -       | 1300        |

| UI instantaneous       | UI              | ns   | $IOVCC = DPHYVCC = 1.65 \sim \mathbf{1.95V}$ | 0.77    | _       | 12.5        |

| Data transfer<br>rate* | tDSIR           | Mbps | IOVCC = DPHYVCC = 1.65 ~ 1.95V               | 182     | _       | 2971        |

| Inter lane skew        | Tskew-<br>inter | UI   | IOVCC = DPHYVCC = 1.65 ~ 1.95V               | -3.5    | -       | +3.5        |

1 C-PHY data transfer rate is 2.28 times the C-PHY symbol rate.

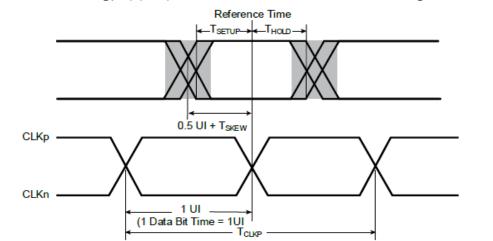

| Item                      | Symbol         | Unit | Test Condition                                                                                   | Minimum | Typical | Maximum | Footnote |

|---------------------------|----------------|------|--------------------------------------------------------------------------------------------------|---------|---------|---------|----------|

| DSICLK frequency          | <b>fDSICLK</b> | MHz  | IOVCC = DPHYVCC = 1.65 ~ 1.95V                                                                   | 250     | -       | 650     | 1        |

| DSICLK cycle time         | tCLKP          | ns   | IOVCC = DPHYVCC = 1.65 ~ 1.95V                                                                   | 1.54    | -       | 4       | 1        |

| DSI data transfer<br>rate | tDSIR          | Mbps | IOVCC = DPHYVCC = 1.65 ~ 1.95V                                                                   | 500     | -       | 1300    | 1        |

|                           |                | UI   | IOVCC = DPHYVCC = 1.65 ~ 1.95V                                                                   | 0.15    | -       | -       | 1, 3     |

| Data to clock setup       | +O CTUD        | ns   | DSI transfer rate ≦ 1000 Mbps                                                                    | 0.15    | -       | -       | 1, 2, 3  |

| time                      | tSETUP         | UI   | IOVCC = DPHYVCC = 1.65 ~ 1.95V                                                                   | 0.2     | -       | -       | 1, 3     |

|                           |                | ns   | DSI transfer rate $\geq$ 1000 Mbps                                                               | 0.13    | -       | -       | 1, 2, 3  |

|                           |                | UI   | IOVCC = DPHYVCC = 1.65 ~ 1.95V                                                                   | 0.15    | -       | -       | 1, 3     |

| Clock to data hold tHOLD  |                | ns   | DSI transfer rate ≦ 1000 Mbps<br>IOVCC = DPHYVCC = 1.65 ~ 1.95V<br>DSI transfer rate > 1000 Mbps | 0.15    | _       | -       | 1, 2, 3  |

|                           | THULD          | UI   |                                                                                                  | 0.2     | _       | -       | 1, 3     |

|                           |                | ns   |                                                                                                  | 0.13    | _       | _       | 1, 2, 3  |

1. Minimum 110 mV/-110 mV HS differential swing is required for display data transfer.

2. tSETUP/tHOLD times are measured without HS-TX jitter.

3. Minimum tSETUP/tHOLD Time is 0.15 UI or 0.20 UI. This value may change according to the DSI transfer rate.

# SPEC. NUMBER SPEC TITLE SXXX-XXXX VS021XRM-NW0-6KP0 Product Specification

PAGE 23 OF 34

B2006-5006-O (3/3)

# PRODUCT GROUP

REV

ISSUE DATE

#### TFT LCD PRODUCT

P1

2020.03.03

| Item                                                                                                                                                   | Symbol                     | Unit | Test Condition                    | Minimum               | Typical               | Maximu<br>m           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|-----------------------------------|-----------------------|-----------------------|-----------------------|

| Time to drive LP-000 to prepare<br>for high speed transmission                                                                                         | T3-PREPARE                 | Ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 38                    | -                     | 95                    |

| Time interval during high speed receiver<br>can receive high speed data starting at<br>the beginning of t <sub>3-PREPARE</sub>                         | T <sub>3-SETTLE</sub>      | Ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 95                    | _                     | 300                   |

| Time from driving LP-000<br>to sending sync word <sup>1</sup>                                                                                          | T3-PREPARE +<br>T3PREAMBLE | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 300ns*1               | _                     | -                     |

| Time to drive LP-111 after<br>a HS burst                                                                                                               | T <sub>HS-EXIT</sub>       | Ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 100                   | -                     | -                     |

| Time to drive LP-000<br>after a turnaround request                                                                                                     | T <sub>TA-GO</sub>         | _    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V |                       | 4 • T <sub>LPTX</sub> |                       |

| Time that the new transmitter waits after<br>the LP-100 state before transmitting the<br>bridge state (LP-000) during a link<br>turnaround             | T <sub>TA-SURE</sub>       | _    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 1 • T <sub>LPTX</sub> | _                     | 2 • T <sub>LPTX</sub> |

| Time that the new transmitter drives the<br>bridge state (LP-000) after accepting<br>control during a link turnaround                                  | T <sub>TA-GET</sub>        | _    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V |                       | 5 • T <sub>lptx</sub> |                       |

| Length of any low-power<br>state period                                                                                                                | T <sub>LPX</sub>           | Ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 50                    | _                     | _                     |

| Ratio of TLPX(MASTER)/TLPX(SLAVE)<br>between the master and<br>slave sides                                                                             | Ratio T <sub>LPX</sub>     |      | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 2/3                   | _                     | 3/2                   |

| Time that the transmitter continues<br>sending post words (4444444) after the<br>last associated data lane has<br>transitioned to LP mode <sup>2</sup> | Тзроят                     | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 224*2                 | -                     | _                     |

| Length of the low-power transmitter period                                                                                                             | Тіртх                      | Ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | _                     | (8/fosc)              | _                     |

<sup>1</sup> The minimum value of T<sub>3-PREPARE</sub> is 38 ns and the minimum value of T<sub>3-PREPARE</sub> is 14 UI, so the minimum value of T<sub>3-PREPARE</sub> + T<sub>3-PREAMBLE</sub> is calculated as 38 ns + 14 UI. However, there is a relation where T<sub>3-PREPARE</sub> + T<sub>3-PREAMBLE</sub> > T<sub>3-PREPARE</sub> + T<sub>3-PREAMBLE</sub> is the minimum value, T<sub>3-PREPARE</sub> + T<sub>3-PREPARE</sub> + T<sub>3-PREAMBLE</sub> is the same as the T<sub>3-PREPARE</sub> minimum value.

<sup>2</sup> The minimum value of T<sub>3-POST</sub> is defined as 7 UI in the CPHY specification. However, R63455 requires a T3<sub>-POST</sub> period at 224 UI. The CPHY specification states that the value of T<sub>3-POST</sub> should be adjustable at the transmitter from 7 UI to 224 UI in increments of 7 UI.

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 24 OF 34 |

**ISSUE DATE**

TFT LCD PRODUCT

P1

2020.03.03

| Item                                                                                                                                          | Symbol                                 | Unit | Test Condition                    | Minimum                                       | Typical | Maximum           |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|-----------------------------------|-----------------------------------------------|---------|-------------------|

| Time to drive LP-00 to<br>prepare<br>for HS transmission                                                                                      | T <sub>HS-PREPARE</sub>                | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 40 ns + 4 • UI                                | _       | 85 ns +<br>6 • UI |

| THS-PREPARE + time to drive HS-<br>O before the sync sequence                                                                                 | Ths-prepare<br>+ Ths-zero              | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 145ns + 10 • UI                               | _       | _                 |

| Time to drive flipped<br>differential state<br>after last payload data bit<br>of a HS transmission burst <sup>1, 2</sup>                      | T <sub>HS-TRAIL</sub>                  | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | max<br>(n • 8 • UI,<br>60 ns +<br>n • 4 • UI) | _       | _                 |

| Time to drive LP-11 after<br>a HS burst                                                                                                       | T <sub>HS-EXIT</sub>                   | ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 100                                           | -       | -                 |

| Time to drive LP-00<br>after a turnaround request                                                                                             | Tta-go                                 | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 4                                             | • Тиртх |                   |

| Time that the new TX waits<br>after the LP-10 state before<br>transmitting the bridge state<br>(LP-00) during a link<br>turnaround            | TTA-SURE                               | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 1 • T <sub>LPTX</sub>                         | _       | 2 • Tlptx         |

| Time that the new TX drives<br>the bridge state (LP-00) after<br>accepting control during a<br>link turnaround                                | T <sub>TA-GET</sub>                    | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 5 • T <sub>LPTX</sub>                         |         |                   |

| Length of any low-power<br>state period                                                                                                       | T <sub>LPX</sub>                       | ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 50                                            | -       | -                 |

| Ratio of TLPX(MASTER)/TLPX(SLAVE)<br>between the master and<br>slave sides                                                                    | Ratio T <sub>LPX</sub>                 | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 2/3                                           | -       | 3/2               |

| Time that the transmitter<br>continues sending HS clock<br>after the last associated<br>data lane has transitioned to<br>LP mode <sup>3</sup> | TCLK-POST                              | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 60 ns + 52 UI                                 | -       | -                 |

| T <sub>CLK-PREPARE</sub> +time for lead HS-<br>O drive period before starting<br>the clock                                                    | Tclk-prepare<br>+T <sub>clk-zero</sub> | ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 300                                           | -       | -                 |

| Time that the HS clock is<br>driven prior to any associated<br>data lane beginning the<br>transition from LP to HS<br>mode                    | Tolk-pre                               | UI   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 8                                             | _       | _                 |

| Time to drive LP-00 to<br>prepare<br>for HS clock transmission                                                                                | T <sub>CLK-PREPARE</sub>               | ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 38                                            | _       | 95                |

| Time to drive HS differential<br>state after last payload<br>clock bit of an HS<br>transmission burst                                         | T <sub>CLK-TRAIL</sub>                 | ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | 60                                            | _       | _                 |

SPEC. NUMBER SXXX-XXXX

VS021XRM-NW0-6KP0 Product Specification

SPEC TITLE

B2006-5006-O (3/3)

A4(210 X 297)

PAGE

25 OF 34

# PRODUCT GROUP

REV

ISSUE DATE

#### TFT LCD PRODUCT

P1

2020.03.03

| Item                                                                                       | Symbol | Unit | Test Condition                    | Minimum | Typical  | Maximum                    |

|--------------------------------------------------------------------------------------------|--------|------|-----------------------------------|---------|----------|----------------------------|

| Time from the start of<br>THS-TRAIL period to the start<br>of the LP-11 state <sup>2</sup> | Теот   | -    | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | _       | _        | 105 ns +<br>n • 12 •<br>UI |

| Length of the low-power TX<br>period when using the DSI-2<br>clock <sup>4, 5</sup>         | Τιρτχί | UI   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | _       | 1/fTXCLK | _                          |

| Length of the low-power TX<br>period when using the<br>internal OSC clock <sup>4, 5</sup>  | TLPTX2 | ns   | IOVCC = DPHYVCC =<br>1.65 ~ 1.95V | _       | 8/fosc   | _                          |

1. If a > b then max (a, b) = a, otherwise max (a, b) = b

Where n = 1 for forward direction HS mode.

R63455 works with this specification, although the last part of the internal process remains when the clock lane enters LP-11 and R63455 works without the remaining process if tCLK-POST is more than 512 UI.

R63455 uses the DSI clock from the host processor if the DSI-2 clock lane is active, and uses the internal oscillator clock if the DSI-2 clock lane is stopped.

5. See section "DSI-2 Control Setting (B6h)" (D-PHY) in this document for more information about the DSITXDIV register function.

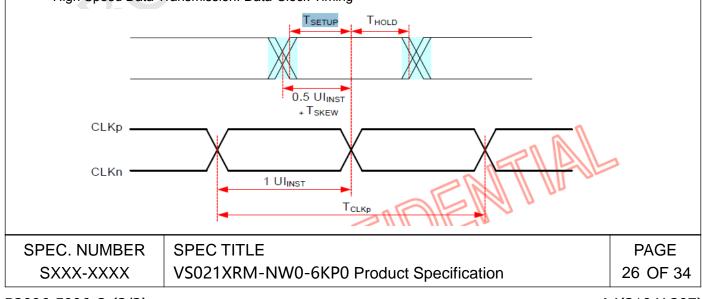

High speed mode

High Speed Data Transmission: Data-Clock Timing

B2006-5006-O (3/3)

#### Switching Clock lane Switching the Clock Lane between Clock Transmission and Low-Power Mode

#### Timing request between data transmission

| SPEC. NUMBER SPEC TITLE F                            |          |

|------------------------------------------------------|----------|

|                                                      | PAGE     |

| SXXX-XXXX VS021XRM-NW0-6KP0 Product Specification 27 | 27 OF 34 |

2020.03.03

B2006-5006-O (3/3)

| BOE |  |

|-----|--|

|-----|--|

P1

2020.03.03

## 7.6 Initial Code Setting

## □ Speed & Porch Setting (for reference only)

|          | It         | tem                    | Symbol  | Min. | Тур.  | Max. | Unit |

|----------|------------|------------------------|---------|------|-------|------|------|

|          |            | Frame Rate             | -       | -    | 70/90 |      | Hz   |

| On a sit |            | Line Time              | -       | -    | 2.5   | -    | us   |

| Speed*   |            | Dot CLK                | -       | -    | -     | -    | MHz  |

|          |            | MIPI Speed             | -       | -    | 700   | -    | Mbps |

|          |            | Horizontal total time  | Htotal  | -    | 1651  | -    | dot  |

|          | Horizontal | Horizontal Active time | Hactive | 1600 |       | dot  |      |

|          |            | Horizontal Pulse Width | Hsync   | -    | 1     | -    | dot  |

|          |            | Horizontal Back Porch  | НВР     | -    | 20    | -    | dot  |

| Doroh    |            | Horizontal Front Porch | HFP     | -    | 30    | -    | dot  |

| Porch    |            | Vertical Total         | Vtotal  | -    | 1780  | -    | line |

|          |            | Vertical Active        | Vactive |      | 1600  |      | line |

|          | Vertical   | Vertical Pulse Width   | Vsync   | -    | 1     | -    | line |

|          |            | Vertical Back Porch    | VBP     | -    | 29    | -    | line |

|          |            | Vertical Front Porch   | VFP     | -    | 150   | -    | line |

|          |            | Lane                   |         | -    | 4     | 8    | Lane |

\* The Driver IC supports VESA DSC V1.0 and V1.1 Data compression Decoder.

## □ Display Scan Direction

| ·        |          |             |           | _                  |                 |          |

|----------|----------|-------------|-----------|--------------------|-----------------|----------|

|          | Dat      | a Direction | 36h       |                    | P H Active Area | HFP      |

| 正向<br>扫描 |          |             | 00h       | V Active Area      | Active Area     |          |

| 反向<br>扫描 |          | Driver 10   | c0h       |                    |                 |          |

| SPEC. NL | JMBER    | SPEC TITLE  |           |                    |                 | PAGE     |

| SXXX-X   | XXXX     | VS021XRM-N  | W0-6KP0 P | roduct Specificati | on              | 30 OF 34 |

| 006 5006 | 0 (2 (2) | 1           |           |                    |                 |          |

B2006-5006-O (3/3)

| Β | Ο | Ε |

|---|---|---|

|   |   |   |

P1

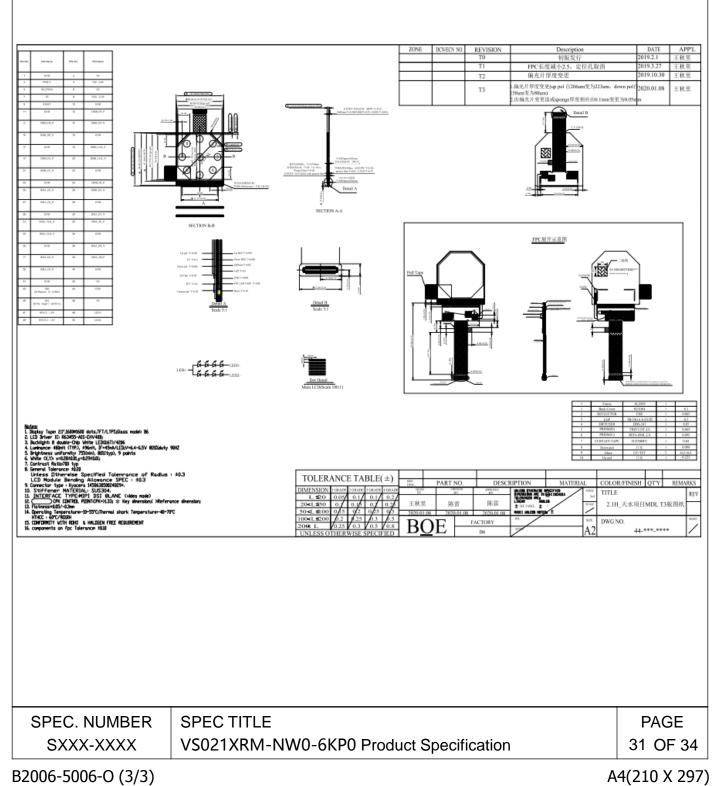

# **8.0 MECHANICAL CHARACTERISTICS**

P1

2020.03.03

# 9.0 RELIABILITY TEST

The Reliability test items and its conditions are shown in below.

| <table 7.="" reliability<="" th=""><th>y Test Conditions&gt;</th></table> | y Test Conditions> |

|---------------------------------------------------------------------------|--------------------|

|---------------------------------------------------------------------------|--------------------|

| No. | Test Items                                      | Conditions               |  |

|-----|-------------------------------------------------|--------------------------|--|

| 1   | High temperature storage                        | Ta = 70 °C, 48 hrs       |  |

| 2   | Low temperature storage                         | Ta = -30°C, 48 hrs       |  |

| 3   | High temperature & high humidity operation test | Ta = 60 °C, 90%RH, 48hrs |  |

| 4   | High temperature operation                      | Ta = 55 °C, 48 hrs       |  |

| 5   | Low temperature operation                       | Ta = -10 °C, 48 hrs      |  |

Remark : The Reliability test items can only be applied to the BLU 20% on duty Mode

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 32 OF 34 |

B2006-5006-O (3/3)

P1

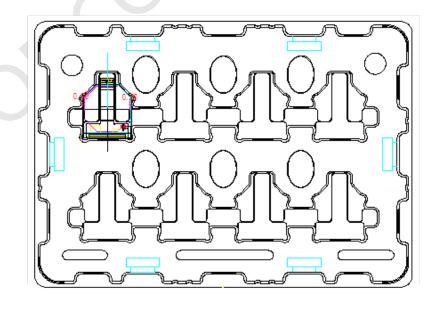

# **10.0 PACKING INFORMATION**

## **10.1 Packing Description**

| No. | Description        | Quantity            | Size (mm)            |

|-----|--------------------|---------------------|----------------------|

| 1   | LCM per Box        | 200pcs              |                      |

| 2   | LCM per Tray       | 8pcs                |                      |

| 3   | PET Tray           | 26ea<br>(1ea empty) | 320mm ×225mm×16mm    |

| 4   | Antistatic Bag     | 1ea                 | 650×550×0.08mm       |

| 5   | PE Bag             | 1ea                 | 480(L)×380(W)        |

| 6   | inner box          | 1ea                 | 375×280×290mm        |

| 7   | Out Box            | 1ea                 | 545(L)×380(W)×270(H) |

| 8   | Distribution label |                     |                      |

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 33 OF 34 |

B2006-5006-O (3/3)

P1

2020.03.03

## 10.2 Packing Procedure

| Put 8pcs LCM into the PET tray;                                         | Stack the Trays with LCMs in<br>25 layers, then cover 1 empty<br>tray on the top; 200pcs LCM<br>/25Tray | Put the 26 layers of Tray<br>electrostatic shielding ba                 |                 |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|

|                                                                         | 8 7 6 5 4 3 1 1 1                                                                                       |                                                                         |                 |

| Step 1                                                                  | Step 2                                                                                                  |                                                                         | Step 3          |

| Put the Pet bag into the inner box                                      | Put the inner box into the Out<br>Box                                                                   | Seal the outer box and r<br>lable on the surface of o<br>84pcs LCMs/Box |                 |

|                                                                         |                                                                                                         |                                                                         |                 |

| Step 4                                                                  | Step 5                                                                                                  |                                                                         | Step 6          |

| The 8 cartons are stacked in one layer.They will be stacked in 4 layers |                                                                                                         |                                                                         |                 |

|                                                                         |                                                                                                         |                                                                         |                 |

| PEC. NUMBER SPEC TIT<br>SXXX-XXXX VSO219XRI                             | LE<br>M-NW0-6KP0 Product Specifi                                                                        | cation                                                                  | PAGE<br>34 OF 3 |

B2006-5006-O (3/3)

| serial | 1   | 2    | 3         | 4  | 5  | 6   | 7    | 8   | 9                                   | 10 | 11 | 12   | 13 |

|--------|-----|------|-----------|----|----|-----|------|-----|-------------------------------------|----|----|------|----|

| code   | Х   | Х    | S         | 3  | 1  | 5   | В    | 0   | 0                                   | 0  | 1  | Н    | D  |

| Des.   | GBN | Code | grad<br>e | B3 | Υe | ear | Mon. | Rev | Serial no.(36 decimal, without I,O) |    |    | I,O) |    |

Year: 2015—15, 2016—16 Month: 1~12→ 1~9, A, B, C

| SPEC. NUMBER | SPEC TITLE                              | PAGE     |

|--------------|-----------------------------------------|----------|

| SXXX-XXXX    | VS021XRM-NW0-6KP0 Product Specification | 35 OF 34 |

|              |                                         |          |

B2006-5006-O (3/3)