# DM-OLEDC141-648

# 1.41" 320 x 360 AMOLED FULL COLOR DISPLAY PANEL WITH IN-CELL TOUCH-MIPI

### Contents

- 1 Revision History

- 2 Main Features

- 3 Pin Description

- 3.1 Panel Pin Description

- 4 Mechanical Drawing

- 4.1 Panel Mechanical Drawing

- 5 Optics & Electrical Characteristics

- 5.1 Optical Characteristics

- 5.2 Absolute Maximum Ratings

- 5.3 DC Characteristics

- 5.3.1 Display DC Characteristics

- 5.3.2 Display & TP Current Consumption

- 5.4 AC Characteristics

- 5.4.1 MIPI Interface Characteristics

- 5.4.2 Display RESET Timing Characteristics

- 5.4.3 Display Scan Direction & Coordinate

#### 6 Touch Performance

- 6.1 Touch Sensor Drawing

- 6.2 Touch pattern design

- 6.3 Touch Specifications

- 7 Power ON/OFF Timing Sequence

- 8 Reliability

- 9 Warranty and Conditions

# 1 Revision History

| Date       | Changes       |

|------------|---------------|

| 2019-06-20 | First release |

### 2 Main Features

| Item                     | Specification        | Unit   |

|--------------------------|----------------------|--------|

| Diagonal Size            | 1.41                 | inch   |

| Display Mode             | AMOLED               | -      |

| Display Colors           | 16.7M(Maximum)       | Colors |

| Resolution               | 320 x RBG x 360      | pixel  |

| Controller IC            | WT010                | -      |

| Interface                | MIPI                 | -      |

| Active Area              | 23.84 x 26.82        | mm     |

| Module Dimension         | 26.04 x 31.00 x 0.66 | mm     |

| Frame rate (normal mode) | 60                   | Hz     |

| Weight                   | TBD                  | g      |

# 3 Pin Description

### 3.1 Panel Pin Description

| Pin No. | Symbol   | Function Description                                                           |  |  |  |

|---------|----------|--------------------------------------------------------------------------------|--|--|--|

| 1       | NC       | Floating                                                                       |  |  |  |

| 2       | TP_INT   | TP initial signal                                                              |  |  |  |

| 3       | NC       | Floating                                                                       |  |  |  |

| 4       | GND      | Ground                                                                         |  |  |  |

| 5       | VCI      | Driver analog power supply                                                     |  |  |  |

| 6       |          | (Power IC need to follow AUO's suggestion)                                     |  |  |  |

| 7       | GND      | Ground                                                                         |  |  |  |

| 8       | SWIRE    | SWIRE signal for PWR IC control<br>(Power IC need to follow AUO' s suggestion) |  |  |  |

| 9       | TE       | Vsync (vertical sync) signal output from panel to avoid tearing effect         |  |  |  |

| 10      | REST     | Device reset signal (0 : enable ; 1 : Disable)                                 |  |  |  |

| 11      | GND      | Ground                                                                         |  |  |  |

| 12      | VDDIO    | Power supply for interface system except MIPI interface                        |  |  |  |

| 13      | MTP      | Power supply for OTP                                                           |  |  |  |

| 14      | ELVDD    | AMOLED positive power supply                                                   |  |  |  |

| 15      |          | (Power IC need to follow AUO' s suggestion)                                    |  |  |  |

| 16      | ELVSS    | AMOLED negative power supply                                                   |  |  |  |

| 17      |          | (Power IC need to follow AUO' s suggestion)                                    |  |  |  |

| 18      | GND      | Ground                                                                         |  |  |  |

| 19      | IDF      | Panel ID pin                                                                   |  |  |  |

| 20      | GND      | Ground                                                                         |  |  |  |

| 21      | DSI_D0N  | MIPI negative data signal                                                      |  |  |  |

| 22      | DSI_D0P  | MIPI positive data signal                                                      |  |  |  |

| 23      | GND      | Ground                                                                         |  |  |  |

| 24      | DSI_CLKN | MIPI negative clock signal                                                     |  |  |  |

| 25      | DSI_CLKP | MIPI positive clock signal                                                     |  |  |  |

| 26      | GND      | Ground                                                                         |  |  |  |

| 27      | NC       | Floating                                                                       |  |  |  |

| 28      | TP_SDA   | TP Data signal                                                                 |  |  |  |

| 29      | TP_SCL   | TP Clock signal                                                                |  |  |  |

| 30      | TP_RST   | TP Reset signal                                                                |  |  |  |

Note 1 : I = input ; O = output ; P = Power ; I/O = input / Output; NC= No Connection.

Note 2 : AUO suggest only use MIPI I/F, and pin of SPI I/F is connected as below.

(SCL & DCX & SDI & SDO pin is GND, and CSX is connected to VDDIO.)

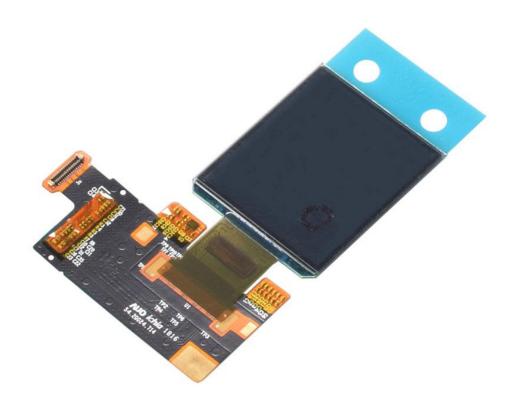

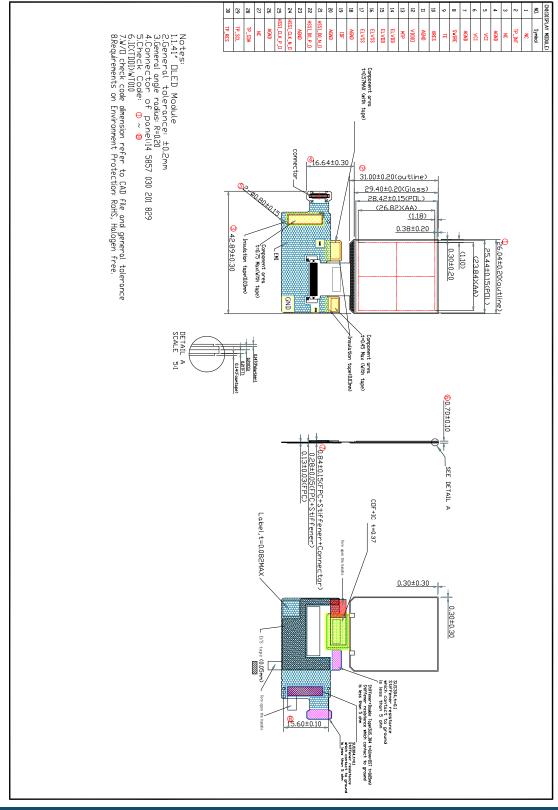

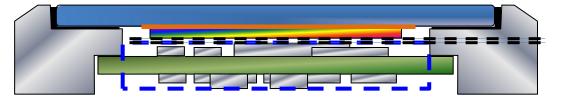

### 4 Mechanical Drawing

### 4.1 Panel Mechanical Drawing

# 5 Optics & Electrical Characteristics

#### 5.1 Optical Characteristics

| Item               | Symbol          | Min   | Тур   | Max   | Unit              | Remark     |  |

|--------------------|-----------------|-------|-------|-------|-------------------|------------|--|

| View Angles TOP    | ΘU              | 80    | -     | -     | 0                 | -          |  |

| View Angles Bottom | ΘD              | 80    | -     | -     | 0                 | -          |  |

| View Angles Right  | ΘR              | 80    | -     | -     | 0                 | -          |  |

| View Angles Left   | ΘL              | 80    | -     | -     | 0                 | -          |  |

| C.I.E. (White)     | (x)             | 0.28  | 0.30  | 0.32  |                   | C.I.E.1931 |  |

|                    | (y)             | 0.29  | 0.31  | 0.33  | -                 | 0.1.1.1751 |  |

| C.I.E(Red)         | (x)             | 0.64  | 0.67  | 0.70  |                   | C.I.E.1931 |  |

| C.I.E(Red)         | (y)             | 0.30  | 0.33  | 0.36  | _                 | C.I.E.1951 |  |

| C.I.E(Green)       | (x)             | 0.186 | 0.236 | 0.286 |                   | C.I.E.1931 |  |

| C.I.E(Gleen)       | (y)             | 0.661 | 0.711 | 0.761 | -                 | C.I.E.1951 |  |

| C.I.E(Blue)        | (x)             | 0.090 | 0.130 | 0.170 |                   | C.I.E.1931 |  |

|                    | (y)             | 0.025 | 0.065 | 0.105 | -                 | C.I.E.1951 |  |

| Pixel Luminance    | L <sub>br</sub> | 315   | 350   | 385   | cd/m <sup>2</sup> | Note 1     |  |

| Contrast Ratio     | CR              | 10000 | -     | -     | -                 | Note 2     |  |

Note 1: The brightness measurement shall be done at the center of the display with a full white image.

Note 2: Definition of contrast ratio:

Contrast ratio is calculated with the following formula:

Contrast ratio (CR) =

Photo detector output when OLED is at "White" state

Photo detector output when OLED is at "Black

#### 5.2 Absolute Maximum Ratings

| Parameter              | Symbol            | Min  | Max | Unit |

|------------------------|-------------------|------|-----|------|

| Analog Supply Voltage  | V <sub>CI</sub>   | -0.3 | 5.5 | V    |

| Digital Supply Voltage | V <sub>DDIO</sub> | -0.3 | 5.5 | V    |

| ELVDD Supply Voltage   | ELVDD             | -    | 5.0 | V    |

| ELVSS Supply Voltage   | ELVSS             | -5.0 | -   | V    |

Note: If the module exceeds the absolute maximum ratings, it may be damaged permanently.

#### 5.3 DC Characteristics

#### 5.3.1 Display DC Characteristics

| I V                       |                   |                         |       |                         |      |

|---------------------------|-------------------|-------------------------|-------|-------------------------|------|

| Item                      | Symbol            | Min                     | Тур.  | Max                     | Unit |

| Battery Supply Voltage    | V <sub>CI</sub>   | 2.75                    | 2.8   | 3.0                     | V    |

| Digital Supply Voltage    | V <sub>DDIO</sub> | 1.65                    | 1.8   | 1.95                    | V    |

| ELVDD Supply Voltage      | ELVDD             | 4.55                    | 4.6   | 4.65                    | V    |

| ELVSS Supply Voltage      | ELVSS             | -2.35                   | -2.40 | -2.45                   | V    |

| Low Level Input Voltage   | VIL               | 0                       | -     | 0.2 x V <sub>DDIO</sub> | V    |

| High Level Input Voltage  | VIH               | 0.8 x V <sub>DDIO</sub> | -     | V <sub>DDIO</sub>       | V    |

| Low Level Output Voltage  | Vol               | 0                       | -     | 0.2 x V <sub>DDIO</sub> | V    |

| High Level Output Voltage | V <sub>OH</sub>   | 0.8 x V <sub>DDIO</sub> | -     | V <sub>DDIO</sub>       | V    |

Note : The operation is guaranteed under the recommended operating conditions only. The operation is not guaranteed if a quick voltage change occurs during the operation. To prevent the noise, a bypass capacitor must be inserted into the line closed to the power pin.

#### 5.3.2 Display & TP Current Consumption

| Item         | Symbol             | Condition               | Min | Тур. | Max  | Unit | Remark |

|--------------|--------------------|-------------------------|-----|------|------|------|--------|

| Panel Power  | POLED              | ELVDD:4.6V              | -   | -    | 119  | mW   | Note1  |

| Fallel Fower | Ioled              | ELVSS:-2.4V             | -   | -    | 17   | mA   | Note1  |

| Normal IC    | P <sub>VCI</sub>   | V <sub>CI</sub> : 2.8V  | -   | 13.6 | 15.7 | mW   | Note2  |

|              | I <sub>VCI</sub>   | V CI . 2.0 V            | -   | 4.9  | 5.6  | mA   | Note2  |

| (with TP)    | P <sub>VDDIO</sub> | V <sub>DDIO</sub> :1.8V | -   | 4.0  | 4.6  | mW   | Note2  |

|              | Ivddio             | V DDIO .1.0 V           | -   | 2.2  | 2.6  | mA   | Note2  |

| Sleep IC     | P <sub>VCI</sub>   | V <sub>CI</sub> : 2.8V  | -   | -    | 0.76 | mW   | Note3  |

| Sheep te     | Ivci               | V CI . 2.0 V            | -   | -    | 0.27 | mA   | Note3  |

| (with TP)    | P <sub>VDDIO</sub> | V <sub>DDIO</sub> :1.8V | -   | -    | 0.98 | mW   | Note3  |

|              | I <sub>VDDIO</sub> | V DDIO :1.8 V           | -   | -    | 0.54 | mA   | Note3  |

Note 1: Based on L255 (350nits) full white pattern.

Note 2: Based on black pattern. MIPI-DSI frame rate 60Hz command mode.

Note 3: Power consumption spec. is base on TP FW of the engineer version. The power consumption may be revised according to the TP FW version.

#### 5.4 AC Characteristics

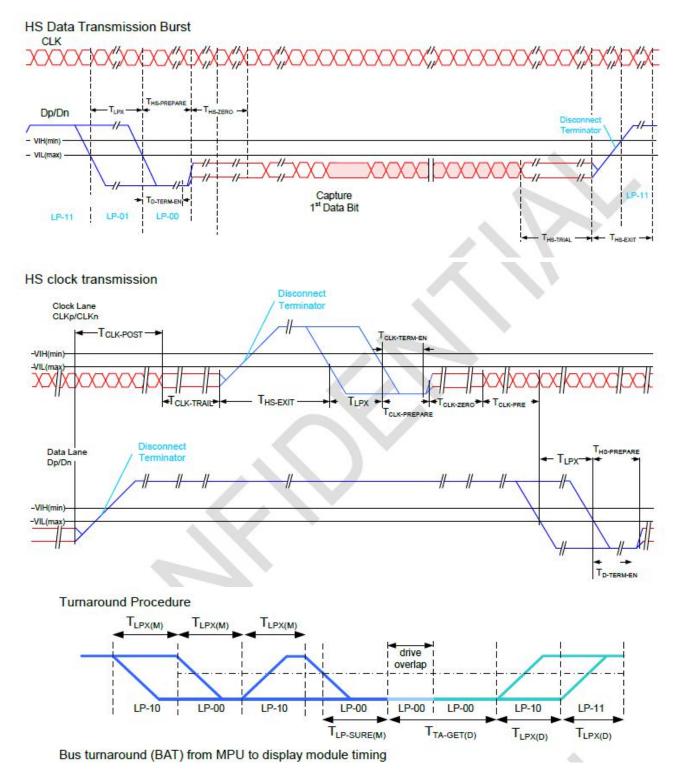

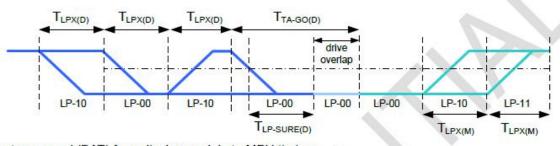

#### 5.4.1 MIPI Interface Characteristics

Bus turnaround (BAT) from display module to MPU timing

#### **Timing Parameters**

| Symbol                                                    | Description                                                                                                                                                                                                                      | Min                              | Typ. | Max             | Unit |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|-----------------|------|

| T <sub>CLK-POST</sub>                                     | Time that the transmitter continues to<br>send HS clock after the last associated<br>Data Lane has transitioned to LP<br>Mode. Interval is defined as the period<br>from the end of THS-TRAIL to the<br>beginning of TCLK-TRAIL. | 60ns + 52*UI                     |      |                 | ns   |

| T <sub>CLK-TRAIL</sub>                                    | Time that the transmitter drives the<br>HS-0 state after the last payload clock<br>bit of a HS transmission burst.                                                                                                               | 60                               |      |                 | ns   |

| T <sub>HS-EXIT</sub>                                      | Time that the transmitter drives LP-11 following a HS burst.                                                                                                                                                                     | 300                              |      |                 | ns   |

| T <sub>CLK</sub> -term-<br>en                             | Time for the Clock Lane receiver to<br>enable the HS line termination, starting<br>from the time point when Dn crosses<br>VIL MAX                                                                                                | Time for Dn to<br>reach VTERM-EN |      | 38              | ns   |

| Tclk-<br>prepare                                          | Time that the transmitter drives the<br>Clock Lane LP-00 Line state<br>immediately before the HS-0 Line state<br>starting the HS transmission.                                                                                   | 38                               |      | 95              | ns   |

| T <sub>CLK-PRE</sub>                                      | Time that the HS clock shall be driven<br>by the transmitter prior to any<br>associated Data Lane beginning the<br>transition from LP to HS mode.                                                                                | 8                                |      |                 | UI   |

| T <sub>CLK</sub> -<br>prepare +<br>T <sub>CLK</sub> -zero | T <sub>CLK-PREPARE</sub> + time that the<br>transmitter drives the HS-0 state prior<br>to starting the Clock.                                                                                                                    | 300                              |      |                 | ns   |

| T <sub>D-TERM-EN</sub>                                    | Time for the Data Lane receiver to<br>enable the HS line termination, starting<br>from the time point when Dn crosses<br>VIL MAX                                                                                                 | Time for Dn to<br>Reach Vterm-en |      | 35 ns<br>+4*UI  |      |

| T <sub>HS-PREPARE</sub>                                   | Time that the transmitter drives the<br>Data Lane LP-00 Line state<br>immediately before the HS-0 Line state<br>starting the HS transmission                                                                                     | 40ns + 4*UI                      |      | 85 ns +<br>6*UI | ns   |

| T <sub>HS-PREPARE</sub><br>+ T <sub>HS-ZERO</sub>         | THS-PREPARE + time that the<br>transmitter drives the HS-0 state prior<br>to transmitting the Sync sequence.                                                                                                                     | 145ns + 10*UI                    |      |                 | ns   |

| T <sub>HS</sub> -T <sub>RAIL</sub>                        | Time that the transmitter drives the<br>flipped differential state after last<br>payload data bit of a HS transmission<br>burst                                                                                                  | 60ns + 4*UI                      |      |                 | ns   |

| TLPX(M)                  | Transmitted length of any Low-Power state period of MCU to display module                                                                | 50      |                       | 150                   | ns |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|-----------------------|----|

| T <sub>TA-SURE(M)</sub>  | Time that the display module waits<br>after the LP-10 state before<br>transmitting the Bridge state (LP-00)<br>during a Link Turnaround. | Tlpx(m) |                       | 2*T <sub>LPX(M)</sub> | ns |

| T <sub>LPX(D)</sub>      | Transmitted length of any Low-Power state period of display module to MCU                                                                | 50      |                       | 150                   | ns |

| T <sub>TA-GET(D)</sub>   | Time that the display module drives<br>the Bridge state (LP-00) after accepting<br>control during a Link Turnaround.                     |         | 5*TLPX(D)             |                       | ns |

| T <sub>TA-GO(D)</sub>    | Time that the display module drives<br>the Bridge state (LP-00) before<br>releasing control during a Link<br>Turnaround.                 |         | 4*T <sub>LPX(D)</sub> |                       | ns |

| T <sub>TA</sub> -sure(d) | Time that the MPU waits after the LP-<br>10 state before transmitting the Bridge<br>state (LP-00) during a Link<br>Turnaround.           | Tlpx(d) |                       | 2*T <sub>LPX(D)</sub> | ns |

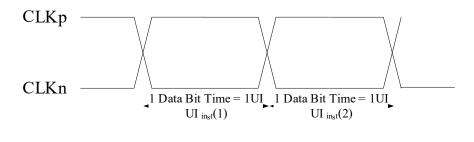

#### **DDR Clock Definition**

$-1 \text{ DDR Clock Period} = \text{UI}_{inst}(1) + \text{UI}_{inst}(2) - \mathbf{E}$

| Clock Parameter | Symbol | Min | Тур | Max  | Units |

|-----------------|--------|-----|-----|------|-------|

| UI instataneous | UIinst | 2   |     | 12.5 | ns    |

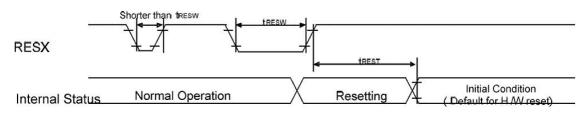

#### 5.4.2 Display RESET Timing Characteristics

#### Reset input timing

| Symbol            | Parameter                    | Related Pins | Min | Тур | Max | Note                                        | Unit |

|-------------------|------------------------------|--------------|-----|-----|-----|---------------------------------------------|------|

| t <sub>RESW</sub> | *1) Reset low<br>pulse width | RESX         | 10  | -   | -   | -                                           | μs   |

|                   | *2) Reset                    | -            | -   | -   | 5   | When reset applied during Sleep in mode     | ms   |

| t <sub>REST</sub> | complete time                | -            |     | -   | 120 | When reset applied<br>during Sleep out mode | ms   |

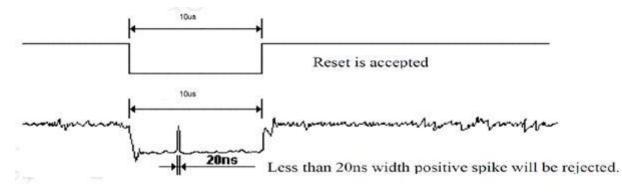

Note 1. Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below.

| RESX Pulse           | Action                         |

|----------------------|--------------------------------|

| Shorter than 5µs     | Invalid Reset                  |

| Longer than 10µs     | Valid Reset                    |

| Between 5µs and 10µs | Reset Initialigation Precedure |

Note 2. During the resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out – mode. The display remains the blank state in Sleep In – mode) and then return to Default condition for H/W reset.

- Note 3. During Reset Complete Time, data in OTP will be latched to internal register during this period. This loading is done every time when there is H/W reset complete time (tREST) within 5ms after a rising edge of RESX.

- Note 4. Spike Rejection also applies during a valid reset pulse as shown below:

Note 5. It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

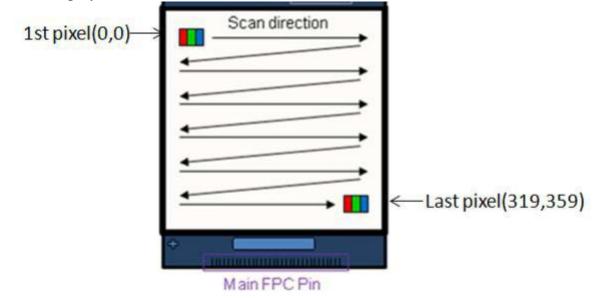

5.4.3 Display Scan Direction & Coordinate

# 6 Touch Performance

### 6.1 Touch Sensor Drawing

| Pad1 | Pad2  | Pad11 | Pad24 | Pad25 |

|------|-------|-------|-------|-------|

| Pad3 | Pad4  | Pad12 | Pad22 | Pad23 |

| Pad5 | Pad6  | Pad15 | Pad20 | Pad21 |

| Pad7 | Pad8  | Pad14 | Pad18 | Pad19 |

| Pad9 | Pod10 | Pad13 | Pad16 | Pad17 |

### 6.2 Touch pattern design

| i                             |           |

|-------------------------------|-----------|

| Item                          | TP sensor |

| Number of touch panel sensors | 25        |

|                               |           |

### 6.3 Touch Specifications

#### **TP** performance

| No. | Ite         | em                       | Spec.                                           |

|-----|-------------|--------------------------|-------------------------------------------------|

| 1   | Multi-      | Finger                   | 2                                               |

| 2   | Repor       | t Rate                   | ≥90Hz                                           |

|     |             | Accuracy<br>(at Ø 6 mm)  | Non-border $\leq 1.5$ mm,<br>Border $\leq 2$ mm |

| 3   | Performance | Linearity<br>(at Ø 6 mm) | Non-border $\leq 1.5$ mm,<br>Border $\leq 2$ mm |

|     |             | Jitter<br>(at Ø 6 mm)    | Non-border $\leq 1.5$ mm,<br>Border $\leq 2$ mm |

Design requirements of in-cell touch are as follows.

1. Cover lens design - Type: Glass,  $\epsilon \ge 7.6$ , Thickness:  $\le 1.2$ mm.

2. System gap  $\ge 0.6$ mm (Base on cover lens thickness =0.8mm), When the cover lens is thinner, the system gap needs more.

System gap:

- 1. the gap between bottom of AMOLED module and system parts/component.

- 2. The gap excludes system part thickness tolerance.

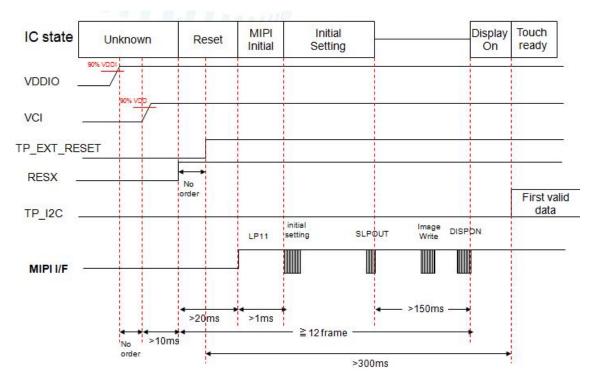

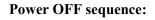

# 7 Power ON/OFF Timing Sequence

#### **Power ON sequence:**

# 8 Reliability

| Test Item                                                                                        | Content of Test                                                                                                                                                             | Test Condition          | Note |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|

| High Temperature StorageEndurance test applying the high storage<br>temperature for a long time. |                                                                                                                                                                             | 70°C<br>240hrs          | 2    |

| Low Temperature Storage                                                                          | Endurance test applying the high storage temperature for a long time.                                                                                                       | -30°C<br>240hrs         | 1,2  |

| High Temperature Operation                                                                       | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.                                                      | 60°C<br>240hrs          | -    |

| Low Temperature Operation                                                                        | Endurance test applying the electric stress<br>under low temperature for a long time.                                                                                       | -20 °C<br>240hrs        | 1    |

| High Temperature/<br>Humidity Operation                                                          | The module should be allowed to stand at 60°C,90%RH max, for 96hrs under no-load condition excluding the polarizer. Then taking it out and drying it at normal temperature. | 60°C,90%RH<br>240hrs    | 1,2  |

| Thermal Shock Resistance                                                                         | The sample should be allowed stand the<br>following 10 cycles of operation<br>-40°C 25°C 85°C.<br>30min 5min 30min.<br>1 cycle.                                             | -40°C/70°C<br>100cycles | -    |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal. Temperature and humidity after remove from the rest chamber.

### 9 Warranty and Conditions

http://www.displaymodule.com/pages/faq HYPERLINK "http://www.displaymodule.com/pages/faq"