DM-OLEDC13-621P 1.27" 128x96 RGB Color OLED DISPLAY PANEL - SPI, MCU

#### Contents

- 1 Revision History

- 2 Main Features

- 3 Pin Description

- 3.1 Panel Pin Description

- 4 Mechanical Drawing

- 5 Electrical Characteristics

- 6 Optical Characteristics

- 7 Timing Characteristics

- 7.1 Serial Interface Timing Characteristics: (4-wire SPI)

- 7.2 Serial Interface Timing Characteristics: (3-wire SPI)

- 7.3 68XX-Seriel MPU Parallel Interface Timing Characteristics

- 7.4 80XX-Seriel MPU Parallel Interface Timing Characteristics

- 8 Functional Specification

- 8.1 Power down and Power up Sequence

- 8.1.1 Power up Sequence

- 8.1.2 Power down Sequence

- 8.2 Reset Circuit

- 9 Actual Application Example

- 10 Reliability

- Warranty and Conditions

# 1 Revision History

| Date       | Changes                                                  |

|------------|----------------------------------------------------------|

| 2015-03-13 | First release                                            |

| 2018-05-29 | Mainboard update to new version ,Interface change to SPI |

### 2 Main Features

| Item             | Specification                 | Unit   |

|------------------|-------------------------------|--------|

| Diagonal Size    | 1.27                          | inch   |

| Display Mode     | Passive Matrix OLED           | -      |

| Display Colors   | 262,144                       | Colors |

| Resolution       | 128(RGB) x 96                 | pixel  |

| Controller IC    | SSD1351                       | -      |

| Duty             | 1/96                          | duty   |

| Interface        | 3/4 wire SPI, 8 bit 68XX/80XX | -      |

| Power Supply     | 2.8V                          | V      |

| Active Area      | 25.708 x 19.28                | mm     |

| Module Dimension | 33.7 x 26.9                   | mm     |

| Weight           | 2.92                          | g      |

# 3 Pin Description

### 3.1 Panel Pin Description

| Pin No. | Symbol  | Function Description                                                                |                          |                           |  |  |

|---------|---------|-------------------------------------------------------------------------------------|--------------------------|---------------------------|--|--|

|         | Ţ       | Reserved Pin (Supporting Pi                                                         | in)                      |                           |  |  |

| 1       | NC(GND) | The supporting pins can red                                                         |                          | m stresses on the         |  |  |

|         | , , ,   | function pins. These pins mu                                                        |                          |                           |  |  |

|         |         | Power Supply for OEL Pane                                                           |                          | 8                         |  |  |

| 2       | VCC     | This is the most positive vol                                                       |                          | chip.                     |  |  |

| _       | ,       | It must be connected to exte                                                        |                          | P                         |  |  |

|         |         | Voltage Output High Level                                                           |                          |                           |  |  |

| 3       | VCOMH   | This pin is the input pin for                                                       |                          | th level for COM signals. |  |  |

|         |         | A tantalum capacitor should                                                         |                          |                           |  |  |

|         |         | Power Supply for I/O Pin                                                            |                          | 1                         |  |  |

|         |         | This pin is a power supply p                                                        | in of I/O buffer. It she | ould be connected to VCI  |  |  |

| 4       | VDDIO   | or external source. All I/O si                                                      |                          |                           |  |  |

|         | ,       | When I/O signal pins (BS0~                                                          | •                        |                           |  |  |

|         |         | they should be connected to                                                         |                          | ) pui iigii,              |  |  |

|         |         | Voltage Output Low Level f                                                          |                          |                           |  |  |

|         |         | This is segment voltage refe                                                        |                          |                           |  |  |

| 5       | VSL     | When external VSL is not us                                                         |                          | e left open.              |  |  |

|         |         | When external VSL is used,                                                          |                          |                           |  |  |

|         |         | diode to ground.                                                                    | 1                        |                           |  |  |

|         |         | Reserved Pin                                                                        |                          |                           |  |  |

| 6       | N.C.    | The N.C. pins between function pins are reserved for compatible and                 |                          |                           |  |  |

|         |         | flexible design.                                                                    |                          |                           |  |  |

|         |         | Host Data Input/Output Bus                                                          |                          |                           |  |  |

|         |         | These pins are 8-bit bi-direc                                                       | tional data bus to be o  | connected to the          |  |  |

| 7~14    | D7~D0   | microprocessor's data bus. When serial mode is selected, D1 will be the             |                          |                           |  |  |

|         |         | serial data input SDIN and I                                                        |                          |                           |  |  |

|         |         | Unused pins must be connect                                                         |                          |                           |  |  |

|         |         | Read/Write Enable or Read                                                           |                          |                           |  |  |

|         |         | This pin is MCU interface in                                                        | put. When interfacing    | g to a 68XX-series        |  |  |

|         |         | microprocessor, this pin will                                                       | l be used as the Enabl   | e (E) signal. Read/write  |  |  |

|         |         | operation is initiated when the                                                     | his pin is pulled high   | and the CS# is pulled     |  |  |

| 15      | E/RD#   | low.                                                                                |                          |                           |  |  |

|         |         | When connecting to an 80X                                                           |                          |                           |  |  |

|         |         | (RD#) signal. Data read ope                                                         | ration is initiated whe  | n this pin is pulled low  |  |  |

|         |         | and CS# is pulled low.                                                              |                          |                           |  |  |

|         |         | When serial mode is selected                                                        | d, this pin must be con  | nnected to VSS.           |  |  |

|         |         | Read/Write Select or Write                                                          |                          | 60777                     |  |  |

|         |         | This pin is MCU interface in                                                        |                          | _                         |  |  |

|         |         | microprocessor, this pin will                                                       |                          |                           |  |  |

| 1.0     | D/MIII  | input. Pull this pin to "High"                                                      | for read mode and p      | ull it to "Low" for write |  |  |

| 16      | R/W#    | mode.                                                                               | in animated district     |                           |  |  |

|         |         | When 80XX interface mode is selected, this pin will be the Write (WR#)              |                          |                           |  |  |

|         |         | input. Data write operation is initiated when this pin is pulled low and the        |                          |                           |  |  |

|         |         | CS# is pulled low. When serial mode is selected, this pin must be connected to VSS. |                          |                           |  |  |

|         |         |                                                                                     |                          | meeted to vss.            |  |  |

|         |         | Communicating Protocol Se                                                           |                          | the following table:      |  |  |

| 17      | BS1     | These pins are MCU interface                                                        | •                        |                           |  |  |

| 18      | BS0     | 2 wire CDI                                                                          | BS0                      | BS1                       |  |  |

|         |         | 3-wire SPI                                                                          | 1                        | 0                         |  |  |

|         |         | 4-wire SPI                                                                          | 0                        | 0                         |  |  |

|          |                | 68XX-parallel (8-bit)                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                | 1                            |  |  |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|--|--|

|          |                | 80XX-parallel (8-bit)                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 1                            |  |  |

|          |                |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                  |                              |  |  |

| 19       | CS#            | Chip Select This pin is the chip select input. The chip is enabled for MCU communication only when CS# is pulled low.                                                                                                                                                                                                                                                                                             |                                                  |                              |  |  |

| 20       | D/C#           | Data/Command Control This pin is Data/Command control pin. When the pin is pulled high, the input at D7~D0 is treated as display data. When the pin is pulled low, the input at D7~D0 will be transferred to the command register. For detail relationship to MCU interface signals, please refer to the Timing Characteristics Diagrams. When 3-wire serial mode is selected, this pin must be connected to VSS. |                                                  |                              |  |  |

| 21       | RES#           | Power Reset for Controller a<br>This pin is reset signal input.<br>is executed.                                                                                                                                                                                                                                                                                                                                   |                                                  | , initialization of the chip |  |  |

| 22       | IREF           | Current Reference for Brightness Adjustment This pin is segment current reference pin. A resistor should be connected between this pin and VSS. Set the current lower than 12.5uA.                                                                                                                                                                                                                                |                                                  |                              |  |  |

| 23<br>24 | GPIO0<br>GPIO1 | General Purpose Input/Output<br>These pins could be left open<br>inputted/outputted. They are<br>circuit enabled/disabled cont                                                                                                                                                                                                                                                                                    | n individually or have<br>able to use as the ext | ernal DC/DC converter        |  |  |

| 25       | N.C.           | Reserved Pin The N.C. pins between funct flexible design.                                                                                                                                                                                                                                                                                                                                                         | ion pins are reserved                            | for compatible and           |  |  |

| 26       | VDD            | Power Supply for Core Logi<br>This is a voltage supply pin v<br>capacitor should be connected<br>circumstances.                                                                                                                                                                                                                                                                                                   | which is regulated int                           |                              |  |  |

| 27       | VCI            | Power Supply for Operation<br>This is a voltage supply pin.<br>always be equal to or higher                                                                                                                                                                                                                                                                                                                       |                                                  |                              |  |  |

| 28       | VSS            | Ground of OEL System This is a ground pin. It also a driving voltages, and the ana ground.                                                                                                                                                                                                                                                                                                                        |                                                  |                              |  |  |

| 29       | N.C.           | Reserved Pin The N.C. pins between funct flexible design.                                                                                                                                                                                                                                                                                                                                                         | tion pins are reserved                           | for compatible and           |  |  |

| 30       | N.C.(GND)      | Reserved Pin (Supporting Pi<br>The supporting pins can redu<br>function pins. These pins mu                                                                                                                                                                                                                                                                                                                       | ace the influences from                          |                              |  |  |

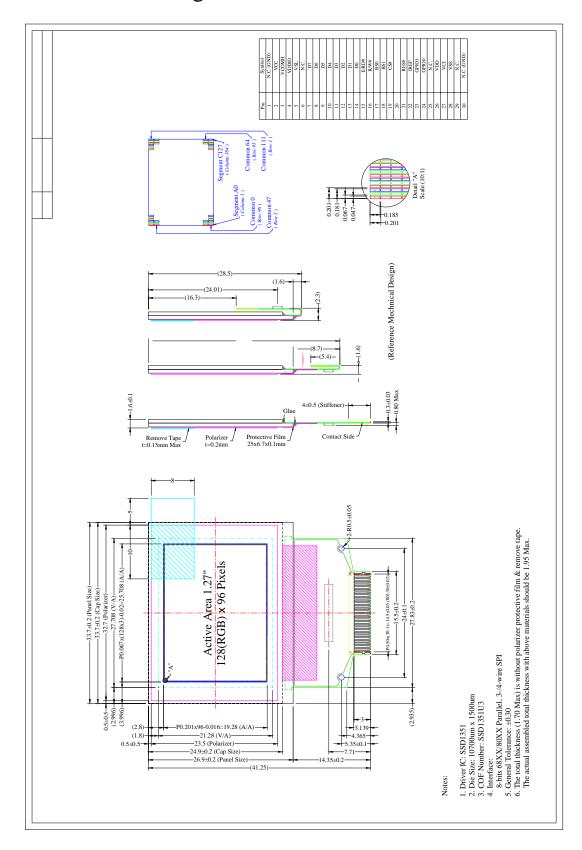

## 4 Mechanical Drawing

### 5 Electrical Characteristics

| Item                         | Symbol            | Condition    | Min                           | Тур. | Max                           | Unit         |

|------------------------------|-------------------|--------------|-------------------------------|------|-------------------------------|--------------|

| Supply Voltage for Operation | Vci               |              | 2.4                           | 3.3  | 3.5                           | V            |

| Supply Voltage for Logic     | $V_{\mathrm{DD}}$ |              | 2.4                           | 2.5  | 2.6                           | V            |

| Supply Voltage for I/O pins  | V <sub>DDIO</sub> |              | 1.65                          | 1.8  | Vci                           | V            |

| Supply Voltage for Display   | VCC               | Note1        | 11.5                          | 12   | 12.5                          | V            |

| Operation Current for VCI    | Ici               |              | -                             | 240  | 300                           | mA           |

| Low Level Input Voltage      | $V_{\rm IL}$      |              | 0                             | -    | $0.2xV_{DDIO}$                | V            |

| High Level Input Voltage     | $V_{\mathrm{IH}}$ |              | $0.8 \mathrm{xV}_\mathrm{DD}$ | -    | $V_{ m DDIO}$                 | V            |

| Low Level Output Voltage     | $V_{OL}$          |              | 0                             |      | $0.1 \text{xV}_{\text{DDIO}}$ | V            |

| High Level Output Voltage    | V <sub>OH</sub>   |              | $0.9 \text{xV}_{\text{DDIO}}$ |      | $V_{\mathrm{DDIO}}$           | V            |

| Operating Temperature        | TOP               | Absolute Max | -30                           |      | 70                            | $^{\circ}$   |

| Storage Temperature          | TST               | Absolute Max | -40                           |      | 80                            | $^{\circ}$ C |

Note1 :Brightness (Lbr) and Supply Voltage for Display (VCC) are subject to the change of the panel characteristics and the customer's request.

## 6 Optical Characteristics

| Item                 | Symbol  | Min    | Тур     | Max | Unit              |

|----------------------|---------|--------|---------|-----|-------------------|

| View Angles Top      | AV      |        | 80      |     | 0                 |

| View Angles Bottom   | AV      |        | 80      |     | 0                 |

| View Angles Left     | AH      |        | 80      |     | 0                 |

| View Angles Right    | AH      |        | 80      |     | 0                 |

| Response Time (25 ℃) | Tr + Tf |        | 20      |     | us                |

| Brightness           |         | 80     | 100     |     | cd/m <sup>2</sup> |

| Contrast Ratio       | CR      |        | 2,000:1 |     |                   |

| Lifetime             |         | 10,000 |         |     | Hrs               |

## 7 Timing Characteristics

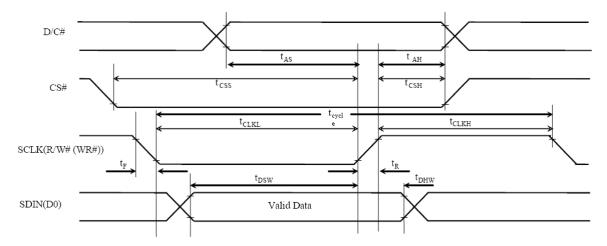

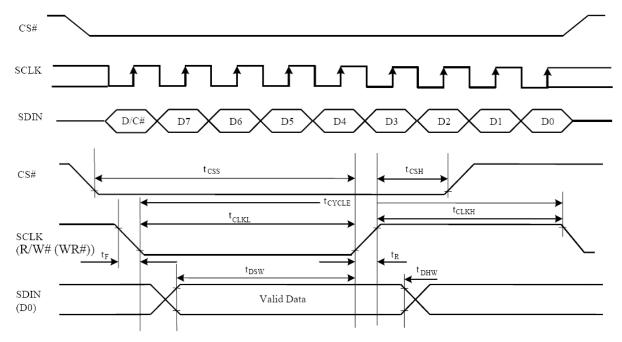

### 7.1 Serial Interface Timing Characteristics: (4-wire SPI)

| Symbol             | Item                   | Min | Тур | Max | Unit |

|--------------------|------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 50  | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 15  |     |     | ns   |

| $t_{AH}$           | Address Hold Time      | 15  | -   | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 20  | -   | -   | ns   |

| $t_{CSH}$          | Chip Select Hold Time  | 10  | -   | -   | ns   |

| $t_{DSW}$          | Write Data Setup Time  | 15  | -   | -   | ns   |

| $t_{DHW}$          | Write Data Hold Time   | 15  | -   |     | ns   |

| $t_{CLKL}$         | Clock Low Time         | 20  | -   |     | ns   |

| $t_{CLKH}$         | Clock High Time        | 20  |     |     | ns   |

| $t_R$              | Rise Time              | -   |     | 15  | ns   |

| $t_{\mathrm{F}}$   | Fall Time              | -   |     | 15  | ns   |

V<sub>DD</sub>-V<sub>SS</sub> =2.4V to 2.6V, V<sub>DDIO</sub>=1.65V, V<sub>CI</sub>=2.8V, Ta=25 °C

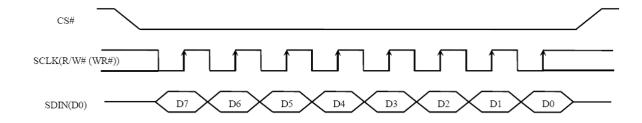

#### 7.2 Serial Interface Timing Characteristics: (3-wire SPI)

| Symbol             | Item                   | Min | Тур | Max | Unit |

|--------------------|------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 50  | -   | -   | ns   |

| $t_{CSS}$          | Chip Select Setup Time | 20  | -   | -   | ns   |

| $t_{CSH}$          | Chip Select Hold Time  | 10  | -   | -   | ns   |

| $t_{ m DSW}$       | Write Data Setup Time  | 15  | -   | -   | ns   |

| $t_{ m DHW}$       | Write Data Hold Time   | 15  | -   |     | ns   |

| $t_{CLKL}$         | Clock Low Time         | 20  | -   |     | ns   |

| $t_{CLKH}$         | Clock High Time        | 20  |     |     | ns   |

| $t_R$              | Rise Time              | -   |     | 15  | ns   |

| $t_{\mathrm{F}}$   | Fall Time              | =   |     | 15  | ns   |

$\overline{V}_{DD}$ - $V_{SS}$  =2.4V to 2.6V,  $V_{DDIO}$ =1.65V,  $V_{CI}$ =2.8V, Ta=25 °C

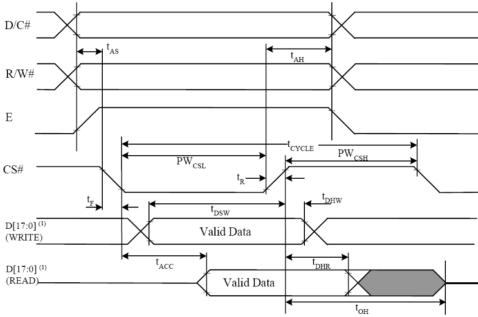

#### 7.3 68XX-Seriel MPU Parallel Interface Timing Characteristics

| Symbol             | Description                          | Min | Max | Unit |

|--------------------|--------------------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 10  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -   | ns   |

| $t_{ m DSW}$       | Write Data Setup Time                | 40  | -   | ns   |

| $t_{ m DHW}$       | Write Data Hold Time                 | 7   | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | _   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                          | _   | 140 | ns   |

| DW                 | Chip Select Low Pulse Width (Read)   | 120 |     | ***  |

| $PW_{CSL}$         | Chip Select Low Pulse Width (Write)  | 60  | _   | ns   |

| DW                 | Chip Select High Pulse Width (Read)  | 60  |     | ***  |

| $PW_{CSH}$         | Chip Select High Pulse Width (Write) | 60  | _   | ns   |

| t                  | Rise Time                            | _   | 15  | ns   |

| t <sub>F</sub>     | Fall Time                            | _   | 15  | ns   |

<sup>\*</sup>  $(V_{DD} - V_{SS} = 2.4V \text{ to } 2.6V, V_{DDIO} = 1.65V, V_{CI} = 2.8V, T_a = 25^{\circ}C)$

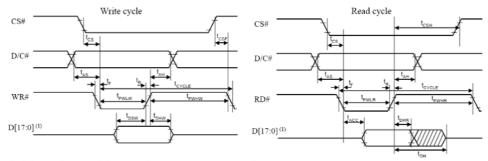

#### 7.4 80XX-Seriel MPU Parallel Interface Timing Characteristics

| Symbol             | Description                          | Min | Max | Unit |

|--------------------|--------------------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | ns   |

| $t_{AS}$           | Address Setup Time                   | 10  | -   | ns   |

| $t_{AH}$           | Address Hold Time                    | 0   | _   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                | 40  | -   | ns   |

| $t_{ m DHW}$       | Write Data Hold Time                 | 7   | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | _   | 70  | ns   |

| $t_{ACC}$          | Access Time                          | _   | 140 | ns   |

| $t_{PWLR}$         | Read Low Time                        | 150 | -   | ns   |

| t <sub>PWLW</sub>  | Write Low Time                       | 60  | _   | ns   |

| t <sub>PWHR</sub>  | Read High Time                       | 60  | -   | ns   |

| t <sub>PWHW</sub>  | Write High Time                      | 60  | -   | ns   |

| $t_{CS}$           | Chip Select Setup Time               | 0   | _   | ns   |

| CSH                | Chip Select Hold Time to Read Signal | 0   | _   | ns   |

| $t_{CSF}$          | Chip Select Hold Time                | 20  | -   | ns   |

| t <sub>R</sub>     | Rise Time                            | _   | 15  | ns   |

| $t_{\mathrm{F}}$   | Fall Time                            | _   | 15  | ns   |

<sup>\*</sup>  $(V_{DD} - V_{SS} = 2.4 \text{V to } 2.6 \text{V}, V_{DDIO} = 1.65 \text{V}, V_{CI} = 2.8 \text{V}, T_a = 25 ^{\circ}\text{C})$

\* (1) When 8-bit Used: D[7:0] Instead

### 8 Functional Specification

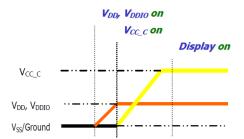

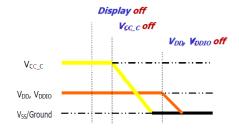

#### 8.1 Power down and Power up Sequence

To protect OEL panel and extend the panel life time, the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. It gives the OEL panel enough time to complete the action of charge and discharge before/after the operation.

#### 8.1.1 Power up Sequence

- 1. Power up  $V_{DD} \& V_{DDIO}$

- 2. Send Display off command

- 3. Initialization

- 4. Clear Screen

- 5. Power up  $V_{CC}$

- 6. Delay 100ms(When V<sub>CC</sub> is stable)

- 7. Send Display on command

- 1. Send Display off command

- 2. Power down V<sub>CC</sub>

- 3. Delay 100ms (When V<sub>CC</sub> is reach 0 and panel is completely discharges)

- 4. Power down V<sub>DD</sub> &V<sub>DDIO</sub>

#### 8.2 Reset Circuit

When RES# input is low, the chip is initialized with the following status:

- 1. Display is OFF

- 2. 128(RGB) x 128 Display Mode

- 3. Normal segment and display data column and row address mapping (SEG0 mapped to column address 00h and COM0 mapped to row address 00h)

- 4. Display start line is set at display RAM address 0

- 5. Column address counter is set at 0

- 6. Normal scan direction of the COM outputs

- 7. Command A2h, B1h, B3h, BBh, BEh are locked by command FDh

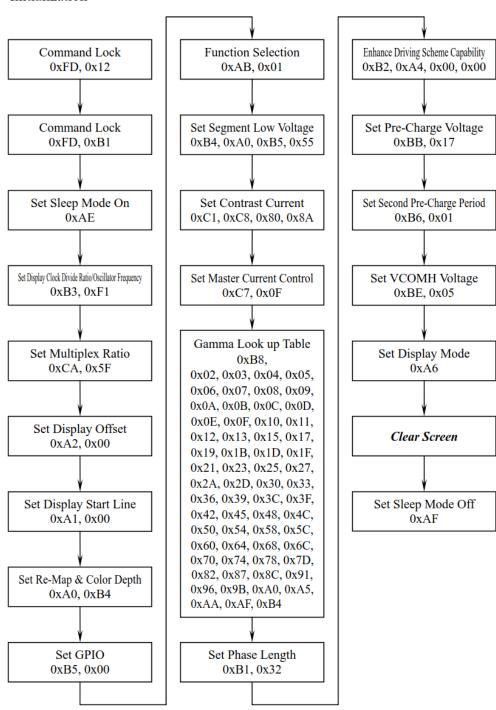

### 9 Actual Application Example

<Initialization>

If the noise is accidentally occurred at the displaying window during the operation, please reset the display in order to recover the display function.

### 10 Reliability

| Test Item                | Content of Test                              | Test Condition     | Note |

|--------------------------|----------------------------------------------|--------------------|------|

| High Temperature Storage | Endurance test applying the high storage     | 80°C               | 2    |

|                          | temperature for a long time.                 | 200hrs             | 2    |

| Low Temperature Storage  | Endurance test applying the high storage     | -40°C              | 1,2  |

|                          | temperature for a long time.                 | 200hrs             | 1,2  |

| High Temperature         | Endurance test applying the electric stress  | 70°C               |      |

| Operation                | (Voltage & Current) and the thermal stress   | 200hrs             | -    |

|                          | to the element for a long time.              |                    |      |

| Low Temperature          | Endurance test applying the electric stress  | -30 °C             | 1    |

| Operation                | under low temperature for a long time.       | 200hrs             | 1    |

| High Temperature/        | The module should be allowed to stand at     | 60°C,90%RH         |      |

| Humidity Operation       | 60°C,90%RH max, for 96hrs under no-load      | 96hrs              |      |

|                          | condition excluding the polarizer. Then      |                    | 1,2  |

|                          | taking it out and drying it at normal        |                    |      |

|                          | temperature.                                 |                    |      |

| Thermal Shock Resistance | The sample should be allowed stand the       | -30°C/70°C         |      |

|                          | following 10 cycles of operation             | 10 cycles          |      |

|                          | -30°C 25°C 70°C√                             |                    |      |

|                          |                                              |                    | -    |

|                          | 30min 5min 30min⊌                            |                    |      |

|                          | 1 cycle₽                                     |                    |      |

| Vibration Test           | Endurance test applying the vibration during | Total fixed        |      |

|                          | transportation and using                     | amplitude:         |      |

|                          |                                              | 15mm; Vibration:   |      |

|                          |                                              | 10~55Hz;           |      |

|                          |                                              | One cycle 60       | 3    |

|                          |                                              | seconds to 3       |      |

|                          |                                              | directions of X,   |      |

|                          |                                              | Y, Z, for each 16  |      |

|                          |                                              | minutes.           |      |

| Static Electricity Test  | Endurance test apply the electric stress to  | VS=800V,           |      |

|                          | the terminal.                                | RS=1.5k $\Omega$ , |      |

|                          |                                              | CS=100pF,          | _    |

|                          |                                              | 1 time.            |      |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal. Temperature and humidity after remove from the rest chamber.

Note3: Test performed on product itself, not inside a container.

### 11 Warranty and Conditions

http://www.displaymodule.com/pages/faq HYPERLINK

"http://www.displaymodule.com/pages/faq"