# DM-OLED32-648 Monochrome Graphic OLED Display Panel-SPI,MCU

### Contents

- 1 Revision History

- 2 Main Features

- 3 Pin Description

- 4 Mechanical Drawing

- 5 Absolute Maximum Ratings

- 6 Electrical Characteristics

- 7 MCU Interface

- 7.1 MCU Parallel 6800-series Interface

- 7.2 MCU Parallel 8080-series Interface

- 7.3 MCU Serial Interface (4-wire SPI)

- 7.4 MCU Serial Interface (3-wire SPI)

- 8 Block Diagram

- 9 Application Reference

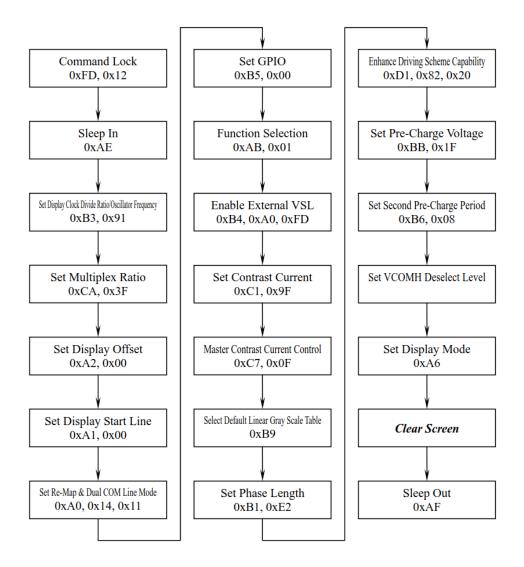

- 10 Initialization flow

- 11 Example Initialization Code

- 12 Reliability

- 13 Warranty and Conditions

# 1 Revision History

|                          | <u> </u> |

|--------------------------|----------|

| 2019-05-31 First release |          |

# 2 Main Features

| Item           | Specification                                | Unit  |

|----------------|----------------------------------------------|-------|

| Diagonal Size  | 3.2                                          | inch  |

| Display Mode   | OLED                                         | -     |

| Display Colors | Monochrome White/Yellow/Blue/Green           |       |

| Resolution     | 256 x 64                                     | pixel |

| Controller IC  | SSD1322                                      | -     |

| Duty           | 1/64                                         |       |

| Interface      | 8-Bit 6800/8080 Parallel 3/4-Wire Serial SPI |       |

| Power Supply   | 3.3V/5V                                      | V     |

| Viewing Area   | 78.78 x 21.18                                | mm    |

| Weight         | 9.95                                         | g     |

# 3 Pin Description

| Pin No. | Symbol   | Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          | Reserved Pin(Supporting Pin)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1       | N.C(GND) | The supporting pins can reduce the influences from stresses on the function pins. These pins must be connected to external ground.                                                                                                                                                                                                                                                                                                                                    |

|         |          | Ground of Logic Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2       | VSS      | This is a ground pin. It also acts as a reference for the logic pins. It must be connected to external ground.                                                                                                                                                                                                                                                                                                                                                        |

|         |          | Power supply for OEL Panel                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3       | VCC      | These are the most positive voltage supply pin of the chip. They must be connected to external source.                                                                                                                                                                                                                                                                                                                                                                |

|         |          | Voltage Output High Level for COM Signal                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4       | VCOMH    | This pin is the input pin for the voltage output high level for COM signals.<br>A tantalum capacitor should be connected between this pin and VSS.                                                                                                                                                                                                                                                                                                                    |

|         |          | Ground of Analog Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5       | VLSS     | These are the analog ground pins. They should be connected to VSS externally.                                                                                                                                                                                                                                                                                                                                                                                         |

|         |          | Host Data Input/ Output Bus                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6-13    | D7-D0    | These pins are 8-bit bi-directional data bus to be connected to the microprocessor's data bus. When serial mode is selected, D1 will be the serial data input SDIN and D0 will be the serial clock input SCLK.                                                                                                                                                                                                                                                        |

|         |          | Unused pins must be connected to VSS except for D2 in serial mode.                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |          | Read/Write Enable or Read                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14      | E/RD#    | This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled high and the CS# is pulled low. When connecting to an 80XX-microprocessor, this pin receives the Read (RD#) signal. Data read operation is initiated when this pin is pulled low and CS# is pulled low. When serial mode is selected, this pin must be connected to VSS. |

|         |          | Read/Write Select or Write                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15      | R/W#     | This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as Read/Write (R/W#) selection input. Pull this pin to "High" for read mode and pull it to "Low" for write mode. When 80XX interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled low and the CS# is pulled low. When serial mode is selected, this pin must                          |

|       |       | be connected to VSS.                                                                                                                                                                                                                                                                                                                                     |                         |                              |  |  |  |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------|--|--|--|

|       |       | Communicating Protocol Select                                                                                                                                                                                                                                                                                                                            |                         |                              |  |  |  |

|       | BS0   | These pin are MCU interface selection input. See the following table:                                                                                                                                                                                                                                                                                    |                         |                              |  |  |  |

| 16-17 | BS1   | 3-wire SPI<br>4-wire SPI<br>8-bit 68XX Parallel<br>8-bit 80XX Parallel                                                                                                                                                                                                                                                                                   | BS0<br>1<br>0<br>1<br>0 | BS1<br>0<br>0<br>1<br>1<br>1 |  |  |  |

| 18    | D/C#  | Data/Command Control<br>This pin is Data/Command control pin. When the pin is pulled high, the<br>input at D7~D0 is treated as display data. When the pin is pulled low, the<br>input at D7~D0 will be transferred to the command register. For detail<br>relationship to MCU interface signals, please refer to the Timing<br>Characteristics Diagrams. |                         |                              |  |  |  |

| 19    | CS#   | Chip Select<br>This pin is the chip select input. The chip is enabled for MCU<br>communication only when CS# is pulled low.                                                                                                                                                                                                                              |                         |                              |  |  |  |

| 20    | RES#  | Power Reset for Controller and Driver<br>This pin is reset signal input. When the pin is low, initialization of the chip<br>is executed.                                                                                                                                                                                                                 |                         |                              |  |  |  |

| 21    | FR    | Cascade Application Connection Pin<br>This pin is No Connection pins. Nothing should be connected to this pin. It<br>should be left open individually                                                                                                                                                                                                    |                         |                              |  |  |  |

| 22    | IREF  | Current Reference for Brightness Adjustment   This pin is segment current reference pin. A resistor should be connected between this pin and VSS. Set the current lower than 10uA                                                                                                                                                                        |                         |                              |  |  |  |

| 23    | N.C   | Reserved Pin<br>No connection                                                                                                                                                                                                                                                                                                                            |                         |                              |  |  |  |

| 24    | VDDIO | Power Supply for I/O Pin<br>This pin is a power supply pin of I/O buffer. It should be connected to<br>VDD or external source. All I/O signal should have VIH reference to<br>VDDIO. When I/O signal pins (BS0~BS1, D0~D7, control signals…) pull<br>high, they should be connected to VDDIO.                                                            |                         |                              |  |  |  |

| 25    | VDD   | Power Supply for Core Logic CircuitThis is a voltage supply pin. It can be supplied externally (within the range<br>of 2.4~2.6V) or regulated internally from VCI. A capacitor should be<br>connected between this pin & VSS under all circumstances.                                                                                                    |                         |                              |  |  |  |

|       | VCI   | Power Supply for Operation                                                                                                                                                                                                                                                                                                                               |                         |                              |  |  |  |

|    |          | This is a voltage supply pin. It must be connected to external source & always be equal to or higher than VDD & VDDIO.                                                                                                                     |

|----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27 | VSL      | Voltage Output Low Level for SEG Signal<br>This is segment voltage reference pin. When external VSL is not used, this<br>pin should be left open. When external VSL is used, this pin should<br>connect with resistor and diode to ground. |

| 28 | VLSS     | Ground of Analog Circuit<br>These are the analog ground pins. They should be connected to VSS<br>externally.                                                                                                                               |

| 29 | VCC      | Power supply for OEL Panel<br>These are the most positive voltage supply pin of the chip. They must be<br>connected to external source.                                                                                                    |

| 30 | N.C(GND) | Reserved Pin(Supporting Pin)<br>The supporting pins can reduce the influences from stresses on the<br>function pins. These pins must be connected to external ground.                                                                      |

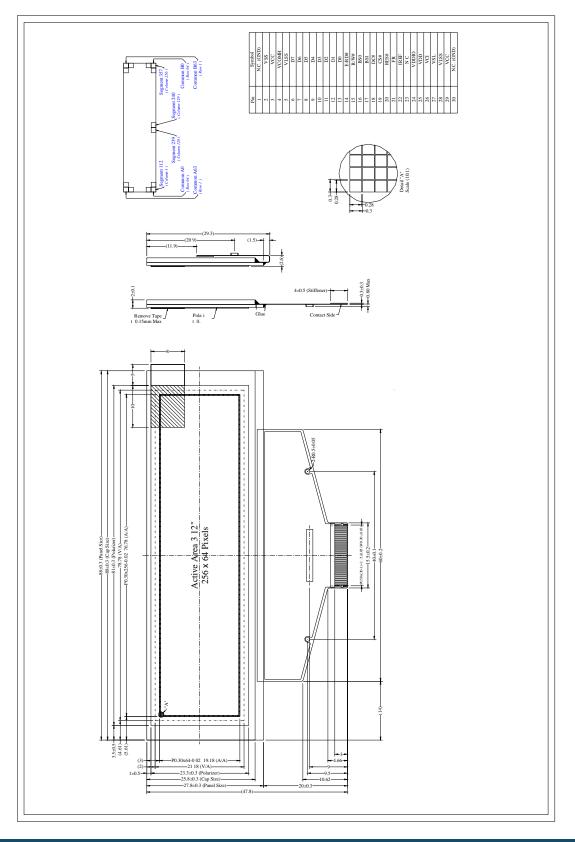

# 4 Mechanical Drawing

Copyright © 2019

## 5 Absolute Maximum Ratings

| Parameter                    | Symbol | Min  | Max  | Unit | Notes |

|------------------------------|--------|------|------|------|-------|

| Supply Voltage for Operation | Vci    | -0.3 | 4    | V    | 1,2   |

| Supply Voltage for Logic     | Vdd    | -0.5 | 2.75 | V    | 1,2   |

| Supply Voltage for I/O Pins  | Vddio  | -0.5 | Vci  | V    | 1,2   |

| Supply Voltage for Display   | Vcc    | -0.5 | 16   | V    | 1,2   |

| Operating Current for Vcc    | Icc    | -    | 55   | mA   | 1,2   |

| Operating Temperature        | Тор    | -30  | 85   | °C   |       |

| Storage Temperature          | Tstg   | -40  | 90   | °C   |       |

Note1:All above voltage are on the basis of "VSS=0V".

Note2: When this module is used beyond the above absolute maximum ratings, permanent breakage of the module may occur. Also, for normal operations, it is desirable to use this module under the conditions according to the "Electrical Characteristics". If this module is used beyond these conditions, malfunctioning of the module can occur and the reliability of the module may deteriorate.

### 6 Electrical Characteristics

#### 6.1 DC Characteristics

| Item                         | Symbol          | Condition   | Min       | Тур. | Max       | Unit |

|------------------------------|-----------------|-------------|-----------|------|-----------|------|

| Supply Voltage for Operation | Vci             |             | 2.4       | 2.8  | 3.5       | V    |

| Supply Voltage for Logic     | $V_{DD}$        |             | 2.4       | 2.5  | 2.6       | V    |

| Supply Voltage for I/O Pins  | Vddio           |             | 1.65      | 1.8  | VCI       | V    |

| Supply Voltage for Display   | Vcc             | Note1       | 11.5      | 12.0 | 12.5      | V    |

| Low Level Input Voltage      | V <sub>IL</sub> |             | 0         | -    | 0.2 Vddio | V    |

| High Level Input Voltage     | V <sub>IH</sub> |             | 0.8 Vddio | -    | Vddio     | V    |

| Low Level Output Voltage     | V <sub>OL</sub> | Iout=100uA, | 0         |      | 0.1 Vddio | V    |

|                              |                 | 3.3MHz      |           |      |           |      |

| High Level Output Voltage    | V <sub>OH</sub> | Iout=100uA, | 0.9 Vddio |      | Vddio     | V    |

|                              |                 | 3.3MHz      |           |      |           |      |

| Operating Current for VCI    | Ісі             | Note2       | -         | 1.8  | 2.25      | mA   |

|                              |                 | Note3       |           | 1.8  | 2.25      | mA   |

| Operating Current for Vcc    | Icc             | Note2       | -         | 25.5 | 31.9      | mA   |

|                              |                 | Note3       |           | 40.1 | 51.1      | mA   |

| Sleep Mode Current for VCI   | ICI,SLEEP       |             | -         | 1    | 5         | uA   |

| Sleep Mode Current for Vcc   | ICC,SLEEP       |             | -         | 1    | 5         | uA   |

Note1 : Brightness (Lbr) and Supply Voltage for Display (Vcc) are subject to the change of the panel characteristics and the customer's request.

Note2:  $V_{CI} = 2.8V$ ,  $V_{CC} = 12V$ , 50% Display Area Turn on.

Note3:  $V_{CI} = 2.8V$ ,  $V_{CC} = 12V$ , 100% Display Area Turn on.

#### **6.2 Optical Characteristics**

| Item               | Symbol          | Min       | Тур     | Max  | Unit              |

|--------------------|-----------------|-----------|---------|------|-------------------|

| View Angles Left   |                 |           | 80      |      | 0                 |

| View Angles Right  |                 |           | 80      |      | 0                 |

| View Angles Top    |                 |           | 80      |      | 0                 |

| View Angles Bottom |                 |           | 80      |      | 0                 |

| C.I.E(Yellow)      | (x)             | Without   | 0.44    | 0.48 | 0.52              |

|                    | (y)             | Polarizer | 0.46    | 0.50 | 0.54              |

| Contrast Ratio     | CR              |           | >2000:1 |      |                   |

| Brightness         | L <sub>br</sub> | 60        | 80      |      | cd/m <sup>2</sup> |

Note: Optical measurement taken at  $V_{CI} = 2.8V$ ,  $V_{CC} = 12V$

# 7 MCU Interface

MCU interface assignment under different bus interface mode

| Bus Interface | Data/Command Interface |      |      | Control Signal |        |      |     |         |      |

|---------------|------------------------|------|------|----------------|--------|------|-----|---------|------|

|               | D7 D6 D5 D4 D3         | 3 D2 | D1   | D0             | E      | R/W# | CS# | D/C#    | RES# |

| 8-bit 8080    | D[                     | 7:0] |      |                | RD#    | WR#  | CS# | D/C#    | RES# |

| 8-bit 6800    | D[                     | 7:0] |      |                | Е      | R/W# | CS# | D/C#    | RES# |

| 3-wire SPI    | Tie LOW                | NC   | SDIN | SCLK           | Tie LO | OW   | CS# | Tie LOW | RES# |

| 4-wire SPI    | Tie LOW                | NC   | SDIN | SCLK           | TieLO  | W    | CS# | D/C#    | RES# |

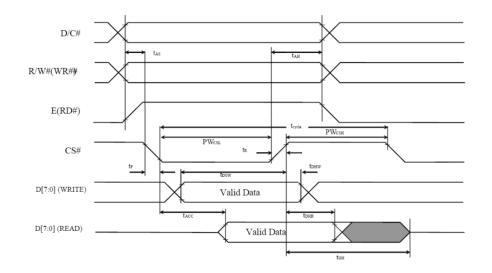

#### 7.1 MCU Parallel 6800-series Interface

The parallel interface consists of 8 bi-directional data pins (D[7:0]), R/W#, D/C#, E and CS#.

A LOW in R/W# indicates WRITE operation and HIGH in R/W# indicates READ operation.

A LOW in D/C# indicates COMMAND read/write and HIGH in D/C# indicates DATA read/write.

The E input serves as data latch signal while CS# is LOW. Data is latched at the falling edge of E signal.

| Function      | Е            | R/W# | CS# | D/C# |

|---------------|--------------|------|-----|------|

| Write command | $\downarrow$ | L    | L   | L    |

| Read status   | $\downarrow$ | Н    | L   | L    |

| Write data    | $\downarrow$ | L    | L   | Н    |

| Read data     | $\downarrow$ | Н    | L   | Н    |

Note: ↓stands for falling edge of signal

H stands for HIGH in signal

L stands for LOW in signal

| Symbol             | Description                          | Min | Max | Unit |

|--------------------|--------------------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 10  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                | 40  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                 | 7   | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | -   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                          | -   | 140 | ns   |

| DW                 | Chip Select Low Pulse Width (Read)   | 120 |     |      |

| PW <sub>CSL</sub>  | Chip Select Low Pulse Width (Write)  | 60  | -   | ns   |

| DW                 | Chip Select High Pulse Width (Read)  | 60  |     |      |

| PW <sub>CSH</sub>  | Chip Select High Pulse Width (Write) | 60  | -   | ns   |

| t <sub>R</sub>     | Rise Time                            | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time                            |     | 15  | ns   |

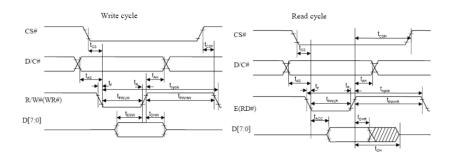

#### 7.2 MCU Parallel 8080-series Interface

The parallel interface consists of 8 bi-directional data pins (D[7:0]), RD#, WR#, D/C# and CS#.

A LOW in D/C# indicates COMMAND read/write and HIGH in D/C# indicates DATA read/write. A rising edge of RD# input serves as a data READ latch signal while CS# is kept LOW.

A rising edge of WR# input serves as a data/command WRITE latch signal while CS# is kept LOW.

| Function      | RD#        | WR# | CS# | D/C# |

|---------------|------------|-----|-----|------|

| Write command | Н          | ↑   | L   | L    |

| Read status   | ↑          | Н   | L   | L    |

| Write data    | Н          | ↑   | L   | Н    |

| Read data     | $\uparrow$ | Н   | L   | Н    |

Note: ↑ stands for rising edge of signal

L stands for LOW in signal

| Symbol             | Description                          | Min | Max | Unit |

|--------------------|--------------------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 10  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                | 40  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                 | 7   | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | -   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                          | -   | 140 | ns   |

| t <sub>PWLR</sub>  | Read Low Time                        | 150 | -   | ns   |

| t <sub>PWLW</sub>  | Write Low Time                       | 60  | -   | ns   |

| t <sub>PWHR</sub>  | Read High Time                       | 60  | -   | ns   |

| t <sub>PWHW</sub>  | Write High Time                      | 60  | -   | ns   |

| t <sub>CS</sub>    | Chip Select Setup Time               | 0   | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time to Read Signal | 0   | -   | ns   |

| t <sub>CSF</sub>   | Chip Select Hold Time                | 20  | -   | ns   |

| t <sub>R</sub>     | Rise Time                            |     | 15  | ns   |

| t <sub>F</sub>     | Fall Time                            | -   | 15  | ns   |

H stands for HIGH in signal

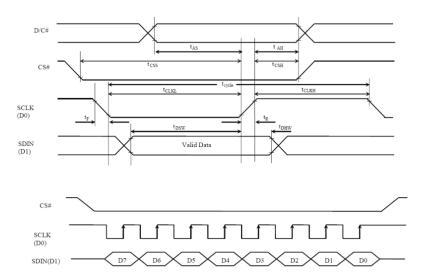

#### 7.3 MCU Serial Interface (4-wire SPI)

The serial interface consists of serial clock SCLK, serial data SDIN, D/C#, CS#. In SPI mode, D0 acts as SCLK, D1 acts as SDIN. For the unused data pins, D2 should be left open. The pins from D3 to D7, E and R/W# can be connected to an external ground.

| Function      | E(RD#)  | R/W#(WR#) | CS# | DC# | D0#        |

|---------------|---------|-----------|-----|-----|------------|

| Write command | Tie LOW | Tie LOW   | L   | L   | $\uparrow$ |

| Write data    | Tie LOW | Tie LOW   | L   | Н   | ↑          |

Note: H stands for HIGH in signal

L stands for LOW in signal

| Symbol             | Description            | Min | Max | Unit |

|--------------------|------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 100 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 15  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 15  | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 20  | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 10  | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time  | 15  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time   | 15  | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 20  | -   | ns   |

| t <sub>CLKH</sub>  | Clock High Time        | 20  | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time              | -   | 15  | ns   |

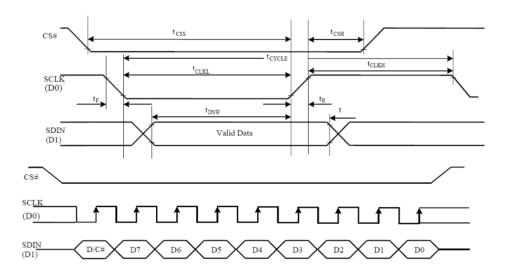

#### 7.4 MCU Serial Interface (3-wire SPI)

The 3-wire serial interface consists of serial clock SCLK, serial data SDIN and CS#. In 3-wire SPI mode, D0 acts as SCLK, D1 acts as SDIN. For the unused data pins, D2 should be left open. The pins from D3 to D7, R/W# (WR#), E(RD#) and D/C# can be connected to an external ground.

|                                 | Function      | E(RD#)  | R/W#(WR#) | CS# | D/C#    | D0         |

|---------------------------------|---------------|---------|-----------|-----|---------|------------|

|                                 | Write command | Tie LOW | Tie LOW   | L   | Tie LOW | $\uparrow$ |

|                                 | Write data    | Tie LOW | Tie LOW   | L   | Tie LOW | $\uparrow$ |

| Note: Letende for LOW in signal |               |         |           |     |         |            |

Note: L stands for LOW in signal

| Symbol             | Description            | Min | Max | Unit |

|--------------------|------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 100 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 15  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 15  | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 20  | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 10  | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time  | 15  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time   | 15  | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 20  | -   | ns   |

| t <sub>CLKH</sub>  | Clock High Time        | 20  | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time              | -   | 15  | ns   |

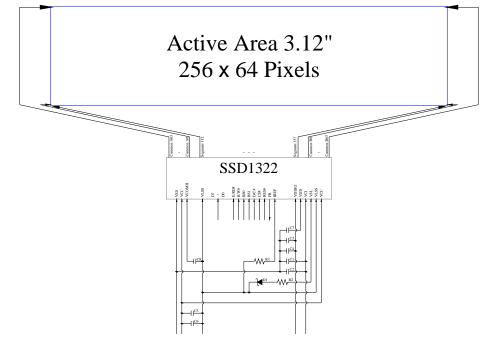

### 8 Block Diagram

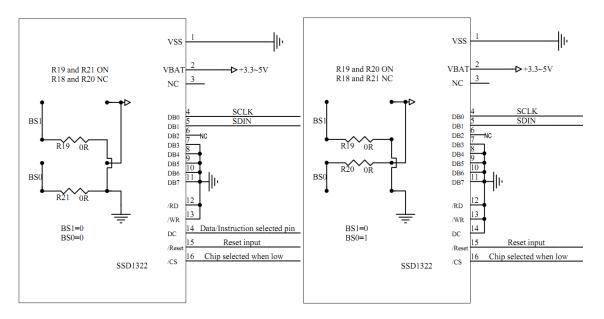

MCU Interface Selection: BS0 and BS1 Pins connected to MCU interface: D7~D0, E/RD#, R/W#, D/C#, CS#, and RES#

C1, C3, C5: 0.1µF

- C2, C4: 4.7µF

- C6: 10µF

- C7: 1μF

- C8: 4.7uF / 25V Tantalum Capacitor

- R1:  $680k\Omega$ , R1 = (Voltage at IREF VSS) / IREF

- R2: 50Ω, 1/4W

- D1: ≤1.4V, 0.5W

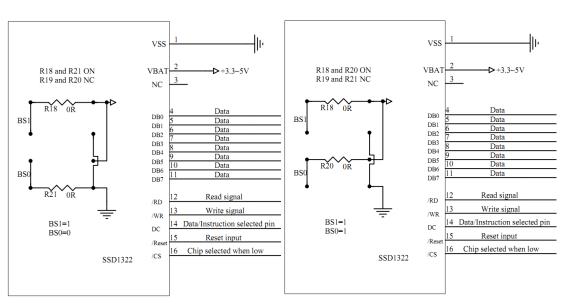

# 9 Application Reference

The Parallel (8080 Series MCU)Reference Example

The Parallel (6800 Series MCU)Reference Example

The Serial 3 Line SPI Reference Example

# 10 Initialization flow

If the noise is accidentally occurred at the displaying window during the operation, please reset the display in order to recover the display function.

### 11 Example Initialization Code

void Write\_Data(unsigned char dat) RS=1; CS=0; \_RW=0; DATA\_BUS=dat; Delayms(2); \_RW=1; CS=1;} void Write\_Instruction(unsigned char cmd) { RS=0; CS=0; \_RW=0; DATA\_BUS=cmd; Delayms(2); RW=1; CS=1;} void LCD\_initialize(void) { RES=1; Delayms(200); RES=0; Delayms(200); RES=1; Delayms(200); /\*SET COMMAND LOCK \*/ Write\_Instruction(0xFD); Write\_Data(0x12); /\* UNLOCK \*/ /\*DISPLAY OFF\*/ Write\_Instruction(0xAE); Write\_Instruction(0xB3); /\*DISPLAYDIVIDE CLOCKRADIO/OSCILLATAR FREQUANCY\*/ Write\_Data(0x91); Write\_Instruction(0xCA); /\*multiplex ratio\*/ Write\_Data(0x3F); /\*duty = 1/64\*/ Write\_Instruction(0xA2); /\*set offset\*/ Write\_Data(0x00); Write\_Instruction(0xA1); /\*start line\*/ Write\_Data(0x00); Write\_Instruction(0xA0); /\*set remap\*/ Write\_Data(0x14); Write\_Data(0x11); Write\_Instruction(0xAB); /\*funtion selection\*/ Write\_Data(0x01); /\* selection external vdd \*/ Write\_Instruction(0xB4); Write\_Data(0xA0); Write\_Data(0xFD); Write\_Instruction(0xC1); /\*set contrast current \*/ Write\_Data(Contrast\_level); Write\_Instruction(0xC7); /\*master contrast current control\*/ Write\_Data(0x0F); Wriite\_Instruction(0xB1); /\*SET PHASE LENGTH\*/ Write\_Data(0xE2); Write\_Instruction(0xD1); Write\_Data(0x82); Write\_Data(0x20); Write\_Instruction(0xBB); /\*SET PRE-CHANGE VOLTAGE\*/ Write\_Data(0x1F); Write\_Instruction(0xB6); /\*SET SECOND PRE-CHARGE PERIOD\*/ Write\_Data(0x08); Write\_Instruction(0xBE); /\* SET VCOMH \*/ Write\_Data(0x07); Write\_Instruction(0xA6); /\*normal display\*/ Clear\_ram(); Write\_Instruction(0xAF); /\*display ON\*/

}

# 12 Reliability

| Test Item                | Content of Test                             | Test Condition                                         | Note |

|--------------------------|---------------------------------------------|--------------------------------------------------------|------|

| High Temperature Storage | Endurance test applying the high storage    | 80°C                                                   | 2    |

|                          | temperature for a long time.                | 200hrs                                                 | 2    |

| Low Temperature Storage  | Endurance test applying the high storage    | -30°C                                                  | 1,2  |

|                          | temperature for a long time.                | 200hrs                                                 | 1,2  |

| High Temperature         | Endurance test applying the electric stress | 70°C                                                   |      |

| Operation                | (Voltage & Current) and the thermal         | 200hrs                                                 | -    |

|                          | stress to the element for a long time.      |                                                        |      |

| Low Temperature          | Endurance test applying the electric stress | -20 °C                                                 | 1    |

| Operation                | under low temperature for a long time.      | 200hrs                                                 | 1    |

| High Temperature/        | The module should be allowed to stand at    | 60°C,90%RH                                             |      |

| Humidity Operation       | 60°C,90%RH max, for 96hrs under no-         | 96hrs                                                  |      |

|                          | load condition excluding the polarizer.     |                                                        | 1,2  |

|                          | Then taking it out and drying it at normal  |                                                        |      |

|                          | temperature.                                |                                                        |      |

| Thermal Shock Resistance | The sample should be allowed stand the      | -30°C/85°C                                             |      |

|                          | following 10 cycles of operation            | 10 cycles                                              |      |

|                          | -30°C 25°C 85°C₊/                           |                                                        |      |

|                          |                                             |                                                        | -    |

|                          | 30min 5min 30min                            |                                                        |      |

|                          | 1 cycle                                     |                                                        |      |

| Vibration Test           | Endurance test applying the vibration       | Total fixed                                            |      |

| violation rest           | during transportation and using             | amplitude: 15mm;                                       |      |

|                          | during transportation and using             | Vibration:                                             |      |

|                          |                                             | 10~55Hz;                                               |      |

|                          |                                             | One cycle 60                                           | 3    |

|                          |                                             | seconds to 3                                           | 5    |

|                          |                                             | directions of X, Y,                                    |      |

|                          |                                             | Z, for each 16                                         |      |

|                          |                                             | minutes.                                               |      |

| Static Electricity Test  | Endurance test apply the electric stress to | VS=800V,                                               |      |

| Suite Dicetiony Test     |                                             |                                                        |      |

|                          |                                             |                                                        | -    |

|                          |                                             |                                                        |      |

| Static Electricity Test  | the terminal.                               | VS=800V,<br>RS=1.5k <b>Ω</b> ,<br>CS=100pF,<br>1 time. | -    |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal. Temperature and humidity after remove from the rest chamber.

Note3: The packing have to including into the vibration testing.

### 13 Warranty and Conditions

http://www.displaymodule.com/pages/faq