# DM-OLED2004-611 2004 YELLOW CHARACTER OLED DISPLAY WITH PARALLEL OR SERIAL MPU INTERFACE

## Contents

<u>Revision History</u>

<u>Main Features</u>

Pin Description

Parallel interface(Default):

Serial Interface:

Jumper Selections

Mechanical Drawing

Electrical Characteristics

Optical Characteristics

MPU Interface

68 series Interface

80-Series Interface

Serial Interface

Table of Commands

Instruction Description

Initialization by Instruction

Character Generator ROM (CGROM)

Driver/Controller Information

<u>Reliability</u>

Warranty and Conditions

# 1 Revision History

| Date       | Changes                |

|------------|------------------------|

| 2015-03-13 | First release          |

| 2015-12-24 | Pin Description Update |

# 2 Main Features

| Item                 | Specification                                               | Unit |

|----------------------|-------------------------------------------------------------|------|

| Number of Characters | 20 characters x 4 lines                                     |      |

| Display Mode         | Passive Matrix                                              | -    |

| Display Colors       | Yellow                                                      |      |

| Interface            | Parallel or serial MPU interface(default 6800 MPU parallel) | -    |

| Controller IC        | WS0010                                                      | -    |

| Power Supply         | 3.0 or 5.0                                                  | V    |

| Module Dimension     | 98.0 x 60.0 x 10.0                                          | mm   |

| Duty                 | 1/16 duty                                                   | -    |

| Weight               | 41.6                                                        | g    |

# 3 Pin Description

### 3.1 Parallel interface(Default):

| Pin No. | Symbol  | Function Description                                                                                      |

|---------|---------|-----------------------------------------------------------------------------------------------------------|

| 1       | VSS     | Ground                                                                                                    |

| 2       | VDD     | Supply Voltage for OLED and logic                                                                         |

| 3       | NC      | No Connect                                                                                                |

| 4       | RS      | H: DATA, L:Instruction code                                                                               |

| 5       | R/W     | H: Read(MPU←Module) L:Write(MPU→Module)                                                                   |

| 6       | E       | Chip enable signal                                                                                        |

| 7-10    | DB0-DB3 | Four low order bi-directional three-state data bus lines. These four are not used during 4-bit operation. |

| 11-14   | DB4-DB7 | Four high order bi-directional three-state data bus lines.                                                |

| 15      | NC      | No Connect                                                                                                |

| 16      | NC      | No Connect                                                                                                |

### 3.2 Serial Interface:

| Pin No. | Symbol | Function Description              |  |  |  |  |

|---------|--------|-----------------------------------|--|--|--|--|

| 1       | VSS    | Ground                            |  |  |  |  |

| 2       | VDD    | Supply Voltage for OLED and logic |  |  |  |  |

| 3-11    | NC     | No Connect                        |  |  |  |  |

| 12      | SCL    | Serial Clock signal               |  |  |  |  |

| 13      | SDO    | Serial Data output signal         |  |  |  |  |

| 14      | SDI    | Serial Data input signal          |  |  |  |  |

| 15      | /CS    | Active LOW Chip Select signal     |  |  |  |  |

| 16      | NC     | No Connect                        |  |  |  |  |

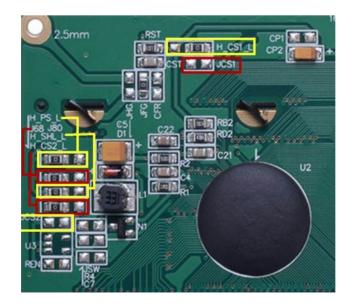

### 3.3 Jumper Selections

| Pin No.                | L_SHL_H | J68_J80 | L_PS_H | L_CS1_H | L_CS2_H | JCS1  | JCS2  |

|------------------------|---------|---------|--------|---------|---------|-------|-------|

| 6800 Parallel(default) | Н       | J68     | Н      | L       | L       | Х     | Х     |

| 8080 Parallel          | Н       | J80     | Н      | L       | L       | Х     | Х     |

| Serial                 | Н       | Х       | L      | Open    | Open    | Short | Short |

X= Don't Care

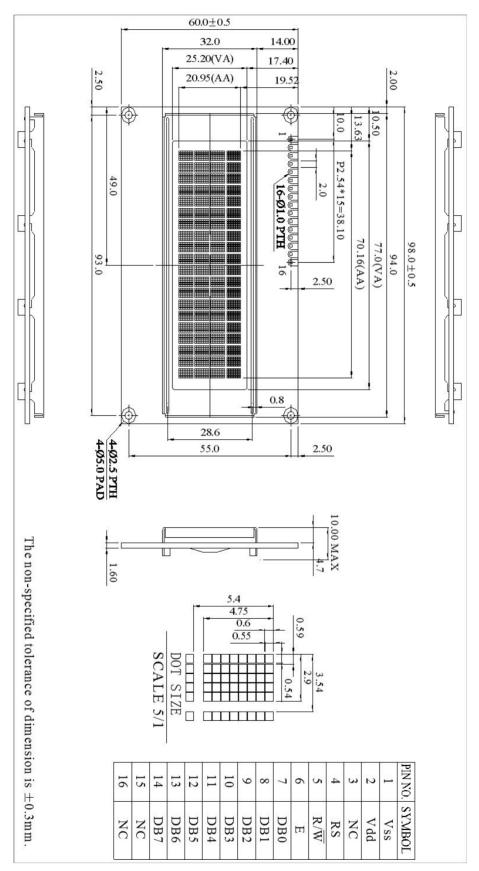

# 4 Mechanical Drawing

### DM-OLED2004-611

| MPU       | RS<br>R/W<br>E | WS0010<br>Master | C1~C16<br>S1~S100 | 20X4 OLED |

|-----------|----------------|------------------|-------------------|-----------|

| 68 Series | DB0~DB7        | WS0010<br>Slave  | S101~S200         |           |

| Address Format         | DB7 | DB6  | DB5  | DB4  | DB3  | DB2  | DB1  | DB0  |

|------------------------|-----|------|------|------|------|------|------|------|

| CA (Character Address) | 1   | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

| Display Position | 1  | 2  | 3  | 4  | ···. | ···. | 17 | 18 | 19 | 20 |

|------------------|----|----|----|----|------|------|----|----|----|----|

| DD RAM Address   | 00 | 01 | 02 | 03 | ···  | ···  | 10 | 11 | 12 | 13 |

| DD RAM Address   | 40 | 41 | 42 | 43 |      | ···· | 50 | 51 | 52 | 53 |

| DD RAM Address   | 14 | 15 | 16 | 17 | ···  | ···. | 24 | 25 | 26 | 27 |

| DD RAM Address   | 54 | 55 | 56 | 57 | ···. | ···  | 64 | 65 | 66 | 67 |

# **5** Electrical Characteristics

| Item                      | Symbol          | Condition    | Min    | Тур | Max    | Unit |

|---------------------------|-----------------|--------------|--------|-----|--------|------|

| Supply Voltage For Logic  | VDD             |              | 3.0    | 5.0 | 5.3    | V    |

| 50% Operation Current     | IDD             | -            | 52     | 60  | 65     | mA   |

| Low Level Input Voltage   | V <sub>IL</sub> |              | GND    | -   | 0.2VDD | V    |

| High Level Input Voltage  | V <sub>IH</sub> |              | 0.8VDD | -   | VDD    | V    |

| Low Level Output Voltage  | V <sub>OL</sub> |              | GND    |     | 0.2VDD | V    |

| High Level Output Voltage | V <sub>OH</sub> |              | 0.8VDD |     | VDD    | V    |

| Operating Temperature     | TOP             | Absolute Max | -40    |     | 80     | °C   |

| Storage Temperature       | TST             | Absolute Max | -40    |     | 80     | °C   |

# **6** Optical Characteristics

| Item                       | Symbol         | Min    | Тур    | Max | Unit  |

|----------------------------|----------------|--------|--------|-----|-------|

| View Angles - Horizontal   | AH             | 160    |        |     | 0     |

| View Angles - Vertical     | AV             | 160    |        |     | 0     |

| Response Time (25°C)       | Tr + Tf        |        | 20     |     | us    |

| Contrast Ratio             | CR             | 2000:1 |        |     |       |

| 50% check Board Brightness | L <sub>v</sub> | 70     | 80     |     | cd/m² |

| Operation Life Time        |                | 80000  | 100000 |     | Hrs   |

Notes:

1. Lifetime is defined the amount of time when the luminance has decayed to <50% of the initial value.

2. This analysis method uses life data obtained under accelerated conditions to extrapolate an estimated probability density function (*pdf*) for the product under normal use conditions.

3. Screen saving mode will extend OLED lifetime.

## 7 MPU Interface

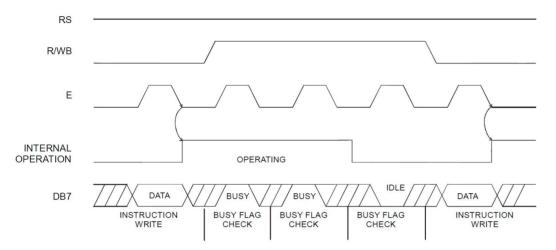

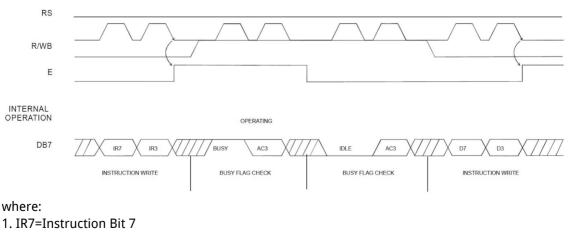

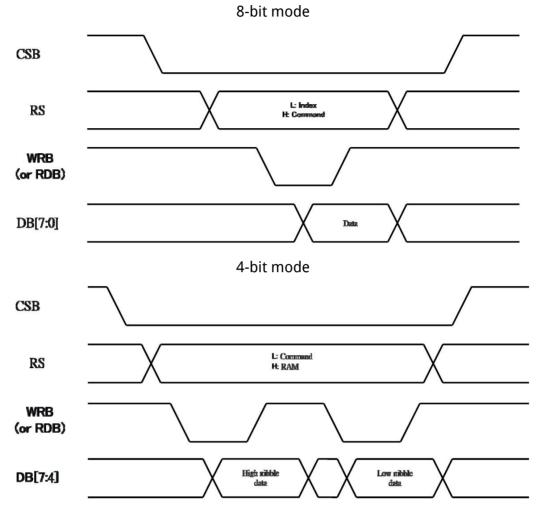

### 7.1 68 series Interface 8-BIT mode(Not available for serial mode)

When WS0010 interfaces with an 8-bit MPU, DB0 to DB7 are used. The 8-bit data transfer starts from the four high order bits --DB4 to DB7 followed by the four low order bits -- DB0 to DB3. An example of a Busy Flag Check Timing in an 8-Bit MPU Interface is given in the diagram below.

### 4-BIT mode (Not available for serial mode)

WS0010 can be configured to interface with a 4-bit MPU and is selected via a program. If the I/O port of the 4-Bit MPU from which WS0010 is connected to, is capable of transferring 8 bits, then an 8-bit data transfer operation is executed. Otherwise, two 4-bit data transfer operations are needed to satisfy one complete data transfer.

Under the 4-bit data transfer, DB4 to DB7 are used as bus lines. DB0 to DB3 are disabled. The data transfer between WS0010 and MPU is completed after two 4-bit data have been transferred. The Busy Flag must be checked (one instruction) after completion of the data transfer (that is, 4-bit data has been transferred twice.). The Busy Flag must be checked after two 4-bits data transfer has been completed. Please refer to the diagram below for a 4-bit data transfer timing sequence.

- 2. IR3=Instruction Bit 3

- 3. AC3=Address Counter 3

From the above timing diagram, it is important to note that the Busy Flag Check and the data transfer are both executed twice.

### 7.2 80-Series Interface

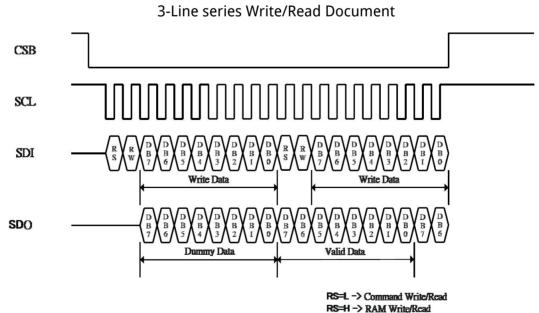

### 7.3 Serial Interface

# 8 Table of Commands

| Instruction                                 | Code | e    |               |      |                                                                            | Description | Max.<br>Execution<br>Time when |     |     |     |                                                                                                                                                                                                       |                         |

|---------------------------------------------|------|------|---------------|------|----------------------------------------------------------------------------|-------------|--------------------------------|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                             | RS   | R/WB | DB7           | DB6  | DB5                                                                        | DB4         | DB3                            | DB2 | DB1 | DB0 |                                                                                                                                                                                                       | fsp or fosc =<br>250KHz |

| Clear Display                               | 0    | 0    | o o o o o o 1 |      | Clears entire display.<br>Sets DDRAM Address 0 into the<br>Address Counter | 6.2ms       |                                |     |     |     |                                                                                                                                                                                                       |                         |

| Return Home                                 | 0    | 0    | 0             | 0    | 0                                                                          | 0           | 0                              | 0   | 1   | 0   | Sets DDRAM Address 0 into the<br>Address Counter.<br>Returns shifted display to<br>original position. DDRAM<br>contents remain unchanged.<br>(DB0 is test pin. User should<br>set DB0=0 all the time) | 0                       |

| Entry Mode<br>Set                           | 0    | 0    | o             | 0    | o                                                                          | 0           | 0                              | 1   | ٧D  | S   | Sets cursor move direction and<br>specifies display shift.<br>(These operations are<br>performed during data write and<br>read.)                                                                      | 0                       |

| Display<br>ON/OFF<br>Control                | 0    | 0    | 0             | 0    | 0                                                                          | 0           | 1                              | D   | с   | в   | Sets entire Display (D) ON/OFF.<br>Sets Cursor (C) ON/OFF.<br>Sets Blinking (B) of Cursor<br>Position Character.                                                                                      | 0                       |

| Cursor/<br>Display Shift/<br>Mode/ Pwr      | 0    | 0    | 0             | 0    | 0                                                                          | 1           | S/C                            | R/L | 0   | 0   | Moves cursor & shifts display<br>without changing DDRAM<br>contents.                                                                                                                                  | 0                       |

|                                             |      |      |               |      |                                                                            |             | G/C                            | PWR | 1   | 1   | Sets Graphic/Character Mode<br>Sets internal power on/off                                                                                                                                             |                         |

| Function Set                                | 0    | 0    | 0             | 0    | 1                                                                          | DL          | N                              | F   | FT1 | FTO | Sets interface data length (DL).<br>Sets number of display lines (N).<br>Sets Character Font (F).<br>Sets Font Table (FT)                                                                             | 0                       |

| et CGRAM<br>Address                         | 0    | 0    | 0             | 1    | ACG                                                                        | ACG         | ACG                            | ACG | ACG | ACG | Sets CGRAM Address. CGRAM<br>data is sent and received after this<br>setting.                                                                                                                         | 0                       |

| et DDRAM<br>Address                         | 0    | 0    | 1             | ADD  | ADD                                                                        | ADD         | ADD                            | ADD | ADD | ADD | Sets DDRAM Address. The<br>DDRAM data Is sent and<br>received after this setting.                                                                                                                     | 0                       |

| ead Busy<br>Flag &<br>Address               | 0    | 1    | BF            | AC   | AC                                                                         | AC          | AC                             | AC  | AC  | AC  | Reads Busy Flag (BF) indicating<br>that internal operation is being<br>performed.<br>Reads Address Counter<br>contents.                                                                               | 0                       |

| Write data<br>into the<br>CGRAM or<br>DDRAM | 1    | 0    | Write I       | Data |                                                                            |             | 122                            |     |     | ă.  | Writes data into the CGRAM or<br>DDRAM                                                                                                                                                                | 0                       |

| Read Data<br>from the<br>CGRAM or<br>DDRAM  | 1    | 1    | Read          | Data |                                                                            |             |                                |     |     |     | Read data from the CGRAM or<br>DDRAM                                                                                                                                                                  | 0                       |

Notes:

- 1. After the After the CGRAM/DDRAM Read or Write Instruction has been executed, the RAM Address Counter is incremented or decremented by 1. After the Busy Flag is turned OFF, the RAM Address is updated.

- 2. I/D=Increment/Decrement Bit; I/D="1": Increment; I/D="0": Decrement

- 3. S=Shift Entire Display Control Bit. When S="0", shift function disable.

- 4. 4. BF=Busy Flag

- BF="1": Internal Operating in Progress

- BF="0": No Internal Operation is being executed, next instruction can be accepted.

- 5. R/L=Shift Right/Left; R/L="1": Shift to the Right; R/L="0": Shift to the Left

- 6. S/C=Display Shift/Cursor Move; S/C="1": Display Shift; S/C="0": Cursor Move

- 7. G/C=Graphic/Character mode selection. G/C="0", Character mode is selected. G/C="1", Graphic mode is selected.

- 8. PWR=Internal DCDC on/of control. PWR="1", DCDC on. PWR="0", DCDC off.

- 9. DDRAM=Display Data RAM

- 10. CGRAM=Character Generator RAM

- 11. ACG=CGRAM Address

- 12. ADD=Address Counter Address (corresponds to cursor address)

- 13. AC=Address Counter (used for DDRAM and CGRAM Addresses)

- 14. F=Character Pattern Mode; F="1": 5 x 10 dots; F="0": 5 x 8 dots

- 15. N=Number of Lines Displayed; N="1": 2 -Line Display; N="0": 1-Line Display

## 9 Instruction Description

### **Clear Display Instruction**

| Ĩ | RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Ī | 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

This instruction is used to clear the Display Write Space 20H in all DDRAM Addresses. That is, the character pattern for the Character Code 20H must be a BLANK pattern. It then sets the DDRAM Address 0 into the Address Counter and reverts the display to its original state (if the display has been shifted). The display will be cleared and the cursor or blinking will go to the left edge of the display. If there are 2 lines displayed, the cursor or blinking will go to the first line 's left edge of the display. Under the Entry Mode, this instruction also sets the I/D to 1 (Increment Mode). The S Bit of the Entry Mode does not change.

#### **Return Home Instruction**

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | *   |

Note: \* = Not Relevant

This instruction is used to set the DDRAM Address 0 into the Address Counter and revert the display to its original status (if the display has been shifted). The DDRAM contents do not change.

The cursor or blinking will go to the left edge of the display. If there are 2 lines displayed, the cursor or blinking will go to the first line's left edge of the display.

#### **Entry Mode Set Instruction**

The Entry Mode Set Instruction has two controlling bits: I/D and S. Please refer to the table below.

|                                 | 1/D | 2   |

|---------------------------------|-----|-----|

|                                 |     | c   |

| RS R/WB DB7 DB6 DB5 DB4 DB3 DB2 | DB1 | DB0 |

I/D is the Increment/Decrement bit

When I/D is set to "1", the DDRAM Address is incremented by "1" when a character code is written into or read from the DDRAM. An increment of 1 will move the cursor or blinking one step to the right. When I/D is set to "0", the DDRAM is decremented by 1 when a character code is written into or read from the DDRAM. A decrement of 1 will move the cursor or blinking one step to the left.

#### S: Shift Entire Display Control bit

This bit is used to shift the entire display. When S is set to "1", the entire display is shifted to the right (when I/D ="0") or left (when I/D ="1"). When S is set to "0", the display is not shifted. Ex1 : I/D=1, S=1

|   |   | 1 | 2 | 3 | 4 |   |       |

|---|---|---|---|---|---|---|-------|

|   | 1 | 2 | 3 | 4 | A | _ | Input |

| 1 | 2 | 3 | 4 | A | В | _ | Input |

| 2 | 3 | 4 | A | В | С |   | Input |

| 3 | 4 | A | В | С | D |   | Input |

Initial display

Input new character "A" Input new character "B"

Input new character "C"

Input new character "D"

Ex2 : I/D=0, S=1

| 1 | 2 | 3 | 4 | 32       |   | C3- | Initial display         |

|---|---|---|---|----------|---|-----|-------------------------|

|   | 1 | 2 | 3 | <u>4</u> | A | -   | Input new character "A" |

|   |   | 1 | 2 | <u>3</u> | В | A   | Input new character "B" |

|   |   |   | 1 | 2        | С | В   | Input new character "C" |

|   |   |   |   | 1        | D | С   | Input new character "D" |

#### **Display On/Off Control Instruction**

The Display On / OFF Instruction is used to turn the display ON or OFF. The controlling bits are D, C and B.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

### D: DISPLAY ON/OFF BIT

When D is set to "1", the display is turned ON. When D is set to "0", the display is turned OFF and the display data is stored in the DDRAM. The display data can be instantly displayed by setting D to "1". C: CURSOR DISPLAY CONTROL BIT

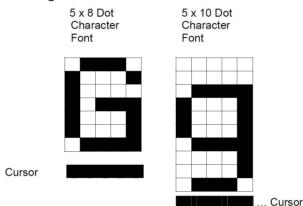

When C is set to "1", the cursor is displayed. In a 5 x 8 dot character font, the cursor is displayed via the

5 dots in the 8th line. In a 5 x 10 dot character font, it is displayed via 5 dots in the 11th line. When C is set to "0", the cursor display is disabled.

During a Display Data Write, the function of the I/D and others will not be altered even if the cursor is not present. Please refer to the figure below.

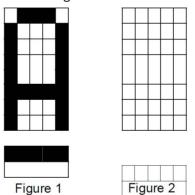

### **B: BLINKING CONTROL BIT**

When B is set to '1", the character specified by the cursor blinks. The blinking feature is displayed by switching between the blank dots and the displayed character at a speed of 409.6ms intervals when the fcp or fosc is 250kHz. Please refer to the figure below.

Note: Figures 1 and 2 are alternately displayed

The cursor and the blinking can be set to display at the same time. The blinking frequency depends on the fosc or the reciprocal of fcp.

To illustrate, when fosc=250K Hz, then, the blinking frequency=409.6 x 250/270=379.2ms

### **Cursor/Display Shift Instruction**

This instruction is used to shift the cursor or display position to the left or right without writing or reading the Display Data. This function is used to correct or search the display. Please refer to the table below.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 1   | S/G | R/L | 0   | 0   |

| 0  | 0    | 0   | 0   | 0   | 1   | G/C | PW  | 1   | 1   |

S/C R/L Shift Function

| 0 | 0 | Shifts the cursor position to the left. (AC is decremented by 1).        |

|---|---|--------------------------------------------------------------------------|

| 0 | 1 | Shifts cursor position to the right. (AC incremented by 1).              |

| 1 | 0 | Shifts entire display to the left. The cursor follows the display shift. |

| 4 | 4 |                                                                          |

1 Shifts the entire display to the right. The cursor follows the display shift.

In a 2-line Display, the cursor moves to the second line when it passes the 40th digit of the first line. The first and second line displays will shift at the same time.

When the displayed data is shifted repeatedly, each line moves only horizontally. The second line display does not shift into the first line position.

The Address Counter (AC) contents will not change if the only action performed is a Display Shift. G/C: GRAPHIC MODE / CHARACTER MODE SELECTION

This bit is used to select the display mode for further process. When G/C = 1, the GRAPHIC MODE will be selected.

When G/C = 0, the CHARACTER MODE will be selected.

PWR: ENABLE/DISABLE INTERNAL POWER

This bit is used to turn ON or turn OFF the internal power.

When PWR = 1, the internal power is turned ON.

When PWR = 0, the internal power is turned OFF.

### **Function Set Instruction**

The Function Set Instruction has three controlling 3 bits, namely: DL, N and F. Please refer to the table below.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| 0  | 0    | 0   | 0   | 1   | DL  | Ν   | F   | FT1 | FT0 |  |

|    |      |     |     |     |     |     |     |     |     |  |

### DL: INTERFACE DATA LENGTH CONTROL BIT

This is used to set the interface data length. When DL is set to "1", the data is sent or received in 8-bit length via the DB0 to DB7 (for an 8-Bit Data Transfer). When DL is set to "0", the data is sent or received in 4-bit length via DB4 to DB7 (for a 4-Bit Data Transfer). When the 4-bit data length is selected, the data must be sent or received twice.

### N: NUMBER OF DISPLAY LINE

This is used to set the number of display lines. When N="1", the 2-line display is selected. When N is set to "0", the 1-line display is selected.

#### F: CHARACTER FONT SET

This is used to set the character font set. When F is set to "0", the  $5 \times 8$  dot character font is selected. When F is set to "1", the  $5 \times 10$  dot character font is selected.

It must be noted that the character font setting must be performed at the head of the program before executing any instructions other than the Busy Flag and Address Instruction. Otherwise, the Function Set Instruction cannot be executed unless the interface data length is changed.

#### FT1, FT0: FONT TABLE SELECTION

These two bits are used to select one font table out of the three for further process.

When (FT1, FT0) = (0, 0), the ENGLISH\_JAPANESE CHARACTER FONT TABLE will be selected.

(FT1, FT0) = (0, 1), the WESTERN EUROPEAN CHARACTER FONT TABLE-I will be selected.

(FT1, FT0) = (1, 0), the ENGLISH\_RUSSIAN CHARACTER FONT TABLE will be selected.

(FT1, FT0) = (1, 1), the WESTERN EUROPEAN CHARACTER FONT TABLE-II will be selected.

Note: The default setting for FT1 and FT0 is 0 and 0 respectively which means the default Font Table is ENGLISH\_JAPANESE CHARACTER FONT TABLE.

### Set CGRAM Address Instruction

This instruction is used to set the CGRAM Address binary AAAAAA into the Address Counter. Data is then written to or read from the MPU for CGRAM.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | ACG | ACG | ACG | ACG | ACG | ACG |

Note: ACG is the CGRAM Address

Set DDRAM Address Instruction

This instruction is used to set the DDRAM Address binary AAAAAAA into the Address Counter. The data is written to or read from the MPU for the DDRAM. If 1-line display is selected (N="0"), then AAAAAAA can be 00H to 4FH. When the 2-line display is selected, then AAAAAAA can be 00H to 27H for the first line and 40H to 67H for the second line.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| 0  | 0    | 1   | ADD |  |

|    |      |     |     |     |     |     |     |     |     |  |

Note: ADD=DDRAM Address

### **Read Busy Flag and Address Instruction**

This instruction is used to read the Busy Flag (BF) to indicate if WS0010 is internally operating on a previously received instruction. If BF is set to "1", then the internal operation is in progress and the next instruction will not be accepted. If the BF is set to "0", then the previously received instruction has been executed and the next instruction can be accepted and processed. It is important to check the BF status before proceeding to the next write operation. The value of the Address Counter in binary AAAAAAA is simultaneously read out. This Address Counter is used by both the CGRAM and the DDRAM and its value is determined by the previous instruction. The contents of the address are the same as for the instructions -- Set CGRAM Address and Set DDRAM Address.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 1    | BF  | AC  |

Notes: BF=Busy Flag AC=Address Counter

### Write Data to CGRAM/DDRAM Instruction

This instruction writes 8-bit binary data -- DDDDDDDD to the CGRAM or the DDRAM. The previous CGRAM or DDRAM Address setting determines whether a data is to be written into the CGRAM or the DDRAM. After the write process is completed, the address is automatically incremented or decremented by 1 in accordance with the Entry Mode instruction. It must be noted that the Entry Mode instruction also determines the Display Shift.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 0    | D   | D   | D   | D   | D   | D   | D   | D   |

### Read Data from the CGRAM or DDRAM Instruction

This instruction reads the 8-bit binary data -- DDDDDDDD from the CGRAM or the DDRAM. The Set CGRAM Address or Set DDRAM Address Set Instruction must be executed before this instruction can be performed, otherwise, the first Read Data will not be valid.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1    | D   | D   | D   | D   | D   | D   | D   | D   |

When the Read Instruction is executed in series, the next address data is normally read from the Second Read. There is no need for the Address Set Instruction to be performed before this Read instruction when using the Cursor Shift Instruction to shift the cursor (Reading the DDRAM). The Cursor Shift Instruction has the same operation as that of the Set the DDRAM Address Instruction.

After a Read instruction has been executed, the Entry Mode is automatically incremented or decremented by 1. It must be noted that regardless of the Entry Mode, the Display Shift is not executed.

After the Write instruction to either the CGRAM or DDRAM has been performed, the Address Counter is automatically increased or decreased by 1. The RAM data selected by the Address Counter cannot be read out at this time even if the Read Instructions are executed. Therefore, in order to correctly read the data, the following procedure has suggested:

1. Execute the Address Set or Cursor Shift (only with DDRAM) Instruction

2. Just before reading the desired data, execute the Read Instruction from the second time the Read Instruction has been sent.

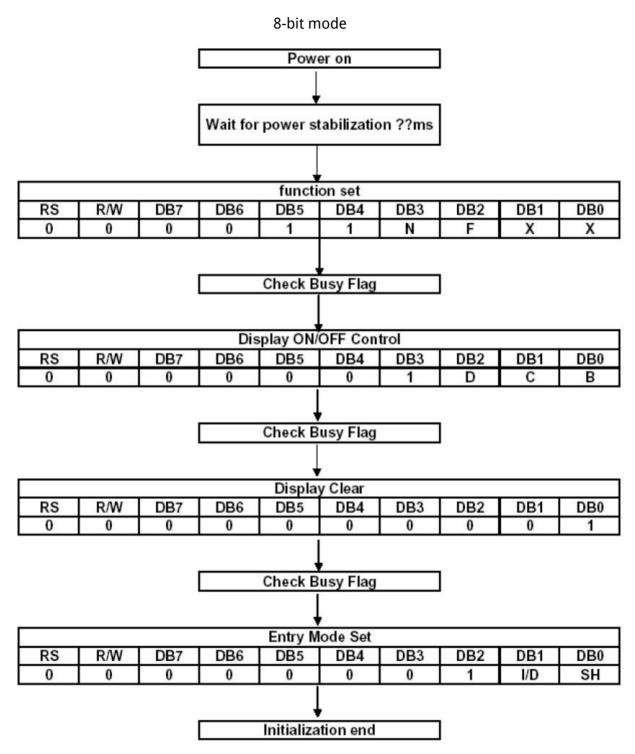

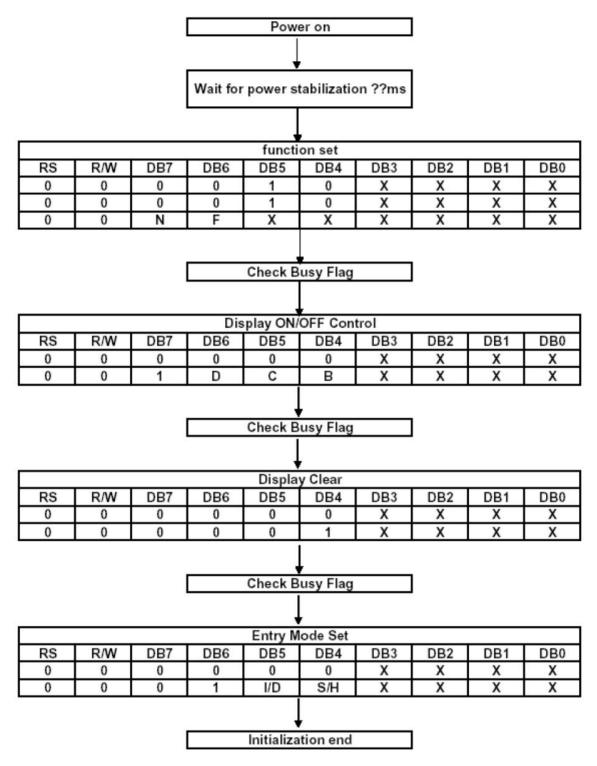

## 10 Initialization by Instruction

4-bit mode

## 11 Character Generator ROM (CGROM)

English\_Japanese Character Font Table(default FT[1:0]=00)

| Upper 4bit<br>Lower 4bit | ա                 | LLLH | LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH | HLHL | HLHH | HHLL | HHLH | HHHL | ннн |

|--------------------------|-------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|

| ш                        | CG<br>RAM<br>(1)  |      |      |      |      |      |      |      |      |      |      |      |      |      | œ    |     |

| ш                        | CG<br>RAM<br>(2)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LLHL                     | CG<br>RAM<br>(3)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LLHH                     | CG<br>RAM<br>(4)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHLL                     | CG<br>RAM<br>(5)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHLH                     | CG<br>RAM<br>(6)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHHL                     | CG<br>RAM<br>(7)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHHH                     | CG<br>RAM<br>(8)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLLL                     | CG<br>RAM<br>(9)  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLLH                     | CG<br>RAM<br>(10) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLHL                     | CG<br>RAM<br>(11) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLHH                     | CG<br>RAM<br>(12) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HHLL                     | CG<br>RAM<br>(13) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HHLH                     | CG<br>RAM<br>(14) |      |      |      |      |      |      |      | Ŋ    |      |      |      |      |      |      |     |

| HHHL                     | CG<br>RAM<br>(15) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| нннн                     | CG<br>RAM<br>(16) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

Western European Character Front Table 1(FT[1:0]=01)

| Upper 4bit<br>Lover 4bit | uu                | <br>LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH | HLHL | HLHH | HHLL | HHLH | HHHL | нннн |

|--------------------------|-------------------|----------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| ш                        | CG<br>RAM<br>(1)  |          |      | a    |      |      |      |      | Ш    |      |      |      |      |      |      |

| ш                        | CG<br>RAM<br>(2)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLHL                     | CG<br>RAM<br>(3)  |          |      | B    |      | Ð    |      |      |      |      |      |      |      |      |      |

| LLHH                     | CG<br>RAM<br>(4)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHLL                     | CG<br>RAM<br>(5)  |          |      | D    |      |      |      |      |      |      |      |      |      |      |      |

| LHLH                     | CG<br>RAM<br>(6)  |          |      |      |      | 8    |      |      |      |      |      |      |      |      |      |

| LHHL                     | CG<br>RAM<br>(7)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHHH                     | CG<br>RAM<br>(8)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLLL                     | CG<br>RAM<br>(9)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLLH                     | CG<br>RAM<br>(10) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLHL                     | CG<br>RAM<br>(11) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLHH                     | CG<br>RAM<br>(12) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHLL                     | CG<br>RAM<br>(13) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHLH                     | CG<br>RAM<br>(14) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHHL                     | CG<br>RAM<br>(15) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

| ннн                      | CG<br>RAM<br>(16) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |

### English\_Russian Character Font Table (FT[1:0]=10)

| Upper<br>4bit | ա                 |          | LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH | HLHL | HLHH | HHLL | HHLH | HHHL | ннн |

|---------------|-------------------|----------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|

| ш             | CG<br>RAM<br>(1)  |          |      |      |      |      |      |      | Ð    |      | B    | H    |      |      | Д    | M   |

| uu            | CG<br>RAM<br>(2)  | A        |      |      |      |      |      |      |      |      |      | 9    |      |      |      |     |

| LLHL          | CG<br>RAM<br>(3)  | <b>F</b> |      |      |      |      |      |      |      |      |      |      |      |      |      | 5   |

| LLHH          | CG<br>RAM<br>(4)  | H        |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHLL          | CG<br>RAM<br>(5)  | e e      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHLH          | CG<br>Ram<br>(6)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHHL          | CG<br>RAM<br>(7)  | Æ        |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| LHHH          | CG<br>RAM<br>(8)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLLL          | CG<br>RAM<br>(9)  |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLLH          | CG<br>RAM<br>(10) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLHL          | CG<br>RAM<br>(11) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLHH          | CG<br>RAM<br>(12) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HHLL          | CG<br>RAM<br>(13) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HHLH          | CG<br>RAM<br>(14) |          |      |      |      |      |      |      |      |      |      |      |      |      |      | 8   |

| HHHL          | CG<br>RAM<br>(15) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

| нннн          | CG<br>RAM<br>(16) |          |      |      |      |      |      |      |      |      |      |      |      |      |      |     |

### Western European Character Font Table II (FT[1:0]=11)

| Upper 4bit | ш                 | LLLH | LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH | HLHL    | HLHH | HHLL      | HHLH | HHHL | нннн |

|------------|-------------------|------|------|------|------|------|------|------|------|------|---------|------|-----------|------|------|------|

| Lower 4bit |                   |      |      |      |      |      |      |      |      |      | 1965265 |      |           |      |      |      |

| ш          | CG<br>RAM<br>(1)  |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| ш          | CG<br>RAM<br>(2)  |      |      |      |      |      |      | l    |      |      |         |      |           |      |      |      |

| LLHL       | CG<br>RAM<br>(3)  |      |      |      |      |      |      |      |      |      | 8       |      | <b>60</b> | m    | 30   |      |

| LLHH       | CG<br>RAM<br>(4)  |      | -    |      |      | EG   |      | 11   |      |      |         |      |           |      |      |      |

| LHLL       | CG<br>RAM<br>(5)  |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| LHLH       | CG<br>RAM<br>(6)  |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| LHHL       | CG<br>RAM<br>(7)  |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| LHHH       | CG<br>RAM<br>(8)  |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| HLLL       | CG<br>RAM<br>(9)  |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| HLLH       | CG<br>RAM<br>(10) |      |      |      |      |      |      |      |      |      |         |      |           | Π    |      |      |

| HLHL       | CG<br>RAM<br>(11) |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| HLHH       | CG<br>RAM<br>(12) |      |      |      |      |      |      |      |      |      |         |      |           | P    |      |      |

| HHLL       | CG<br>RAM<br>(13) |      |      |      |      |      |      |      |      |      |         |      |           |      |      |      |

| HHLH       | CG<br>RAM<br>(14) |      |      |      | M    |      |      |      |      |      | 60      |      |           | H    |      |      |

| HHHL       | CG<br>RAM<br>(15) |      |      |      |      |      |      |      |      |      | 0       |      |           |      |      |      |

| нннн       | CG<br>RAM<br>(16) |      |      |      |      |      | C    |      | *    |      |         |      | 8         |      |      |      |

Character Generator RAM (CGRAM)

| Upper 4bit | ա                 |   |   | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH | HLHL | HLHH | HHLL | HHLH | HHHL | ннн |

|------------|-------------------|---|---|------|------|------|------|------|------|------|------|------|------|------|------|-----|

| ш          | CG<br>RAM<br>(1)  |   |   | 8    | ß    | P    |      | P    |      |      |      |      |      |      |      | T   |

| ա          | CG<br>RAM<br>(2)  |   |   |      | Ĥ    | ٠    |      |      |      |      |      |      |      |      |      |     |

| LLHL       | CG<br>RAM<br>(3)  |   |   |      |      | R    |      |      |      |      |      |      |      |      |      |     |

| LLHH       | CG<br>RAM<br>(4)  | Ľ | - |      |      | 8    |      |      |      |      |      |      |      |      |      |     |

| LHLL       | CG<br>RAM<br>(5)  |   |   |      |      |      |      |      |      | 3    |      |      |      |      |      | 60  |

| LHLH       | CG<br>RAM<br>(6)  |   |   |      |      |      | 9    |      | 33   | 10   |      |      |      |      |      |     |

| LHHL       | CG<br>RAM<br>(7)  |   |   |      |      |      |      |      | 17   |      |      |      |      |      |      |     |

| LHHH       | CG<br>RAM<br>(8)  |   |   |      |      |      | 8    |      |      |      |      |      |      |      |      |     |

| HLLL       | CG<br>RAM<br>(9)  |   |   | 8    |      |      |      |      |      |      |      |      |      |      |      |     |

| HLLH       | CG<br>RAM<br>(10) |   |   |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HLHL       | CG<br>RAM<br>(11) |   |   |      |      | B.   |      |      | 3    |      |      |      |      |      |      |     |

| HLHH       | CG<br>RAM<br>(12) |   |   |      |      |      |      |      |      |      |      |      |      |      |      |     |

| HHLL       | CG<br>RAM<br>(13) |   |   |      |      | •••  |      |      |      |      |      |      |      |      |      |     |

| HHLH       | CG<br>RAM<br>(14) |   |   |      |      |      | m    |      |      |      |      | -    |      |      |      |     |

| HHHL       | CG<br>RAM<br>(15) |   |   |      |      |      | r    |      | Å    |      |      |      |      |      |      |     |

| нннн       | CG<br>RAM<br>(16) |   |   |      | ٠    |      | O    |      | *    |      | æ    |      |      |      |      |     |

# 12 Driver/Controller Information

Built-in WS0010 Controller:

https://drive.google.com/a/displaymodule.com/file/d/0BxCL-uXywP6wbDdvaTNaWIBYRFE/view?usp=sh aring

# 13 Reliability

| Test Item                               | Content of Test                                                                                                              | Test Condition                                             | Note |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|

| High Temperature                        | Endurance test applying the high storage                                                                                     | 80°C                                                       | 2    |

| Storage                                 | temperature for a long time.                                                                                                 | 240hrs                                                     | -    |

| Low Temperature                         | Endurance test applying the high storage                                                                                     | -40°C                                                      | 1,2  |

| Storage                                 | temperature for a long time.                                                                                                 | 240hrs                                                     | .,_  |

| High Temperature<br>Operation           | Endurance test applying the electric stress<br>(Voltage & Current) and the thermal stress<br>to the element for a long time. | 80°C<br>240hrs                                             | 2    |

| Low Temperature<br>Operation            | Endurance test applying the electric stress under low temperature for a long time.                                           | -40 °C<br>240hrs                                           | 1,2  |

| High Temperature/<br>Humidity Operation | Endurance test applying the high temperature and high humidity storage for a long time.                                      | 60°C,90%RH<br>240hrs                                       | 1,2  |

| Thermal Shock<br>Resistance             | Endurance test applying the low and high<br>temperature cycle.<br>-40°C 25°C 80°C+<br>30min 5min 30min+<br>1 cycle+          | -40°C/80°C<br>100 cycles                                   | -    |

| Vibration Test                          | Endurance test applying the vibration during transportation and using                                                        | 10~22Hz→15mm<br>p-p<br>22~500Hz→1.5G<br>Total 0.5hr        | 3    |

| Shock test                              | Constructional and mechanical endurance<br>test applying the shock during<br>transportation                                  | 50G Half sin<br>wave 11 ms<br>3 times of each<br>direction | -    |

| Atmospheric                             | Endurance test applying the atmospheric                                                                                      | 115mbar                                                    | 3    |

| Pressure test                           | pressure during transportation by air                                                                                        | 40hrs                                                      | 5    |

| Static Electricity Test                 | Endurance test apply the electric stress to the terminal.                                                                    | VS=800V,<br>RS=1.5kΩ,<br>CS=100pF,<br>1 time.              | -    |

Note1: No condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal. Temperature and humidity after remove from the rest chamber.

Note3: Test performed on product itself, not inside a container

# 14 Warranty and Conditions

http://www.displaymodule.com/pages/faq