# DM-OLED118-655

1.18" 128 × 128 MONOCHROME GRAHIC OLED DISPLAY PANEL -MCU, SPI, I2C

### Contents

- 1 Revision History

- 2 Main Features

- 3 Pin Description

- 3.1 Panel Pin Description

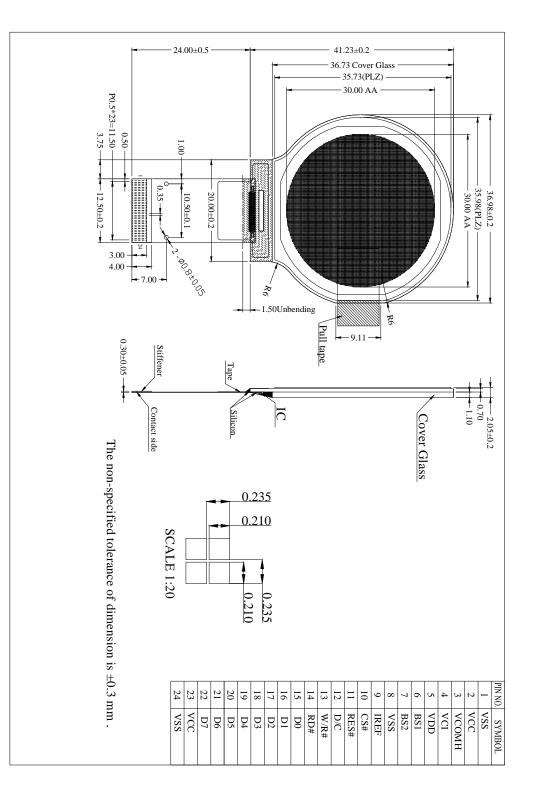

- 4 Mechanical Drawing

- 4.1 Panel Mechanical Drawing

- 5 Optics & Electrical Characteristics

- 5.1 Optical Characteristics

- 5.2 Absolute Maximum Ratings

- 5.3 DC Characteristics

- 5.4 AC Characteristics

- 5.4.1 6800-Series MCU Parallel Interface Timing Characteristics:

- 5.4.2 8000-Series MCU Parallel Interface Timing Characteristics:

- 5.4.3 Serial Interface Timing Characteristics:4-wire Serial

- 5.4.4 I<sup>2</sup>C Interface Timing Characteristics:

- 6 Power ON/OFF Timing Sequence

- 7 Reliability

- 8 Warranty and Conditions

## 1 Revision History

| Date       | Changes       |

|------------|---------------|

| 2019-07-17 | First release |

### 2 Main Features

| Item            | Specification                    | Unit   |

|-----------------|----------------------------------|--------|

| Diagonal Size   | 1.18                             | inch   |

| Display Mode    | Passive Matrix OLED              | -      |

| Display Colors  | Monochrome (White/Yellow/Blue)   | Colors |

| Resolution      | 128 x 128                        | pixel  |

| Controller IC   | SSD1327ZB                        | -      |

| Interface       | 6800/8080 MCU,SPI,I2C            | -      |

| Active Area     | 30.00×30.00                      | mm     |

| Panel Dimension | $36.98 \times 41.23 \times 2.05$ | mm     |

| Pixel Size      | $0.210 \times 0.210$             | -      |

| Pixel Pitch     | $0.235 \times 0.235$             | mm     |

| Drive Duty      | 1/128Duty                        | -      |

| Weight          | TBD                              | g      |

## 3 Pin Description

### 3.1 Panel Pin Description

| Pin No. | Symbol  | Function Description                                                                                             |  |  |  |  |

|---------|---------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | VSS     | Ground pin. It must be connected to external ground.                                                             |  |  |  |  |

| 2       | VCC     | Power supply for panel driving voltage. This is also the most positive power                                     |  |  |  |  |

| 2       | VCC     | voltage supply pin. It is supplied by external high voltage source.                                              |  |  |  |  |

|         |         | COM signal deselected voltage level.                                                                             |  |  |  |  |

| 3       | VCOMH   | A capacitor should be connected between this pin and VSS. No external power                                      |  |  |  |  |

| _       |         | supply is allowed to connect to this pin.                                                                        |  |  |  |  |

|         |         | Low voltage power supply and power supply for interface logic level. It should                                   |  |  |  |  |

|         | . LOI   | match with the MCU interface voltage level and must be connected to external                                     |  |  |  |  |

| 4       | VCI     | source.                                                                                                          |  |  |  |  |

|         |         | VCI must always set to be equivalent to or higher than VDD.                                                      |  |  |  |  |

| 5       | VDD     | Power supply pin for core logic operation.                                                                       |  |  |  |  |

|         |         | MCU bus interface selection pins. Select appropriate logic setting as described in                               |  |  |  |  |

|         |         | the following table. BS2, BS1 and BS0 are pin select.                                                            |  |  |  |  |

| 6       | BS1     | Bus Interface selection                                                                                          |  |  |  |  |

|         |         | BS[2:1] Interface                                                                                                |  |  |  |  |

|         |         | 00 4 line SPI                                                                                                    |  |  |  |  |

|         |         | 01 I2C                                                                                                           |  |  |  |  |

| 7       | BS2     | 11 8-bit 8080 parallel                                                                                           |  |  |  |  |

| ,       | 052     | 10 8-bit 6800 parallel                                                                                           |  |  |  |  |

|         |         | Note (1) 0 is connected to VSS (2) 1 is connected to VCI                                                         |  |  |  |  |

| 8       | VSS     | Ground pin. It must be connected to visit (2) I is connected to visit.                                           |  |  |  |  |

| 9       | IREF    | This pin is the segment output current reference pin                                                             |  |  |  |  |

| 9       | IKEF    | This pin is the segment output current reference pin<br>This pin is the chip select input connecting to the MCU. |  |  |  |  |

| 10      | CS#     | The chip is enabled for MCU communication only when CS# is pulled LOW                                            |  |  |  |  |

| 10      | $C5\pi$ | (active LOW).                                                                                                    |  |  |  |  |

|         |         | This pin is reset signal input.                                                                                  |  |  |  |  |

| 11      | RES#    | When the pin is pulled LOW, initialization of the chip is executed. Keep this pin                                |  |  |  |  |

| 11      | KL5#    | pull HIGH during normal operation.                                                                               |  |  |  |  |

|         |         | This pin is Data/Command control pin connecting to the MCU.                                                      |  |  |  |  |

|         |         | When the pin is pulled HIGH, the data at $D[7:0]$ will be interpreted as data. When                              |  |  |  |  |

|         |         | the pin is pulled LOW, the data at $D[7:0]$ will be transferred to a command                                     |  |  |  |  |

| 12      | D/C     | register.                                                                                                        |  |  |  |  |

|         |         | In I2C mode, this pin acts as SA0 for slave address selection.                                                   |  |  |  |  |

|         |         | When 3-wire serial interface is selected, this pin must be connected to VSS.                                     |  |  |  |  |

|         |         | This pin is read / write control input pin connecting to the MCU interface. When                                 |  |  |  |  |

|         |         | 6800 interface mode is selected, this pin will be used as Read/Write (R/W#)                                      |  |  |  |  |

|         |         | selection input. Read mode will be carried out when this pin is pulled HIGH and                                  |  |  |  |  |

| 13      | W/R#    | write mode when LOW.                                                                                             |  |  |  |  |

|         |         | When 8080 interface mode is selected, this pin will be the Write (WR#) input.                                    |  |  |  |  |

|         |         | Data write operation is initiated when this pin is pulled LOW and the chip is                                    |  |  |  |  |

|         |         | selected.                                                                                                        |  |  |  |  |

|         |         | This pin is MCU interface input.                                                                                 |  |  |  |  |

|         |         | When 6800 interface mode is selected, this pin will be used as the Enable (E)                                    |  |  |  |  |

|         |         | signal.                                                                                                          |  |  |  |  |

|         | ייבת    | Read/write operation is initiated when this pin is pulled HIGH and the chip is                                   |  |  |  |  |

| 14      | RD#     | selected.                                                                                                        |  |  |  |  |

|         |         | When 8080 interface mode is selected, this pin receives the Read (RD#) signal.                                   |  |  |  |  |

|         |         | Read operation is initiated when this pin is pulled LOW and the chip is selected.                                |  |  |  |  |

|         |         | When serial or I2C interface is selected, this pin must be connected to VSS.                                     |  |  |  |  |

| LI      |         |                                                                                                                  |  |  |  |  |

| 15 | D0  |                                                                                                                                                                |

|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 | D1  | These pins are bi-directional data bus connecting to the MCU data bus. Unused                                                                                  |

| 17 | D2  | pins are recommended to tie LOW.                                                                                                                               |

| 18 | D3  | When serial interface mode is selected, D0 will be the serial clock input: SCLK;                                                                               |

| 19 | D4  | D1 will be the serial data input: SDIN and D2 should be kept NC. When I2C                                                                                      |

| 20 | D5  | <ul> <li>mode is selected, D2, D1 should be tied together and serve as SDAout, SDAin in</li> <li>application and D0 is the serial clock input, SCL.</li> </ul> |

| 21 | D6  | application and D0 is the serial clock input, SCL.                                                                                                             |

| 22 | D7  |                                                                                                                                                                |

| 23 | VCC | Power supply for panel driving voltage. This is also the most positive power                                                                                   |

| 23 |     | voltage supply pin. It is supplied by external high voltage source.                                                                                            |

| 24 | VSS | Ground pin.                                                                                                                                                    |

Note: I=Input; O=Output; P=Power; I/O=Input / Output

## 4 Mechanical Drawing

### 4.1 Panel Mechanical Drawing

Copyright © 2019

## 5 Optics & Electrical Characteristics

#### 5.1 Optical Characteristics

| Item           | Symbol | Min    | Тур  | Max  | Unit | Remark   |

|----------------|--------|--------|------|------|------|----------|

| View Angles    | (V)θ   | 160    | -    | -    | 0    | -        |

| View Angles    | (H)φ   | 160    | -    | -    | 0    | -        |

| Desmanae Time  | T rise | -      | -    | 10   | μs   | -        |

| Response Time  | T fall | -      | -    | 10   | μs   | -        |

| C I E (White)  | (x)    | 0.26   | 0.28 | 0.30 |      | CIE 1021 |

| C.I.E(White)   | (y)    | 0.30   | 0.32 | 0.34 | -    | CIE 1931 |

| Contrast Ratio | CR     | 2000:1 | -    | -    | -    | Dark     |

#### 5.2 Absolute Maximum Ratings

| V <sub>CI</sub> | -0.3                          | 4.0                                                                       | V                                                                                                            | Note1,2                                                |

|-----------------|-------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|                 |                               |                                                                           |                                                                                                              | 110101,2                                               |

| V <sub>DD</sub> | -0.5                          | 2.75                                                                      | V                                                                                                            | Note1,2                                                |

| V <sub>CC</sub> | -0.5                          | 19                                                                        | V                                                                                                            | Note1,2                                                |

| ТОР             | -40                           | +80                                                                       | °C                                                                                                           | -                                                      |

| STG             | -40                           | +85                                                                       | °C                                                                                                           | -                                                      |

|                 | V <sub>CC</sub><br>TOP<br>STG | V <sub>CC</sub> -0.5           FOP         -40           TSTG         -40 | V <sub>CC</sub> -0.5         19           TOP         -40         +80           TSTG         -40         +85 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

Note1: All the above voltages are on the basis of "VSS = 0V".

Note2: When this module is used beyond the above absolute maximum ratings, permanent breakage of the module may occur. Also, for normal operations, it is desirable to use this module under the conditions according to Section6 "Electrical Characteristics". If this module is used beyond these conditions, malfunctioning of the module can occur and the reliability of the module may deteriorate

#### 5.3 DC Characteristics

| Item                              | Symbol          | Min                              | Тур. | Max                              | Unit | Remark                 |

|-----------------------------------|-----------------|----------------------------------|------|----------------------------------|------|------------------------|

| Logic Supply Voltage              | V <sub>CI</sub> | 2.8                              | 3.0  | 3.3                              | V    | -                      |

| Display Supply Voltage            | V <sub>CC</sub> | 14                               | 14.5 | 15                               | V    | -                      |

| Low Level Input Voltage           | V <sub>IL</sub> | 0                                | -    | 0.2 x V <sub>CI</sub>            | V    | -                      |

| High Level Input Voltage          | V <sub>IH</sub> | $0.8 \mathrm{x} \mathrm{V_{CI}}$ | -    | V <sub>CI</sub>                  | V    | -                      |

| Low Level Output Voltage          | Vol             | 0                                | -    | $0.1 \mathrm{x} \mathrm{V_{CI}}$ | V    | -                      |

| High Level Output Voltage         | V <sub>OH</sub> | 0.9 x V <sub>CI</sub>            | -    | V <sub>CI</sub>                  | V    | -                      |

| 50% Check Board operating Current |                 | -                                | 24   | 26                               | mA   | V <sub>CC</sub> =14.5V |

Note1: The input digital voltage is the I/O reference voltage.

Note2: VDDIO usually ranges from 1.65V to 1.95 V. If VDDIO is changed, the remaining voltage needs to be changed to the same voltage as VDDIO.

#### 5.4 AC Characteristics

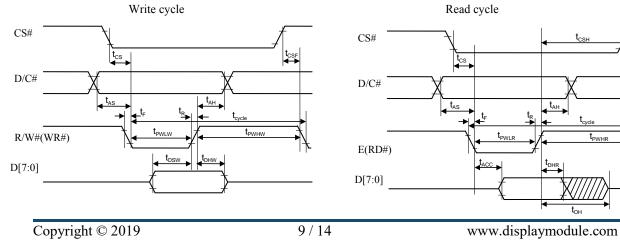

#### 5.4.1 6800-Series MCU Parallel Interface Timing Characteristics:

| Description                          | Min                                                                                                                                                                                                                                                                                                                                                | Max                                                                                                                                                                                                                                                                                   | Unit                                                                                                                                                                                                                                                                                    |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Cycle Time                     | 300                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Address Setup Time                   | 10                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Address Hold Time                    | 0                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Write Data Setup Time                | 40                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Write Data Hold Time                 | 44                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Read Data Hold Time                  | 20                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Output Disable Time                  | -                                                                                                                                                                                                                                                                                                                                                  | 70                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                      |

| Access Time                          | -                                                                                                                                                                                                                                                                                                                                                  | 250                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                      |

| Chip Select Low Pulse Width (Read)   | 120                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                         |

| Chip Select Low Pulse Width (Write)  | 60                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Chip Select High Pulse Width (Read)  | 60                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                         |

| Chip Select High Pulse Width (Write) | 60                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                      |

| Rise Time                            | -                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                      |

| Fall Time                            | _                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                      |

|                                      | Clock Cycle Time<br>Address Setup Time<br>Address Hold Time<br>Write Data Setup Time<br>Write Data Hold Time<br>Read Data Hold Time<br>Output Disable Time<br>Access Time<br>Chip Select Low Pulse Width (Read)<br>Chip Select Low Pulse Width (Write)<br>Chip Select High Pulse Width (Read)<br>Chip Select High Pulse Width (Write)<br>Rise Time | Clock Cycle Time300Address Setup Time10Address Hold Time0Write Data Setup Time40Write Data Hold Time44Read Data Hold Time20Output Disable Time-Access Time-Chip Select Low Pulse Width (Read)120Chip Select High Pulse Width (Read)60Chip Select High Pulse Width (Write)60Rise Time- | Clock Cycle Time300Address Setup Time10Address Hold Time0Write Data Setup Time40Write Data Hold Time44Read Data Hold Time20Output Disable Time-Access Time-Chip Select Low Pulse Width (Read)120Chip Select High Pulse Width (Read)60Chip Select High Pulse Width (Write)60Rise Time-15 |

\* ( $V_{CI} - V_{SS} = 1.65V$  to 2.1V,  $T_A = 25^{\circ}C$ )

| Symbol             | Description                          | Min | Max | Unit |

|--------------------|--------------------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 10  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                | 40  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                 | 20  | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | ns   |

| toн                | Output Disable Time                  | -   | 70  | ns   |

| tACC               | Access Time                          | -   | 140 | ns   |

| DW                 | Chip Select Low Pulse Width (Read)   | 120 |     |      |

| PW <sub>CSL</sub>  | Chip Select Low Pulse Width (Write)  | 60  | -   | ns   |

| DW                 | Chip Select High Pulse Width (Read)  | 60  |     |      |

| $PW_{CSH}$         | Chip Select High Pulse Width (Write) | 60  | -   | ns   |

| t <sub>R</sub>     | Rise Time                            | _   | 15  | ns   |

| t <sub>F</sub>     | Fall Time                            | -   | 15  | ns   |

\* ( $V_{CI} - V_{SS} = 2.1V$  to 3.5V,  $T_A = 25^{\circ}C$ )

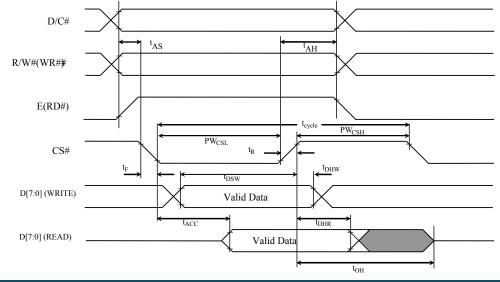

#### Figure 5-1 : 6800-series MCU parallel interface characteristics

Copyright © 2019

www.displaymodule.com

t<sub>он</sub>

| Symbol             | Description                          | Min | Max | Unit |

|--------------------|--------------------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 30  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                | 20  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                 | 42  | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | -   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                          | -   | 140 | ns   |

| t <sub>PWLR</sub>  | Read Low Time                        | 150 | -   | ns   |

| t <sub>PWLW</sub>  | Write Low Time                       | 60  | -   | ns   |

| t <sub>PWHR</sub>  | Read High Time                       | 60  | -   | ns   |

| t <sub>PWHW</sub>  | Write High Time                      | 60  | -   | ns   |

| t <sub>R</sub>     | Rise Time                            | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time                            | -   | 15  | ns   |

| t <sub>CS</sub>    | Chip select setup time               | 0   | -   | ns   |

| t <sub>CSH</sub>   | Chip select hold time to read signal | 0   | -   | ns   |

| t <sub>CSF</sub>   | Chip select hold time                | 20  | -   | ns   |

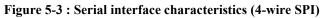

#### 5.4.2 8000-Series MCU Parallel Interface Timing Characteristics:

\*  $(V_{CI} - V_{SS} = 1.65V \text{ to } 2.1V, T_A = 25^{\circ}C)$

| Symbol             | Description                          | Min | Max | Unit |

|--------------------|--------------------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 18  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                | 14  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                 | 20  | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | -   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                          | -   | 140 | ns   |

| t <sub>PWLR</sub>  | Read Low Time                        | 150 | -   | ns   |

| t <sub>PWLW</sub>  | Write Low Time                       | 60  | -   | ns   |

| tpwhr              | Read High Time                       | 60  | -   | ns   |

| tpwhw              | Write High Time                      | 60  | -   | ns   |

| t <sub>R</sub>     | Rise Time                            | -   | 15  | ns   |

| tF                 | Fall Time                            | -   | 15  | ns   |

| tcs                | Chip select setup time               | 0   | -   | ns   |

| tcsh               | Chip select hold time to read signal | 0   | -   | ns   |

| t <sub>CSF</sub>   | Chip select hold time                | 20  | -   | ns   |

\* ( $V_{CI} - V_{SS} = 2.1V$  to 3.5V,  $T_A = 25^{\circ}C$ )

| Symbol             | Description            | Min | Max | Unit |

|--------------------|------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 220 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 15  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 15  | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 20  | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 10  | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time  | 15  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time   | 30  | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 25  | -   | ns   |

| t <sub>CLKH</sub>  | Clock High Time        | 20  | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time              | -   | 15  | ns   |

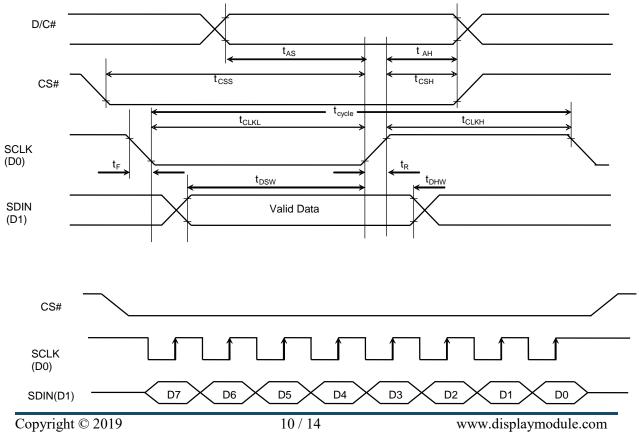

#### 5.4.3 Serial Interface Timing Characteristics:4-wire Serial

\* ( $V_{CI}$  - $V_{SS}$  = 1.65V to 2.1V,  $T_A$  = 25°C)

| Symbol             | Description            | Min | Max | Unit |

|--------------------|------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 160 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 15  | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 15  | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 20  | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 10  | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time  | 15  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time   | 15  | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 20  | -   | ns   |

| t <sub>CLKH</sub>  | Clock High Time        | 20  | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time              | -   | 15  | ns   |

\* ( $V_{CI} - V_{SS} = 2.1$ V to 3.5V,  $T_A = 25$ °C)

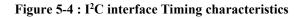

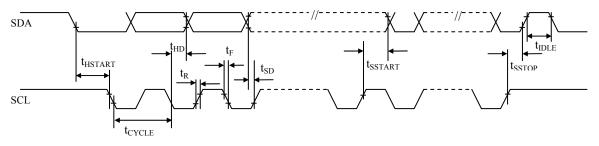

#### 5.4.4 I<sup>2</sup>C Interface Timing Characteristics:

| Symbol              | Description                                                                  | Min | Max | Unit |

|---------------------|------------------------------------------------------------------------------|-----|-----|------|

| t <sub>cycle</sub>  | Clock Cycle Time                                                             | 2.5 | -   | μs   |

| t <sub>HSTART</sub> | Start Condition Hold Time                                                    | 0.6 | -   | μs   |

| t <sub>HD</sub>     | Data Hold Time (for "SDA <sub>OUT</sub> " pin)                               | 0   | -   | ns   |

|                     | Data Hold Time (for "SDA <sub>IN</sub> " pin)                                | 300 | -   | ns   |

| t <sub>SD</sub>     | Data Setup Time                                                              | 10  | -   | ns   |

| t <sub>SSTART</sub> | Start condition Setup Time<br>(Only relevant for a repeated Start condition) | 0.6 | -   | μs   |

| t <sub>SSTOP</sub>  | Stop Condition Setup Time                                                    | 0.6 | -   | μs   |

| t <sub>R</sub>      | Rise Time                                                                    | -   | 300 | ns   |

| t <sub>F</sub>      | Fall Time                                                                    | -   | 300 | ns   |

| t <sub>IDLE</sub>   | Idle Time before a new transmission can start                                | 1.3 | -   | μs   |

\*  $(V_{CI} - V_{SS} = 1.65V \text{ to } 3.5V, T_A = 25^{\circ}C)$

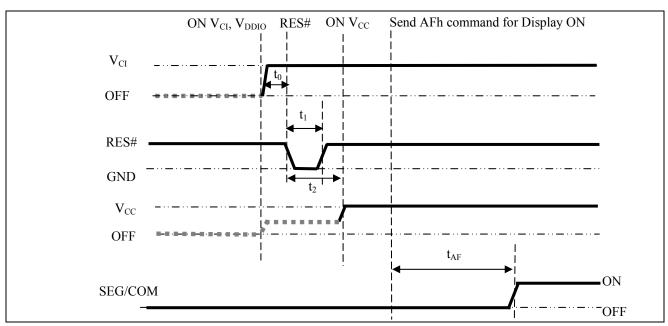

### 6 Power ON/OFF Timing Sequence

The following figures illustrate the recommended power ON and power OFF sequence of SSD1327 (assume internal  $V_{DD}$  is used).

Power ON sequence:

1. Power ON V<sub>CI</sub>.

- 2.After  $V_{CI}$  becomes stable, set wait time at least 1ms (t0) for internal  $V_{DD}$  become stable. Then set RES# pin LOW (logic low) for at least 100us (t<sub>1</sub>) <sup>(4)</sup> and then HIGH (logic high).

- 3.After set RES# pin LOW (logic low), wait for at least 100us (t<sub>2</sub>). Then Power ON V<sub>CC</sub>.<sup>(1)</sup>

- 4.After  $V_{CC}$  become stable, send command AFh for display ON. SEG/COM will be ON after 200ms ( $t_{AF}$ ).

- 5. After  $V_{CI}$  become stable, wait for at least 300ms to send command.

Figure 6-1 : The Power ON sequence.

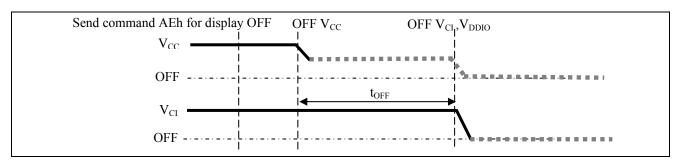

Power OFF sequence:

- 1. Send command AEh for display OFF.

- 2. Power OFF  $V_{CC}$ .<sup>(1), (2),(3)</sup>

- 3. Wait for t<sub>OFF</sub>. Power OFF V<sub>CI</sub>. (where Minimum t<sub>OFF</sub>=0ms<sup>(5)</sup>, Typical t<sub>OFF</sub>=100ms)

#### Figure 6-2 : The Power OFF sequence

Note:

<sup>(1)</sup> Since an ESD protection circuit is connected between  $V_{CI}$  and  $V_{CC}$ ,  $V_{CC}$  becomes lower than  $V_{CI}$  whenever  $V_{CI}$  is ON and  $V_{CC}$  is OFF as shown in the dotted line of  $V_{CC}$  in Figure 6-1 and Figure 6-2.

- <sup>(2)</sup> V<sub>CC</sub> should be kept float (disable) when it is OFF.

- $^{(3)}$  Power pins (V<sub>CI</sub>, V<sub>CC</sub>) can never be pulled to ground under any circumstance.

- $^{\left( 4\right) }$  The register values are reset after  $t_{1}.$

- $^{(5)}$   $V_{CI}$  should not be Power OFF before  $V_{CC}$  Power OFF.

## 7 Reliability

| Test Item                  | Content of Test                                | Test Condition | Note |  |

|----------------------------|------------------------------------------------|----------------|------|--|

| High Temperature Storage   | Endurance test applying the high storage       | 80°C           | 2    |  |

| Tigit Temperature Storage  | temperature for a long time.                   | 240hrs         |      |  |

| Low Tommonstrum Storego    | Endurance test applying the high storage       | -40°C          | 1.2  |  |

| Low Temperature Storage    | temperature for a long time.                   | 240hrs         | 1,2  |  |

|                            | Endurance test applying the electric stress    | 80°C           |      |  |

| High Temperature Operation | (Voltage & Current) and the thermal stress to  | 240hrs         | -    |  |

|                            | the element for a long time.                   | 240113         |      |  |

| Low Temperature Operation  | Endurance test applying the electric stress    | -40°C          | 1    |  |

| Low remperature operation  | under low temperature for a long time.         | 240hrs         | 1    |  |

|                            | The module should be allowed to stand at       |                |      |  |

| High Temperature/          | 60°C,90%RH max, for 96hrs under no-load        | 60°C,90%RH     | 1,2  |  |

| Humidity Operation         | condition excluding the polarizer. Then taking | 240hrs         |      |  |

|                            | it out and drying it at normal temperature.    |                |      |  |

| Thermal Shock Resistance   | The sample should be allowed stand the         | -40°C/80°C     |      |  |

| Thermai Shock Resistance   | following 10 cycles of operation               | 100cycles      | -    |  |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal. Temperature and humidity after remove from the rest chamber.

### 8 Warranty and Conditions

http://www.displaymodule.com/pages/faq HYPERLINK "http://www.displaymodule.com/pages/faq"