# DM-OLED095-626 0.95" 96 X 64 FULL COLOR OLED DISPLAY MODULE WITH SPI INTERFACE

### Contents

**Revision History**

Main Features

Pin Description

Panel Pin Description

Module Pin Description

Mechanical Drawing

Panel Mechanical Drawing

Module Mechanical Drawing

**Electrical Characteristics**

**Optical Characteristics**

**Timing Characteristics**

Serial Interface Timing Characteristics

**Functional Specification**

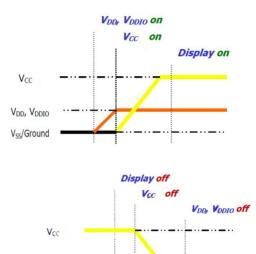

Power down and Power up Sequence

Reset Circuit

Driver/Controller Information

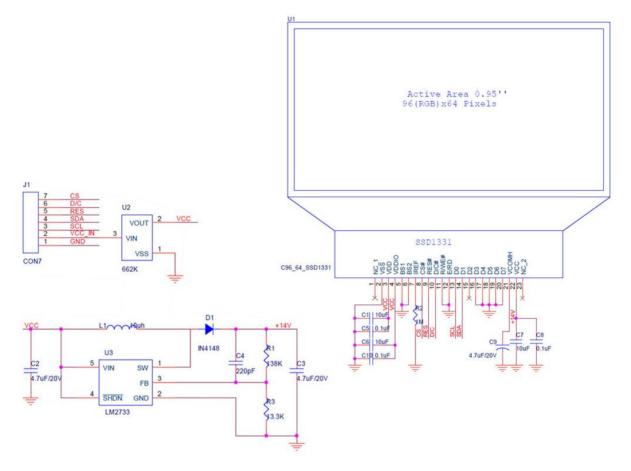

Module Schematic

Example Application

Command Table

**Reliability**

Warranty and Conditions

## 1 Revision History

| Date       | Changes       |

|------------|---------------|

| 2015-12-28 | First release |

### 2 Main Features

| Item             | Specification        | Unit   |

|------------------|----------------------|--------|

| Diagonal Size    | 0.95″                | inch   |

| Display Mode     | Passive Matrix OLED  | -      |

| Display Colors   | 65,536(Maximum)      | Colors |

| Resolution       | 96 x 64              | pixel  |

| Controller IC    | SSD1331              | -      |

| Duty             | 1/64                 | duty   |

| Interface        | SPI                  | -      |

| Active Area      | 20.14 x 13.42        | mm     |

| Module Dimension | 25.70 x 22.20 x 1.50 | mm     |

| Weight           | 1.8                  | g      |

# 3 Pin Description

### 3.1 Panel Pin Description

| Pin No. | Symbol     | Function Descrip                                                                                               | tion                |                     |                  |  |  |  |  |  |  |

|---------|------------|----------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------------------|--|--|--|--|--|--|

| THING.  | Symbol     | Reserved Pin (Su                                                                                               |                     |                     |                  |  |  |  |  |  |  |

| 1       | NC         | The supporting p                                                                                               |                     | e influences from   | stresses on the  |  |  |  |  |  |  |

|         |            | function pins.                                                                                                 |                     |                     |                  |  |  |  |  |  |  |

|         |            | Ground of OEL Sy                                                                                               | /stem               |                     |                  |  |  |  |  |  |  |

| 2       |            | This is a ground pin. It also acts as a reference for the logic pins, the                                      |                     |                     |                  |  |  |  |  |  |  |

| 2       | VSS        | OEL driving voltages, and the analog circuits. It must be connected                                            |                     |                     |                  |  |  |  |  |  |  |

|         |            | to external ground.                                                                                            |                     |                     |                  |  |  |  |  |  |  |

|         |            | Power Supply Pins for Core VDD                                                                                 |                     |                     |                  |  |  |  |  |  |  |

| 3       | VDD        | This is a voltage s                                                                                            | supply pin. It mus  | t be connected to   | o external       |  |  |  |  |  |  |

| -       |            | source.                                                                                                        |                     |                     |                  |  |  |  |  |  |  |

|         |            | Power Supply for                                                                                               |                     |                     |                  |  |  |  |  |  |  |

| 4       | VDDIO      | It should be mate                                                                                              |                     |                     | evel.            |  |  |  |  |  |  |

|         |            | VDDIO must alwa                                                                                                |                     | wer than VDD.       |                  |  |  |  |  |  |  |

|         |            | Communicating I                                                                                                |                     |                     |                  |  |  |  |  |  |  |

|         |            | These pins are M                                                                                               | CU Interface sele   | ction input. See ti | ne following     |  |  |  |  |  |  |

| 5       | BS1        | table:                                                                                                         | 68XX-parallel       | 80XX-parallel       | Serial           |  |  |  |  |  |  |

| 6       | BS2        | BS1                                                                                                            | 0                   | 0077-parallel       | 0                |  |  |  |  |  |  |

|         |            | BS2                                                                                                            | 1                   | 1                   | 0                |  |  |  |  |  |  |

|         |            |                                                                                                                | 1                   | I                   | 0                |  |  |  |  |  |  |

|         |            | Current Reference                                                                                              | e for Brightness    | Adjustment          |                  |  |  |  |  |  |  |

| 7       | IREF       | Current Reference for Brightness Adjustment<br>This pin is segment current reference pin. A resistor should be |                     |                     |                  |  |  |  |  |  |  |

| ,       |            |                                                                                                                |                     |                     |                  |  |  |  |  |  |  |

|         |            | connected between this pin and VSS. Set the current at 10uA.<br>Chip Select                                    |                     |                     |                  |  |  |  |  |  |  |

| 8       | CS#        | This pin is the chip select input. The chip is enabled for MCU                                                 |                     |                     |                  |  |  |  |  |  |  |

|         |            | communication only when CS# is pulled low.                                                                     |                     |                     |                  |  |  |  |  |  |  |

|         |            | Power Reset for Controller and Driver                                                                          |                     |                     |                  |  |  |  |  |  |  |

| 9       | RES#       | This pin is reset signal input. When the pin is low, initialization of                                         |                     |                     |                  |  |  |  |  |  |  |

|         |            | the chip is executed.                                                                                          |                     |                     |                  |  |  |  |  |  |  |

|         |            | Data/Command (                                                                                                 |                     |                     |                  |  |  |  |  |  |  |

|         |            | This pin is Data/C                                                                                             |                     |                     |                  |  |  |  |  |  |  |

| 10      | D/C#       | the input at D0~[                                                                                              |                     |                     |                  |  |  |  |  |  |  |

|         |            | low, the input at D0~D7 will be transferred to the command                                                     |                     |                     |                  |  |  |  |  |  |  |

|         |            | register. For detail relationship to MCU interface signals, please                                             |                     |                     |                  |  |  |  |  |  |  |

|         |            | refer to the Timing Characteristics Diagrams.<br>Read/Write Select or Write                                    |                     |                     |                  |  |  |  |  |  |  |

|         |            | This pin is MCU ii                                                                                             |                     | han interfacing to  | a 68XX-series    |  |  |  |  |  |  |

|         |            |                                                                                                                |                     |                     | (R/W#) selection |  |  |  |  |  |  |

|         |            | input. Pull this pi                                                                                            |                     |                     |                  |  |  |  |  |  |  |

| 11      | R/W# (WR#) | write mode.                                                                                                    |                     |                     |                  |  |  |  |  |  |  |

|         |            | When 80XX interface mode is selected, this pin will be the Write                                               |                     |                     |                  |  |  |  |  |  |  |

|         |            | (WR#) input. Data write operation is initiated when this pin is pulled                                         |                     |                     |                  |  |  |  |  |  |  |

|         |            | low and the CS#                                                                                                |                     |                     |                  |  |  |  |  |  |  |

|         |            | Read/Write Enab                                                                                                | le or Read          |                     |                  |  |  |  |  |  |  |

|         |            | This pin is MCU ii                                                                                             | nterface input. W   | hen interfacing to  | a 68XX-series    |  |  |  |  |  |  |

| 12      | E (RD#)    | microprocessor,                                                                                                | this pin will be us | ed as the Enable    | (E) signal.      |  |  |  |  |  |  |

|         |            | Read/write opera                                                                                               |                     | /hen this pin is pu | illed high and   |  |  |  |  |  |  |

|         |            | the CS# is pulled                                                                                              | low.                |                     |                  |  |  |  |  |  |  |

|       |       | When connecting to an 80XX-microprocessor, this pin receives the Read (RD#) signal. Data read operation is initiated when this pin is pulled low and CS# is pulled low.                                                                            |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13-20 | D0-D7 | Host Data Input/Output Bus<br>These pins are 8-bit bi-directional data bus to be connected to the<br>microprocessor's data bus. When serial mode is selected, D1 will be<br>the serial data input SDIN and D0 will be the serial clock input SCLK. |

| 21    | VCOMH | Voltage Output High Level for COM Signal<br>The COM signal deselected voltage level. A tantalum capacitor<br>should be connected between this pin and VSS.                                                                                         |

| 22    | VCC   | Power Supply for OEL Panel<br>This is the most positive voltage supply pin of the chip.<br>It should be supplied externally.                                                                                                                       |

| 23    | NC    | Reserved Pin (Supporting Pin)<br>The supporting pins can reduce the influences from stresses on the<br>function pins.                                                                                                                              |

### 3.2 Module Pin Description

| Pin No. | Symbol | Function Description                                                   |

|---------|--------|------------------------------------------------------------------------|

| 1       | GND    | Ground                                                                 |

| 2       | VCC_IN | Power Supply                                                           |

|         |        | Host Data Input/Output Bus                                             |

| 3       | SCL    | These pins are 8-bit bi-directional data bus to be connected to the    |

| 4       | SDA    | microprocessor's data bus. When serial mode is selected, D1 will be    |

|         |        | the serial data input SDIN and D0 will be the serial clock input SCLK. |

|         |        | Power Reset for Controller and Driver                                  |

| 5       | RES    | This pin is reset signal input. When the pin is low, initialization of |

|         |        | the chip is executed.                                                  |

|         |        | Data/Command Control                                                   |

|         |        | This pin is Data/Command control pin. When the pin is pulled high,     |

| 6       | D/C    | the input at D0~D7 is treated as display data. When the pin is pulled  |

| 0       | DIC    | low, the input at D0~D7 will be transferred to the command             |

|         |        | register. For detail relationship to MCU interface signals, please     |

|         |        | refer to the Timing Characteristics Diagrams.                          |

|         |        | Chip Select                                                            |

| 7       | CS     | This pin is the chip select input. The chip is enabled for MCU         |

|         |        | communication only when CS# is pulled low.                             |

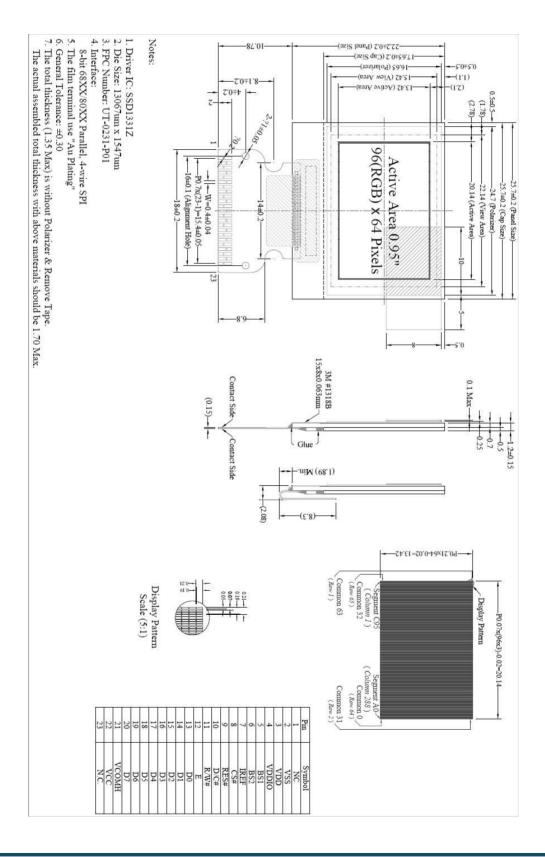

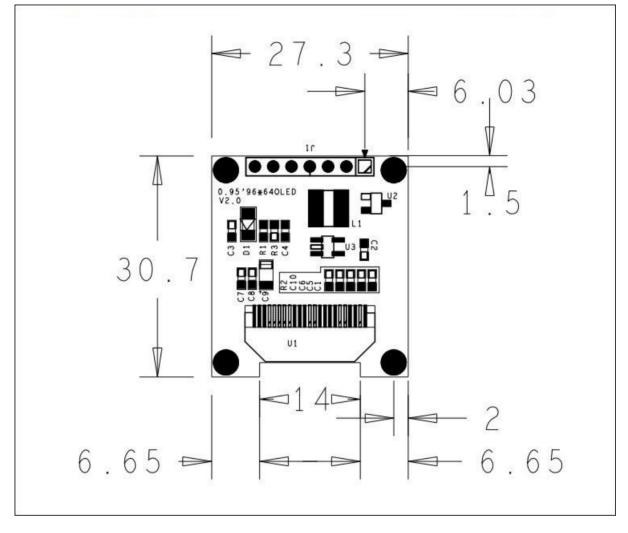

### 4 Mechanical Drawing

### 4.1 Panel Mechanical Drawing

### 4.2 Module Mechanical Drawing

### **5** Electrical Characteristics

| Item                      | Symbol          | Condition    | Min                           | Тур  | Max                           | Unit |

|---------------------------|-----------------|--------------|-------------------------------|------|-------------------------------|------|

| Supply Voltage            | VDD             |              | 2.4                           | 2.8  | 3.5                           | V    |

| Operating Current         | ICC             | Note 1       |                               | 13.5 | 18                            | mA   |

| Low Level Input Voltage   | V <sub>IL</sub> |              | 0                             | -    | 0.2xV <sub>DDIO</sub>         | V    |

| High Level Input Voltage  | V <sub>IH</sub> |              | $0.8 \times V_{DDIO}$         | -    | V <sub>DDIO</sub>             | V    |

| Low Level Output Voltage  | V <sub>OL</sub> |              | 0                             |      | $0.1 \text{xV}_{\text{DDIO}}$ | V    |

| High Level Output Voltage | V <sub>OH</sub> |              | $0.9 \text{xV}_{\text{DDIO}}$ |      | V <sub>DDIO</sub>             | V    |

| Operating Temperature     | TOP             | Absolute Max | -30                           |      | 70                            | °C   |

| Storage Temperature       | TST             | Absolute Max | -40                           |      | 80                            | °C   |

Note 1: VDD = 2.8V, VCC = 12V, IREF=910K 100% Display Area Turn on.

## **6** Optical Characteristics

| Item                 | Symbol  | Min    | Тур      | Max | Unit  |

|----------------------|---------|--------|----------|-----|-------|

| View Angles          |         | >160   | -        | -   | 0     |

| Response Time (25°C) | Tr + Tf |        |          |     | us    |

| Brightness           |         | 80     | 100      | -   | cd/m² |

| Contrast Ratio       | CR      |        | >1,000:1 |     |       |

| Lifetime             |         | 10,000 |          |     | Hrs   |

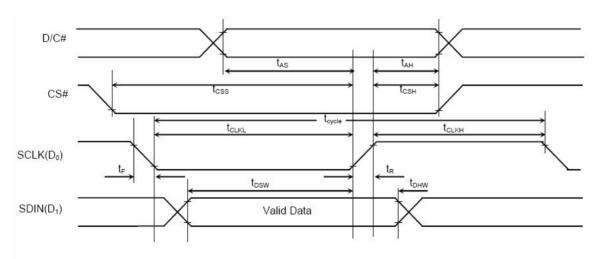

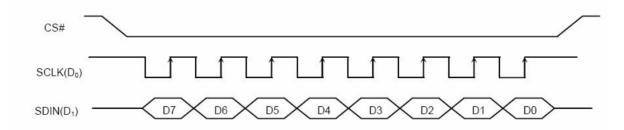

### 7 Timing Characteristics

### 7.1 Serial Interface Timing Characteristics

|                    | -                      |     | TA=25°C,VDD-VSS=1.65-3.5 |     |      |  |  |

|--------------------|------------------------|-----|--------------------------|-----|------|--|--|

| Symbol             | Item                   | Min | Тур                      | Max | Unit |  |  |

| t <sub>cycle</sub> | Clock Cycle Time       | 150 | -                        | -   | ns   |  |  |

| t <sub>AS</sub>    | Address Setup Time     | 40  | -                        | -   | ns   |  |  |

| t <sub>AH</sub>    | Address Hold Time      | 40  | -                        | -   | ns   |  |  |

| t <sub>css</sub>   | Chip Select Setup Time | 75  | -                        | -   | ns   |  |  |

| t <sub>csh</sub>   | Chip Select Hold Time  | 60  | -                        | -   | ns   |  |  |

| t <sub>DSW</sub>   | Write Data Setup Time  | 40  | -                        | -   | ns   |  |  |

| t <sub>DHW</sub>   | Write Data Hold Time   | 40  | -                        | -   | ns   |  |  |

| t <sub>clkl</sub>  | Clock Low Time         | 75  | -                        | -   | ns   |  |  |

| t <sub>clkh</sub>  | Clock High Time        | 75  | -                        | -   | ns   |  |  |

| t <sub>R</sub>     | Rise Time              | -   | -                        | 15  | ns   |  |  |

| t <sub>F</sub>     | Fall Time              | -   | -                        | 15  | ns   |  |  |

### 8 Functional Specification

#### 8.1 Power down and Power up Sequence

To protect OEL panel and extend the panel life time, the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. It gives the OEL panel enough time to complete the action of charge and discharge before/after the operation.

#### Power up Sequence

- 1. Power up V<sub>DD</sub> & V<sub>DDIO</sub>

- 2. Send Display off command

- 3. Clear Screen

- 4. Power up  $V_{cc}$

- 5. Delay 100ms (when VDD & VDDIO is stable)

- 6. Send Display on command

#### **Power down Sequence**

- 1. Send Display off command

- 2. Power down V<sub>cc</sub>

- 3. Delay 100ms (When  $V_{CC}/V_{BAT}$  is reach 0 and panel is completely discharges)

- 4. Power down  $V_{DD}$

V<sub>DD</sub>, V<sub>DDIO</sub>

### 8.2 Reset Circuit

When RES# input is low, the chip is initialized with the following status:

- 1. Display is OFF

- 2. 64 MUX Display Mode

- 3. Display start line is set at display RAM address 0

- 4. Display offset set to 0

- 5. Normal segment and display data column address and row address mapping (SEG0 mapped to address 00H and COM0 mapped to address 00H)

- 6. Column address counter is set at 0

- 7. Master contrast control register is set at 0FH

- 8. Individual contrast control registers of color A, B, and C are set at 80H

- 9. Shift register data clear in serial interface

- 10. Normal display mode (Equivalent to A4 command)

### 9 Driver/Controller Information

Built-in SSD1331 Controller:

https://drive.google.com/file/d/08\_HGldxxTS9iM2JzOWtlZWIIOGs/view?usp=sharing

# 10 Module Schematic

## **11 Example Application**

Command usage and explanation of an actual example

```

<Initialization Setting>

Set Display On/Off (1010111X)

10101110 => 0xAE (Display Off)

```

Set Display Mode (101001XX) 10100100 => 0xA4 (Normal Display Mode)

Set Display Clock Divide Ratio / Oscillator Frequency (10110011 with XXXXXXX)

```

Set Display Offset

(10100010 with XXXXXXX)

```

Set Multiplex Ratio (11001000 with XXXXXXX)

Set Master Configuration (10101101 with 1000111X) 10001110 => 0x8E (External VCC Supply Selected)

Set Display Start Line (10100001 with XXXXXXX) Set Segment Re-map & Data Format (10100000 with XXXXXXX)

Set Master Current Control (10000111 with \*\*\*\*XXXX) Set Contrast Control for Color "A" (10000001 with XXXXXXXX) Set Contrast Control for Color "B" (10000010 with XXXXXXXX) Set Contrast Control for Color "C" (10000011 with XXXXXXXX)

Set Pre-charge Level (10111011 with \*\*XXXXX) Set Second Pre-charge Speed of Color A (10001010 with XXXXXXX) Set Second Pre-charge Speed of Color B (10001011 with XXXXXXX) Set Second Pre-charge Speed of Color C (10001100 with XXXXXXX) Set VCOMH

Set Phase 1 & 2 Period Adjustment (10110001 with XXXXXXX)

Set Power Saving Mode (10110000 with 000XXXXX)

Set Display On/Off (1010111X) 10101111 => 0xAF (Display On)

<Display Boundary Setting> Set Column Address (00010101 with XXXXXXX for Start & XXXXXXX for End) Set Row Address (01110101 with XXXXXXX for Start & XXXXXXXX for End)

If the noise is accidentally occurred at the displaying window during the operation, please reset the display in order to recover the display function.

# 12 Command Table

| Fund    | damental Commands<br># Hex D7 D6 D5 D4 D3 D2 D1 D0 Command Description Default |                |                |                |                |                |                |                |                |                               |                                                                             |             |  |  |

|---------|--------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------------------------------|-----------------------------------------------------------------------------|-------------|--|--|

| D/C#    | Hex                                                                            | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             | Command                       | Description                                                                 | Default     |  |  |

| 0       | 15                                                                             | 0              | 0              | 0              | 1              | 0              | 1              | 0              | 1              |                               | Setup Column start and end address                                          |             |  |  |

| 0       | A[6:0]                                                                         | *              | A <sub>6</sub> | A <sub>5</sub> | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                               | A[6:0] start address from 00d-95d                                           | 00d (00h)   |  |  |

| 0       | B[6:0]                                                                         | *              | B <sub>6</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |                               | B[6:0] end address from 00d-95d                                             | 95d (5Fh)   |  |  |

|         |                                                                                |                |                |                |                |                |                |                |                | Set Column<br>Address         |                                                                             |             |  |  |

| 0       | 75                                                                             | 0              | 1              | 1              | 1              | 0              | 1              | 0              | 1              | -                             | Setup Row start and end address                                             |             |  |  |

| 0       | A[5:0]                                                                         | *              | *              | A <sub>5</sub> | A4             | A <sub>3</sub> | A <sub>2</sub> | A              | A              |                               | A[5:0] start address from 00d-63d                                           | 00d (00h)   |  |  |

| 0       | B[5:0]                                                                         | *              | *              | B <sub>5</sub> | 1.000          | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |                               | B[5:0] end address from 00d-63d                                             | 63d (3Fh)   |  |  |

| (Churk) |                                                                                |                |                |                |                |                |                |                |                | Set Row<br>Address            |                                                                             |             |  |  |

| 0       | 81                                                                             | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |                               | Set contrast for all color "A" segment                                      |             |  |  |

|         |                                                                                |                | Ŭ              |                |                |                |                |                |                |                               | (Pins:SA0 – SA95)                                                           |             |  |  |

| 0       | A[7:0]                                                                         | A7             | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                               | A[7:0] valid range: 00d to 255d                                             | 128d (80h)  |  |  |

|         |                                                                                |                |                |                |                |                |                |                |                | Set Contrast<br>for Color "A" |                                                                             |             |  |  |

| 0       | 82                                                                             | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | -                             | Set contrast for all color "B" segment                                      |             |  |  |

|         |                                                                                |                |                |                |                |                |                |                |                |                               | (Pins:SB0 – SB95).                                                          |             |  |  |

| 0       | A[7:0]                                                                         | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Ao             | Set Contrast<br>for Color "B" | A[7:0] valid range: 00d to 255d                                             | 128d (80h)  |  |  |

| 0       | 83                                                                             | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 1              |                               | Set contrast for all color "C" segment                                      |             |  |  |

| 0       | A[7:0]                                                                         | ^              |                |                |                |                |                |                |                |                               | (Pins:SC0 – SC95).<br>A[7:0] valid range: 00d to 255d                       | 128d (80h)  |  |  |

| 0       | A[7:0]                                                                         | A7             | A <sub>6</sub> | A5             | A <sub>4</sub> | A3             | A <sub>2</sub> | Aı             | Ao             | Set Contrast<br>for Color "C" | A[7.0] valid range. 00d to 255d                                             | 1280 (8011) |  |  |

| 0       | 87                                                                             | 1              | 0              | 0              | 0              | 0              | 1              | 1              | 1              |                               | Set master current attenuation factor                                       |             |  |  |

| 0       | A[3:0]                                                                         | 0              | 0              | 0              | 0              | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                               | A[3:0] from 00d to 15d corresponding to 1/16,<br>2/16 to 16/16 attenuation. | 15d (0Fh)   |  |  |

|         |                                                                                |                |                |                |                |                |                |                |                | Master Current<br>Control     |                                                                             |             |  |  |

# DisplayModule

| Fund | amenta                                       | I Co                                                              | mm                                                                | and          | s       |                                                                   |                                                                   |                                    |                                                    |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

|------|----------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|--------------|---------|-------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| D/C# | Hex                                          | -                                                                 |                                                                   | 1            | D4      | D3                                                                | D2                                                                | D1                                 | D0                                                 | Command                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Default                                         |

|      | 8A<br>A[7:0]<br>8B<br>A[7:0]<br>8C<br>A[7:0] | 1<br>A <sub>7</sub><br>1<br>A <sub>7</sub><br>1<br>A <sub>7</sub> | 0<br>A <sub>6</sub><br>0<br>A <sub>6</sub><br>0<br>A <sub>6</sub> | 0<br>A5<br>0 | 0       | 1<br>A <sub>3</sub><br>1<br>A <sub>3</sub><br>1<br>A <sub>3</sub> | 0<br>A <sub>2</sub><br>0<br>A <sub>2</sub><br>1<br>A <sub>2</sub> | 1<br>A1<br>1<br>A1<br>0<br>A1      | 0 A <sub>0</sub> 1 A <sub>0</sub> 0 A <sub>0</sub> | Set Second<br>Pre-charge<br>Speed for<br>Color "A", "B"<br>and "C" | A[7:0]: Set Second Pre-charge Speed<br>Ranges: 000000b to 111111b,<br>a higher value of A[7:0] gives a higher Second<br>Pre-charge speed.<br>Note<br>(1) The default values of A[7:0] in 8Ah, A[7:0]<br>in 8Bh and A[7:0] in 8Ch are equal to the<br>contrast values for color A, B and C( refer<br>to commands: 81h, 82h, 83h) respectively.<br>(2) All six bytes (8Ah A[7:0], 8Bh A[7:0] and<br>8Ch A[7:0]) must be inputted together. For<br>example: the original value is like that<br>Original value<br>8Ah A[7:0]: 80h<br>8Bh A[7:0]: 80h<br>If it is wanted to change the value of 8Bh<br>A[7:0] to 75h, then all the following 6 bytes<br>must be inputted:<br>8Ah, 80h,<br>8Bh, 75h,<br>8Ch, 80h. | A[7:0] of 81h<br>A[7:0] of 82h<br>A[7:0] of 83h |

| 0    | A0<br>A[7:0]                                 | 1<br>A7                                                           | 0<br>A <sub>6</sub>                                               | 1<br>A5      | 0<br>A4 | 0<br>A3                                                           | 0<br>A2                                                           | 0<br>A1                            | 0<br>40                                            |                                                                    | Set driver remap and color depth<br>A[0]=0, Horizontal address increment<br>A[0]=1, Vertical address increment<br>A[1]=0, RAM Column 0 to 95 maps to Pin Seg<br>(SA,SB,SC) 0 to 95<br>A[1]=1, RAM Column 0 to 95 maps to Pin Seg<br>(SA,SB,SC) 95 to 0<br>A[2]=0, normal order SA,SB,SC (e.g. RGB)<br>A[2]=1, reverse order SC,SB,SA (e.g. BGR)                                                                                                                                                                                                                                                                                                                                                             |                                                 |

|      |                                              |                                                                   |                                                                   |              |         |                                                                   |                                                                   | 2 5<br>2 5<br>2 50<br>2 50<br>2 50 |                                                    | Remap & Color<br>Depth setting                                     | A[3]=0, Disable left-right swapping on COM<br>A[3]=1, Set left-right swapping on COM<br>A[4]=0, Scan from COM 0 to COM [N –1]<br>A[4]=1, Scan from COM [N-1] to COM0.<br>Where N is the multiplex ratio.<br>A[5]=0, Disable COM Split Odd Even<br>(RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A[3]=0<br>A[4]=0<br>A[5]=0                      |

|      |                                              |                                                                   |                                                                   |              |         |                                                                   |                                                                   |                                    |                                                    |                                                                    | A[5]=1, Enable COM Split Odd Even<br>A[7:6] = 00; 256 color format<br>A[7:6] = 01; 65k color format<br>A[7:6] = 10; 65k color format 2<br>If 9 / 18 bit mode is selected, color depth will<br>be fixed to 65k regardless of the setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A[7:6]=01                                       |

| 0    | A1<br>A[5:0]                                 | 1                                                                 | 0                                                                 | 1<br>A5      | 0<br>A4 | 0<br>A3                                                           | 0<br>A2                                                           | 0<br>A1                            | 1<br>A <sub>0</sub>                                | Set Display<br>Start Line                                          | Set display start line register by Row<br>A[5:0]: from 00d to 63d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00d (00h)                                       |

| 0    | A2<br>A[5:0]                                 | 1                                                                 | 0                                                                 | 1<br>A5      | 0<br>A4 | 0<br>A3                                                           | 0<br>A2                                                           | 1<br>A1                            | 0<br>A0                                            | Set Display<br>Offset                                              | Set vertical offset by Com<br>A[5:0]: from 00d to 63d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00d (00h)                                       |

| Fund             | amenta                                               |                                                                                | mm                                                                             | and                                                                            | s                               |                                                    |                                 |                     |                                                                                             |                                                       |                                                                                                                                                                                                                                                                                                                                           |           |

|------------------|------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------|---------------------------------|---------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| D/C#             | Hex                                                  | -                                                                              |                                                                                | D5                                                                             | _                               | D3                                                 | D2                              | D1                  | D0                                                                                          | Command                                               | Description                                                                                                                                                                                                                                                                                                                               | Default   |

| 0<br>0<br>0<br>0 | A4 /<br>A5 /<br>A6 /<br>A7 /                         | 1                                                                              | 0                                                                              | 1                                                                              | 0                               | 0                                                  | 1                               | X <sub>1</sub>      | Xo                                                                                          | Set Display<br>Mode                                   | A4h=Normal Display<br>A5h=Entire Display On, all pixels turn on at<br>GS63<br>A6h=Entire Display Off, all pixels turn off<br>A7h=Inverse Display                                                                                                                                                                                          | A4h       |

| 0                | A8<br>A[5:0]                                         | 1<br>0                                                                         | 0                                                                              | 1<br>A5                                                                        | 0<br>A4                         | 1<br>A <sub>3</sub>                                | 0<br>A2                         | 0<br>A1             | 0<br>A0                                                                                     | Set Multiplex<br>Ratio                                | Set MUX ratio to N+1 Mux<br>N = A[5:0] from 15d to 63d<br>A[5:0] from 00d to 14d are invalid entry                                                                                                                                                                                                                                        | 63d (3Fh) |

|                  | AB<br>A[7:0]<br>B[7:0]<br>C[7:0]<br>D[7:0]<br>E[4:0] | 1<br>A <sub>7</sub><br>B <sub>7</sub><br>C <sub>7</sub><br>D <sub>7</sub><br>0 | 0<br>A <sub>6</sub><br>B <sub>6</sub><br>C <sub>6</sub><br>D <sub>6</sub><br>0 | 1<br>A <sub>5</sub><br>B <sub>5</sub><br>C <sub>5</sub><br>D <sub>5</sub><br>0 | 0<br>A4<br>B4<br>C4<br>D4<br>E4 | B <sub>3</sub><br>C <sub>3</sub><br>D <sub>3</sub> | 0<br>A2<br>B2<br>C2<br>D2<br>E2 |                     | 1<br>A <sub>0</sub><br>B <sub>0</sub><br>C <sub>0</sub><br>D <sub>0</sub><br>E <sub>0</sub> | Dim Mode<br>Setting                                   | Configure dim mode setting<br>A[7:0] = Reserved. (Set as 00h)<br>B[7:0] = Contrast setting for Color A, valid<br>range 0 to 255d.<br>C[7:0] = Contrast setting for Color B, valid<br>range 0 to 255d.<br>D[7:0] = Contrast setting for Color C, valid<br>range 0 to 255d.<br>E[4:0] = Precharge voltage setting, valid<br>range 0 to 31d. |           |

| 0                | AD<br>A[0]                                           | 1                                                                              | 0                                                                              | 1<br>0                                                                         | 0                               | 1                                                  | 1                               | 0                   | 1<br>A <sub>0</sub>                                                                         | Set Master<br>Configuration                           | A[0]=0b, Select external V <sub>CC</sub> supply<br>A[0]=1b, Reserved (RESET)<br>Note<br><sup>(1)</sup> Bit A[0] must be set to 0b after RESET.<br><sup>(2)</sup> The setting will be activated after issuing<br>Set Display ON command (AFh)                                                                                              | A[0] = 1  |

| 0                | AC<br>AE<br>AF                                       | 1                                                                              | 0                                                                              | 1                                                                              | 0                               | 1                                                  | 1                               | A <sub>1</sub>      | A                                                                                           | Set Display<br>On/Off                                 | ACh = Display ON in dim mode<br>AEh = Display off (sleep mode)<br>AFh = Display on in normal mode                                                                                                                                                                                                                                         | AEh       |

| 0                | B0<br>A[7:0]                                         | 1<br>A <sub>7</sub>                                                            | 0<br>A <sub>6</sub>                                                            | 1<br>A5                                                                        | 1<br>A4                         | 0<br>A <sub>3</sub>                                | 0<br>A <sub>2</sub>             | 0<br>A <sub>1</sub> | 0<br>A <sub>0</sub>                                                                         | Power Save<br>Mode                                    | A[7:0]=1Ah, Enable Power save mode<br>(RESET)<br>A[7:0]=0Bh, Disable Power save mode                                                                                                                                                                                                                                                      | 1Ah       |

| 0                | B1<br>A[7:0]                                         | 1<br>A7                                                                        | 0<br>A <sub>6</sub>                                                            | 1<br>A5                                                                        | 1<br>A4                         | 0<br>A3                                            | 0<br>A2                         | 0<br>A1             | 1<br>A <sub>0</sub>                                                                         | Phase 1 and 2<br>period<br>adjustment                 | A[3:0] Phase 1 period in N DCLK. 1~15<br>DCLK allowed.<br>A[7:4] Phase 2 period in N DCLK. 1~15<br>DCLK allowed                                                                                                                                                                                                                           | 74h       |

| 0                | B3<br>A[7:0]                                         | 1<br>A7                                                                        | 0<br>A <sub>6</sub>                                                            | 1<br>A5                                                                        | 1<br>A4                         | 0<br>A <sub>3</sub>                                | 0<br>A2                         | 1<br>A <sub>1</sub> | 1<br>A <sub>0</sub>                                                                         | Display Clock<br>Divider /<br>Oscillator<br>Frequency | A[3:0]: Define the divide ratio (D) of the<br>display clocks (DCLK):<br>Divide ratio (D) = A[3:0] + 1 (i.e., 1 to 16)<br>A[7:4] Fosc frequency.<br>Frequency increases as setting value<br>increases                                                                                                                                      | D0h       |

# DisplayModule

#### DM-OLED095-626

| Fund | amenta                                          |          | mm                  | and                 | s                                                       |                                                             |                                                             |                     |                                                         |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

|------|-------------------------------------------------|----------|---------------------|---------------------|---------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|---------------------|---------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| D/C# | Hex                                             |          |                     | D5                  | _                                                       | D3                                                          | D2                                                          | D1                  | D0                                                      | Command                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default |

|      | B8<br>A[6:0]<br>B[6:0]<br>C[6:0]<br><br>AE[6:0] | 1 * * ** | 0<br>A6<br>B6<br>C6 | 1<br>A5<br>B5<br>C5 | 1<br>A <sub>4</sub><br>B <sub>4</sub><br>C <sub>4</sub> | 1<br>A <sub>3</sub><br>B <sub>3</sub><br>C <sub>3</sub><br> | 0<br>A <sub>2</sub><br>B <sub>2</sub><br>C <sub>2</sub><br> | 0<br>A1<br>B1<br>C1 | 0<br>A <sub>0</sub><br>B <sub>0</sub><br>C <sub>0</sub> | Set Gray Scale<br>Table              | These 32 parameters define pulse widths of<br>GS1 to GS63 in terms of DCLK<br>A[6:0]: Pulse width for GS1, RESET=01d<br>B[6:0]: Pulse width for GS3, RESET=05d<br>C[6:0]: Pulse width for GS5, RESET=09d<br><br>AE[6:0]: Pulse width for GS61, RESET=121d<br>AF[6:0]: Pulse width for GS63, RESET=125d<br>Note:<br><sup>(1)</sup> GS0 has no pre-charge and current drive<br>stages.<br><sup>(2)</sup> GS2, GS4GS62 are derived by<br>Pn = (Pn-1+Pn+1)/2<br><sup>(3)</sup> Pn will be truncated to integer if it is with<br>decimal point.<br><sup>(4)</sup> Pn+1 should always be set to larger than<br>Pn-1<br><sup>(5)</sup> Max pulse width is 125 | λ       |

| 0    | B9                                              | 1        | 0                   | 1                   | 1                                                       | 1                                                           | 0                                                           | 0                   | 1                                                       | Enable Linear<br>Gray Scale<br>Table | Reset built in gray scale table (Linear)<br>Pulse width for GS1 = 1d;<br>Pulse width for GS2 = 3d;<br>Pulse width for GS3 = 5d;<br><br>Pulse width for GS61 = 121d;<br>Pulse width for GS62 = 123d;<br>Pulse width for GS63 = 125d.                                                                                                                                                                                                                                                                                                                                                                                                                    | 1       |

| 0    | BB<br>A[5:0]                                    | 1        | 0                   | 1<br>A5             | 1<br>A4                                                 | 1<br>A <sub>3</sub>                                         | 0<br>A <sub>2</sub>                                         | 1<br>A1             | 1                                                       | Set Pre-charge<br>level              | Set pre-charge voltage level. All three color share the same pre-charge voltage.         A[5:1]       Hex code pre-charge voltage         00000       00h       0.10 x V <sub>CC</sub> :       :       :         11111       3Eh       0.50 x V <sub>CC</sub> Refer to Figure 31 for the details setting of A[5:1].                                                                                                                                                                                                                                                                                                                                    | 3Eh     |

| 0    | BC-BD                                           | 1        | 0                   | 1                   | 1                                                       | 1                                                           | 1                                                           | 0                   | X <sub>0</sub>                                          | NOP                                  | Command for No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ١       |

| 0    | BE<br>A[5:1]                                    | 1<br>0   | 0                   | 1<br>A5             | 1<br>A4                                                 | 1<br>A3                                                     | 1<br>A2                                                     | 1<br>A1             | 0                                                       | Set V <sub>COMH</sub>                | A[5:1]         Hex code         V сомн           00000         00h         0.44 x V <sub>CC</sub> 01000         10h         0.52 x V <sub>CC</sub> 10000         20h         0.61 x V <sub>CC</sub> 11000         30h         0.71 x V <sub>CC</sub> 11111         3Eh         0.83 x V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                  | 3Eh     |

| 0    | E3                                              | 1        | 1                   | 1                   | 0                                                       | 0                                                           | 0                                                           | 1                   | 1                                                       | NOP                                  | Command for No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ١       |

| 0    | FD<br>A[2]                                      | 1        | 1                   | 1<br>0              | 1                                                       | 1                                                           | 1<br>A2                                                     | 0                   | 1                                                       | Set Command<br>Lock                  | <ul> <li>A[2]: MCU protection status</li> <li>A[2] = 0b, Unlock OLED driver IC MCU interface from entering command [reset]</li> <li>A[2] = 1b, Lock OLED driver IC MCU interface from entering command</li> <li>Note         <sup>(1)</sup> The locked OLED driver IC MCU interface prohibits all commands and memory access except the FDh command.</li> </ul>                                                                                                                                                                                                                                                                                        | 12h     |

| Grap                                                 | Graphic Acceleration Commands |   |                |                |                |                |                |                |                |                          |                                               |

|------------------------------------------------------|-------------------------------|---|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--------------------------|-----------------------------------------------|

| D/C# Hex D7 D6 D5 D4 D3 D2 D1 D0 Command Description |                               |   |                |                |                |                |                |                |                |                          |                                               |

| 0                                                    | 21                            | 0 | 0              | 1              | 0              | 0              | 0              | 0              | 1              |                          | A[6:0]: Column Address of Start               |

| 0                                                    | A[6:0]                        | * | A <sub>6</sub> | A <sub>5</sub> | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                          | B[5:0]: Row Address of Start                  |

| 0                                                    | B[5:0]                        | * | *              | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |                          | C[6:0]: Column Address of End                 |

| 0                                                    | C[6:0]                        | * | C <sub>6</sub> | C <sub>5</sub> | C4             | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> | Drawline                 | D[5:0]: Row Address of End                    |

| 0                                                    | D[5:0]                        | * | *              | D <sub>5</sub> | D4             | D <sub>3</sub> | D <sub>2</sub> | D1             | D <sub>0</sub> | Draw Line                | E[5:1]: Color C of the line                   |

| 0                                                    | E[5:1]                        | * | *              | E <sub>5</sub> | E4             | E <sub>3</sub> | E <sub>2</sub> | E1             | *              |                          | F[5:0]: Color B of the line                   |

| o                                                    | F[5:0]                        | * | *              | F <sub>5</sub> | F₄             | F <sub>3</sub> | F <sub>2</sub> | F1             | Fo             |                          | G[5:1]: Color A of the line                   |

| 0                                                    | G[5:1]                        | * | *              | G5             | G4             | G <sub>3</sub> | G <sub>2</sub> | G1             | *              |                          |                                               |

| 0                                                    | 22                            | 0 | 0              | 1              | 0              | 0              | 0              | 1              | 0              |                          | A[6:0]: Column Address of Start               |

| 0                                                    | A[6:0]                        | * | A <sub>6</sub> | A <sub>5</sub> | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                          | B[5:0]: Row Address of Start                  |

| 0                                                    | B[5:0]                        | * | *              | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |                          | C[6:0]: Column Address of End                 |

| 0                                                    | C[6:0]                        | * | C <sub>6</sub> | C <sub>5</sub> | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> |                          | D[5:0]: Row Address of End                    |

| 0                                                    | D[5:0]                        | * | *              | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | $D_2$          | D <sub>1</sub> | D <sub>0</sub> |                          | E[5:1]: Color C of the line                   |

| 0                                                    | E[5:1]                        | * | *              | E <sub>5</sub> | E4             | E <sub>3</sub> | E <sub>2</sub> | E1             | *              | Drawing<br>Rectangle     | F[5:0]: Color B of the line                   |

| 0                                                    | F[5:0]                        | * | *              | F <sub>5</sub> | F4             | F <sub>3</sub> | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub> | Rectangle                | G[5:1]: Color A of the line                   |

| 0                                                    | G[5:1]                        | * | *              | G <sub>5</sub> | G4             | G <sub>3</sub> | G <sub>2</sub> | G1             | *              |                          | H[5:1]: Color C of the fill area              |

| 0                                                    | H[5:1]                        | * | *              | H <sub>5</sub> | H <sub>4</sub> | H <sub>3</sub> | H <sub>2</sub> | H <sub>1</sub> | *              |                          | I[5:0]: Color B of the fill area              |

| 0                                                    | I[5:0]                        | * | *              | 15             | 14             | 13             | 12             | 11             | 10             |                          | J[5:1]: Color A of the fill area              |

| 0                                                    | J[5:1]                        | * | *              | J <sub>5</sub> | J4             | $J_3$          | J <sub>2</sub> | J <sub>1</sub> | *              |                          |                                               |

| 0                                                    | 23                            | 0 | 0              | 1              | 0              | 0              | 0              | 1              | 1              |                          | A[6:0]: Column Address of Start               |

| 0                                                    | A[6:0]                        | * | A <sub>6</sub> | As             | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                          | B[5:0]: Row Address of Start                  |

| 0                                                    | B[5:0]                        | * | *              | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> | _                        | C[6:0]: Column Address of End                 |

| 0                                                    | C[6:0]                        | * | C <sub>6</sub> | C <sub>5</sub> | C4             | C <sub>3</sub> |                | C1             | Co             | Сору                     | D[5:0]: Row Address of End                    |

| 0                                                    | D[5:0]                        | * | *              | D <sub>5</sub> |                | D <sub>3</sub> | D <sub>2</sub> | D1             | Do             |                          | E[6:0]: Column Address of New Start           |

| 0                                                    | E[6:0]                        | * | E <sub>6</sub> | E <sub>5</sub> | E4             | E <sub>3</sub> | E <sub>2</sub> | E1             | E <sub>0</sub> |                          | F[5:0]: Row Address of New Start              |

| 0                                                    | F[5:0]                        | * | *              | F <sub>5</sub> |                | F <sub>3</sub> | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub> |                          |                                               |

| 0                                                    | 24                            | 0 | 0              | 1              | 0              | 0              | 1              | 0              | 0              |                          | A[6:0]: Column Address of Start               |

| 0                                                    | A[6:0]                        | * | A <sub>6</sub> | A <sub>5</sub> | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                          | B[5:0]: Row Address of Start                  |

| 0                                                    | B[5:0]                        | * | *              | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |                          | C[6:0]: Column Address of End                 |

| 0                                                    | C[6:0]                        | * | C <sub>6</sub> | C <sub>5</sub> | C4             | C <sub>3</sub> | C <sub>2</sub> | C1             | C <sub>0</sub> |                          | D[5:0]: Row Address of End                    |

| 0                                                    | D[5:0]                        | * | *              | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |                          | The effect of dim window:                     |

|                                                      |                               |   |                |                | S              |                |                |                |                | Dim Window               | GS15~GS0 no change                            |

|                                                      | 2                             |   |                |                |                |                |                |                |                |                          | GS19~GS16 become GS4                          |

| 6                                                    |                               |   |                |                |                |                |                |                |                |                          | GS23~GS20 become GS5                          |

| 2                                                    |                               |   |                |                |                |                |                |                |                |                          |                                               |

| 5                                                    | Ÿ.                            |   |                |                |                |                |                |                |                |                          | GS63~GS60 become GS15                         |

| 0                                                    | 25                            | 0 | 0              | 1              | 0              | 0              | 1              | 0              | 1              |                          | A[6:0]: Column Address of Start               |

| 0                                                    | A[6:0]                        | * | A              | As             | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                          | B[5:0]: Row Address of Start                  |

| 0                                                    | B[5:0]                        | * | *              | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> | Clear Window             | C[6:0]: Column Address of End                 |

| 0                                                    | C[6:0]                        | * | C <sub>6</sub> | C <sub>5</sub> |                | C <sub>3</sub> |                | C <sub>1</sub> | C <sub>0</sub> |                          | D[5:0]: Row Address of End                    |

| 0                                                    | D[5:0]                        | * | *              | D <sub>5</sub> |                | D <sub>3</sub> |                | D1             | D <sub>0</sub> |                          |                                               |

| 0                                                    | 26                            | 0 | 0              | 1              | 0              | 0              | 1              | 1              | 0              |                          | A0 0 : Disable Fill for Draw Rectangle        |

|                                                      |                               |   | 1000           |                |                |                |                |                | 252            |                          | Command (RESET)                               |

| 0                                                    | A[4:0]                        | * | *              | *              | A4             | 0              | 0              | 0              | A              | Fill Enable /<br>Disable | 1 : Enable Fill for Draw Rectangle<br>Command |

|                                                      |                               |   |                |                |                |                |                |                |                |                          | A[3:1] 000: Reserved values                   |

| 8                                                    | 5                             |   | 8 8            |                | 2 3            |                | 2 3            |                | Q 8            | Disable                  | A4 0 : Disable reverse copy (RESET)           |

|                                                      |                               |   | S 3            |                | 8 3            |                | 3 3            |                | S 2            |                          | 1 : Enable reverse during copy                |

| 2                                                    |                               |   |                |                |                |                |                |                |                |                          | command.                                      |