## Technical Datasheet

# Graphene Field-Effect Transistor Chip: S30/5nm

#### General Description

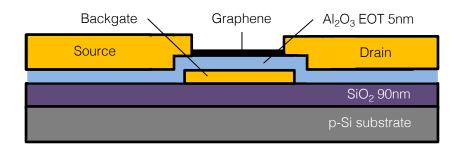

The GFET-S30/5nm chip from Graphenea provides 30 backgated graphene devices distributed in a grid pattern on the chip. All the 30 devices have a 3-probe geometry, leveraging Graphenea's proprietary High-K Metal Gate (HKMG) process flow to provide a backgate with an EOT = 5nm. This scheme allows for individual control of the conductance of each of the graphene channels within the die. There are 3 graphene channel dimensions to allow investigation of size dependence on device properties, enabling immediate optimization.

Because the device isn't passivated, it can still be functionalized or combined with other materials to exploit heterostructures suitable for sensing, specially in the fields of optoelectronics and photonics. The backgate electrode can be as well used as a heating element via Joule-heating for temperature-dependent measurements, which can be beneficial in biosensing research and applications.

#### **Features**

- Local gating enables individual device control. Heating enables temperature-dependent measurements

- Aggresive dielectric scaling via HKMG allows for low-power operation (<5V)</li>

- Devices not encapsulated, ready for your functionalization

- 30 individual GFETs per chip, with different sizes for optimization

- Mobilities typically in excess of 600 cm<sup>2</sup>/V·s

### **Applications**

- · Graphene device research

- Optoelectronics

- Photodetectors

- Photonics

- Optical modulators

- Biosensors

# Typical Specifications

| Chip dimensions                | 10 mm x 10 mm                  |  |  |

|--------------------------------|--------------------------------|--|--|

| Chip thickness                 | 525 μm                         |  |  |

| Number of channels per chip    | 30                             |  |  |

| Gate Oxide thickness (EOT)     | 5 nm                           |  |  |

| Gate Oxide material            | Al <sub>2</sub> O <sub>3</sub> |  |  |

| Dielectric breakdown           | > 13 kV/mm                     |  |  |

| Metallization                  | Au contacts                    |  |  |

| Graphene field-effect mobility | > 600 cm <sup>2</sup> /V·s     |  |  |

| Dirac point                    | < 5 V                          |  |  |

| Yield                          | > 75 %                         |  |  |

### Absolute Maximum Ratings

| Maximum gate-source voltage          | ± 5 V                              |

|--------------------------------------|------------------------------------|

| Maximum temperature rating           | 150 °C                             |

| Maximum drain-source current density | 10 <sup>7</sup> A·cm <sup>-2</sup> |

www.graphenea.com

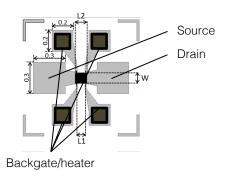

#### **GFET-S30 Layout**

#### **Channel geometries**

| Description | W<br>(µm) | L1<br>(μm) | L2<br>(μm) | QTY |

|-------------|-----------|------------|------------|-----|

| Small       | 50        | 30         | 50         | 18  |

| Medium      | 100       | 75         | 100        | 6   |

| Large       | 200       | 175        | 200        | 6   |

#### **Device cross-section**

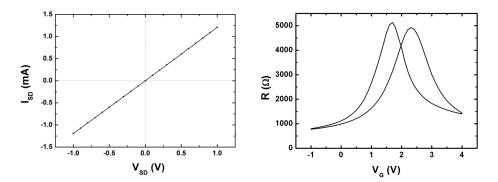

### **Typical characteristics**

Output curve (left) and transfer curve measured at source-drain voltage of 20mV (right), measured at room temperature and vacuum conditions on a device with W=L=50  $\mu$ m.