# Measurement Protocols and Handling Instructions

## Graphene Field-Effect Transistor Chip: GFET-S30/5nm

## Typical Measurement Configurations

The following explains the electrical measurements that can be performed on the different devices in GFET-S30.

#### Measurement type

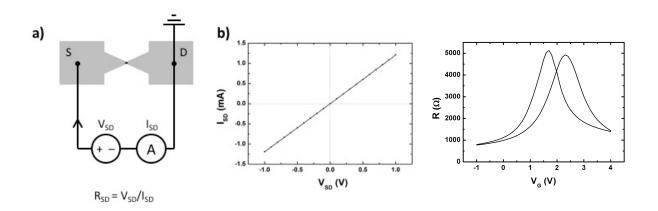

These devices allow field-effect measurements by simultaneously applying two voltages:

- Source-drain voltage (V<sub>SD</sub>): applied between the two probes (source and drain), while one of them is

grounded (see Figure 1a). V<sub>SD</sub> enables the transport of charge carriers through the graphene

channel, with an associated source-drain current (I<sub>SD</sub>). V<sub>SD</sub> can be varied in order to get the desired

I<sub>SD</sub> outcome (see Figure 1b).

- Gate voltage (V<sub>G</sub>): applied to the backgate contact. V<sub>G</sub> creates an electric field on the graphene channel, modulating the conductivity of graphene (see Figure 1c).

Alternatively, the Si substrate can be contacted either from the top surface by scratching the 90 nm-thick  $SiO_2$  with a diamond pen in one of the chip corners; or alternatively from the underside of the chip, for instance using a probe station chuck, and carry out

Figure 1. a) Scheme of the 2-probe device, with the corresponding electrical measurement configuration. b) Typical output curve measured at room temperature and vacuum conditions. c) Typical transfer curve measured at  $V_{SD}$ = 20mV (right), measured at the same conditions as in b).

#### 3-probe measurements

#### Field-effect measurement through backgate

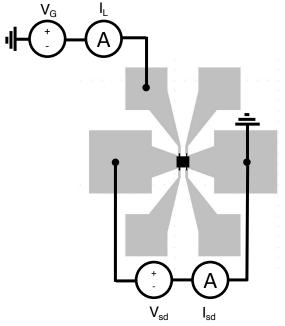

With the S30 die, local gating can be achieved through the 3-probe measurement scheme (see Figure 2). The method is to apply a source-drain voltage ( $V_{sd}$ ) between two outer contacts, measure the current between those two contacts ( $I_{sd}$ ) and additionally apply a gate voltage ( $V_{G}$ ) through the backgate electrode while monitoring the leakage current ( $I_{L}$ ). The benefit of this is that the resistance of the graphene channel alone can be tuned with a voltage, and this can be done contacting a pad and not the substrate itself which eases integration.

Due to the aggressive scaling of the gate dielectric, the device can be operated within a 5V window which is  $\approx 10$  times less operation voltage than using the substrate as a backgate.

Figure 2. Scheme of the 3-probe measurement in a device, with the corresponding electrical measurement configuration.

The resistivity of graphene is usually expressed per thickness unit, i.e. the so-called sheet resistance:

$$R_S = R_{CH} \frac{W}{L},$$

being  $R_{CH}$  the resistance of the graphene channel, and W and L the width and inner length of the graphene channel, respectively. The field-effect mobility ( $\mu_{FE}$ ) can be calculated by using the following equation:

$$\mu_{FE} = g \cdot \frac{1}{C_{gate}},$$

where:

- $g = d\sigma/dV_G$  is the transconductance, being  $\sigma=1/R_S$ ,

- C<sub>gate</sub> is the capacitance per unit area of the gate dielectric.

$\mu_{\text{\tiny EE}}$  is usually calculated using the maximum transconductance.

#### 4-probe measurements

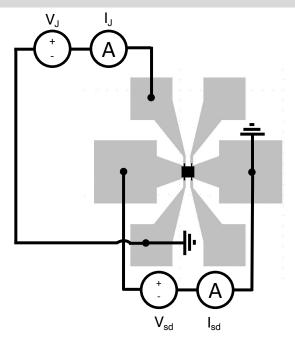

An alternative measurement scheme (see Figure 3) is to apply a source-drain voltage ( $V_{sd}$ ) between two outer contacts, measure the current between those two contacts ( $I_{sd}$ ) and additionally apply a voltage ( $V_J$ ) through the backgate electrodes while monitoring the heating current ( $I_J$ ).

This current  $I_J$  will generate heat by Joule effect, effectively heating the graphene channels which sits on top. This can be used to carry out temperature dependent measurements.

Figure 3. Scheme of the 4-probe measurement in a device, with the corresponding electrical measurement configuration.

#### Doping-reduction treatment

Graphene on  $SiO_2$  is often p-doped after exposure to air due to the adsorption of water molecules and other adsorbates with the effect that the Dirac point is shifted to positive gate voltages and can cause the Dirac voltage to be located out of the recommended gate voltage range. In addition, a large hysteresis is observed between the forward and backward sweeps of a transfer curve.

Immersing the GFET chip in acetone for at least 12h reduces doping. After that, the chip should be rinsed with IPA, properly dried with an Ar or  $N_2$  gun, and shortly introduced into the measurement equipment. In order to preserve the effectivity of this treatment, electrical characterization should be carried out in inert atmosphere or vacuum.

In addition, storage of the chips in a low humidity environment ( $N_2$  cabinet, desiccator, or vacuum) is highly recommended.

### Basic handling instructions

The graphene used in our GFETs is high-quality monolayer CVD graphene and highly prone to damage by external factors. To maintain the quality of your devices, we recommend taking the following precautions:

- Be careful when handling the GFET chip that tweezers do not make contact with the device area. Metallic tweezers should be avoided, as they can damage/scratch the chip edges/surface

- Treat the devices as sensitive electronic devices and take precautions against electrostatic discharge

- Ideally store in inert atmosphere or under vacuum in order to minimize adsorption of unknown species from the ambient air

- · Do not ultrasonicate the GFET dies

- Do not apply any plasma treatment to the GFET dies

- Do not subject the GFET dies to strongly oxidizing reagents

**Disclaimer**: Graphenea SA believes that the information in this instruction is accurate and represents the best and most current information available to us. Graphenea makes no representations or warranties either express or implied, regarding the suitability of the material for any purpose or the accuracy of the information contained within this document. Accordingly, Graphenea will not be responsible for damages resulting from use of or reliance upon this information.