# EG21-G Hardware Design

**LTE Standard Module Series**

Rev. EG21-G\_Hardware\_Design\_V1.1

Date: 2020-04-10

Status: Released

www.quectel.com

## Our aim is to provide customers with timely and comprehensive service. For any assistance, please contact our company headquarters:

#### **Quectel Wireless Solutions Co., Ltd.**

Building 5, Shanghai Business Park Phase III (Area B), No.1016 Tianlin Road, Minhang District, Shanghai, China 200233 Tel: +86 21 5108 6236 Email: <u>info@quectel.com</u>

## Or our local office. For more information, please visit: http://www.quectel.com/support/sales.htm

For technical support, or to report documentation errors, please visit: http://www.quectel.com/support/technical.htm Or email to: <a href="mailto:support@quectel.com">support@quectel.com</a>

#### **GENERAL NOTES**

QUECTEL OFFERS THE INFORMATION AS A SERVICE TO ITS CUSTOMERS. THE INFORMATION PROVIDED IS BASED UPON CUSTOMERS' REQUIREMENTS. QUECTEL MAKES EVERY EFFORT TO ENSURE THE QUALITY OF THE INFORMATION IT MAKES AVAILABLE. QUECTEL DOES NOT MAKE ANY WARRANTY AS TO THE INFORMATION CONTAINED HEREIN, AND DOES NOT ACCEPT ANY LIABILITY FOR ANY INJURY, LOSS OR DAMAGE OF ANY KIND INCURRED BY USE OF OR RELIANCE UPON THE INFORMATION. ALL INFORMATION SUPPLIED HEREIN IS SUBJECT TO CHANGE WITHOUT PRIOR NOTICE.

## COPYRIGHT

THE INFORMATION CONTAINED HERE IS PROPRIETARY TECHNICAL INFORMATION OF QUECTEL WIRELESS SOLUTIONS CO., LTD. TRANSMITTING, REPRODUCTION, DISSEMINATION AND EDITING OF THIS DOCUMENT AS WELL AS UTILIZATION OF THE CONTENT WITHOUT PERMISSION ARE FORBIDDEN. OFFENDERS WILL BE HELD LIABLE FOR PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT OF A PATENT GRANT OR REGISTRATION OF A UTILITY MODEL OR DESIGN.

Copyright © Quectel Wireless Solutions Co., Ltd. 2020. All rights reserved.

## **About the Document**

## **Revision History**

| Version | Date       | Author                   | Description                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------|------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1.0     | 2019-11-19 | Lorry XU/<br>Ethan SHAN  | Initial                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 1.1     | 2020-04-10 | Ward WANG/<br>Ethan SHAN | <ol> <li>Updated current consumption and GNSS current<br/>consumption (Table 33 and 34).</li> <li>Updated notes (Chapter 6.5).</li> <li>Added the note about the standard that the package<br/>warpage level of the module conforms to (Chapter<br/>7.1).</li> <li>Updated module storage information (Chapter 8.1).</li> <li>Updated module manufacturing and soldering<br/>information (Chapter 8.2).</li> </ol> |  |  |  |  |

## Contents

| Abo | out the | Docume     | nt                                                         | 2  |

|-----|---------|------------|------------------------------------------------------------|----|

| Cor | ntents. |            |                                                            |    |

|     |         |            |                                                            |    |

| Fig | ure Ind | lex        |                                                            | 7  |

| 1   | Introd  | uction     |                                                            | 9  |

|     | 1.1.    | Safety I   | nformation                                                 |    |

| 2   | Produ   | ict Conce  | ept                                                        | 11 |

| 2   | 2.1.    |            | Description                                                |    |

|     | 2.2.    |            | atures                                                     |    |

|     | 2.3.    | ,          | nal Diagram                                                |    |

|     | 2.4.    |            | ion Board                                                  |    |

| 3   | Applic  | cation Int | erfaces                                                    | 16 |

| Ŭ   | 3.1.    |            | Description                                                |    |

|     | 3.2.    |            | ignment                                                    |    |

|     | 3.3.    | Pin Des    | cription                                                   |    |

|     | 3.4.    | Operatii   | ng Modes                                                   |    |

|     | 3.5.    | Power S    | Saving                                                     |    |

|     | 3.      | 5.1. SI    | eep Mode                                                   |    |

|     |         | 3.5.1.1    | UART Application                                           |    |

|     |         | 3.5.1.2    | 2. USB Application with USB Remote Wakeup Function         |    |

|     |         | 3.5.1.3    | B. USB Application with USB Suspend/Resume and RI Function |    |

|     |         | 3.5.1.4    | I. USB Application without USB Suspend Function            |    |

|     | 3.      | .5.2. Ai   | rplane Mode                                                |    |

|     | 3.6.    | Power S    | Supply                                                     |    |

|     | 3.      | 6.1. Po    | ower Supply Pins                                           |    |

|     | 3.      | 6.2. D     | ecrease Voltage Drop                                       |    |

|     | 3.      |            | eference Design for Power Supply                           |    |

|     | 3.      | 6.4. M     | onitor the Power Supply                                    |    |

|     | 3.7.    | Power-c    | on/off Scenarios                                           |    |

|     | 3.      | 7.1. Tu    | urn on Module Using the PWRKEY                             |    |

|     | 3.      | .7.2. Tu   | urn off Module                                             |    |

|     |         | 3.7.2.1    | Turn off Module Using the PWRKEY Pin                       |    |

|     |         | 3.7.2.2    | 5                                                          |    |

|     | 3.8.    |            | lodule                                                     |    |

|     | 3.9.    | · · /      | Interface                                                  |    |

|     | 3.10.   |            | erface                                                     |    |

|     | 3.11.   |            | nterfaces                                                  |    |

|     | 3.12.   |            | nd I2C Interfaces                                          |    |

|     | 3.13.   |            | d Interface                                                |    |

|     | 3.14.   | ADC Int    | erfaces                                                    |    |

|    | 3.15.   | SGMII Interface                                        | 50 |

|----|---------|--------------------------------------------------------|----|

|    | 3.16.   | Network Status Indication                              | 52 |

|    | 3.17.   | STATUS                                                 | 54 |

|    | 3.18.   | Behaviors of RI                                        | 54 |

|    | 3.19.   | USB_BOOT Interface                                     |    |

| 4  | GNSS    | Receiver                                               |    |

|    | 4.1.    | General Description                                    | 57 |

|    | 4.2.    | GNSS Performance                                       | 57 |

|    | 4.3.    | Layout Guidelines                                      |    |

| 5  |         | na Interfaces                                          |    |

|    | 5.1.    | Main/Rx-diversity Antenna Interfaces                   | 59 |

|    | 5.1     | 1.1. Pin Definition                                    |    |

|    | 5.1     | 1.2. Operating Frequency                               | 59 |

|    | 5.1     | 1.3. Reference Design of RF Antenna Interface          | 61 |

|    | -       | 1.4. Reference Design of RF Layout                     |    |

|    | 5.2.    | GNSS Antenna Interface                                 |    |

|    | 5.3.    | Antenna Installation                                   |    |

|    |         | 3.1. Antenna Requirement                               |    |

|    | 5.3     | 3.2. Recommended RF Connector for Antenna Installation | 66 |

| 6  | Electri | ical, Reliability and Radio Characteristics            | 68 |

|    | 6.1.    | Absolute Maximum Ratings                               | 68 |

|    | 6.2.    | Power Supply Ratings                                   | 69 |

|    | 6.3.    | Operation and Storage Temperatures                     |    |

|    | 6.4.    | Current Consumption                                    | 70 |

|    | 6.5.    | RF Output Power                                        | 75 |

|    | 6.6.    | RF Receiving Sensitivity                               | 76 |

|    | 6.7.    | Electrostatic Discharge                                | 77 |

|    | 6.8.    | Thermal Consideration                                  | 78 |

| 7  | Mecha   | anical Dimensions                                      | 80 |

|    | 7.1.    | Mechanical Dimensions of the Module                    | 80 |

|    | 7.2.    | Recommended Footprint                                  | 82 |

|    | 7.3.    | Recommended Compatible Footprint                       | 83 |

|    | 7.4.    | Design Effect Drawings of the Module                   |    |

| 8  | Storag  | ge, Manufacturing and Packaging                        | 85 |

|    | 8.1.    | Storage                                                | 85 |

|    | 8.2.    | Manufacturing and Soldering                            | 86 |

|    | 8.3.    | Packaging                                              |    |

| 9  | Appen   | ndix A References                                      |    |

| 10 |         | ndix B GPRS Coding Schemes                             |    |

| 11 |         | ndix C GPRS Multi-slot Classes                         |    |

| 12 | Appen   | ndix D EDGE Modulation and Coding Schemes              | 96 |

## **Table Index**

| Table 1: Supported Frequency Bands and GNSS Function of EG21-G Module            | 11   |

|----------------------------------------------------------------------------------|------|

| Table 2: Key Features of EG21-G Module                                           | . 12 |

| Table 3: I/O Parameters Definition                                               | . 18 |

| Table 4: Pin Description                                                         | . 18 |

| Table 5: Overview of Operating Modes                                             | . 28 |

| Table 6: VBAT and GND Pins                                                       | . 32 |

| Table 7: Pin Definition of PWRKEY                                                | . 35 |

| Table 8: Pin Definition of RESET_N                                               | . 38 |

| Table 9: Pin Definition of (U)SIM Interface                                      | . 39 |

| Table 10: Pin Description of USB Interface                                       | . 41 |

| Table 11: Pin Definition of Main UART Interface                                  | . 43 |

| Table 12: Pin Definition of Debug UART Interface                                 | . 43 |

| Table 13: Logic Levels of Digital I/O                                            | . 44 |

| Table 14: Pin Definition of PCM and I2C Interfaces                               | . 46 |

| Table 15: Pin Definition of SD Card Interface                                    | . 48 |

| Table 16: Pin Definition of ADC Interfaces                                       | . 49 |

| Table 17: Characteristic of ADC                                                  | . 50 |

| Table 18: Pin Definition of SGMII Interface                                      | . 50 |

| Table 19: Pin Definition of Network Connection Status/Activity Indicator         | . 53 |

| Table 20: Working State of Network Connection Status/Activity Indicator          | . 53 |

| Table 21: Pin Definition of STATUS                                               | . 54 |

| Table 22: Behaviors of RI                                                        | . 55 |

| Table 23: Pin Definition of USB_BOOT Interface                                   |      |

| Table 24: GNSS Performance                                                       | . 57 |

| Table 25: Pin Definition of RF Antennas                                          | . 59 |

| Table 26: Module Operating Frequencies                                           | . 59 |

| Table 27: Pin Definition of GNSS Antenna Interface                               | . 63 |

| Table 28: GNSS Frequency                                                         | . 64 |

| Table 29: Antenna Requirements                                                   | . 65 |

| Table 30: Absolute Maximum Ratings                                               | . 68 |

| Table 31: Power Supply Ratings                                                   | . 69 |

| Table 32: Operation and Storage Temperatures                                     | . 69 |

| Table 33: EG21-G Current Consumption                                             | . 70 |

| Table 34: GNSS Current Consumption of EG21-G Module                              | . 75 |

| Table 35: RF Output Power                                                        | . 75 |

| Table 36: EG21-G Conducted RF Receiving Sensitivity                              | . 76 |

| Table 37: Electrostatics Discharge Characteristics (25°C, 45% Relative Humidity) | . 78 |

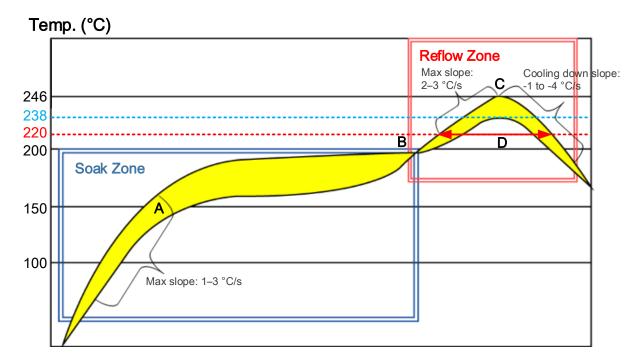

| Table 38: Recommended Thermal Profile Parameters                                 | . 87 |

| Table 39: Related Documents                                                      | . 89 |

| Table 40: Terms and Abbreviations                                                | . 89 |

| Table 41: Description of Different Coding Schemes                                | . 93 |

| Table 42: GPRS Multi-slot Classes            | 94 |

|----------------------------------------------|----|

| Table 43: EDGE Modulation and Coding Schemes | 96 |

## **Figure Index**

| Figure 1: Functional Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 15                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Pin Assignment (Top View)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 17                                                                                                                         |

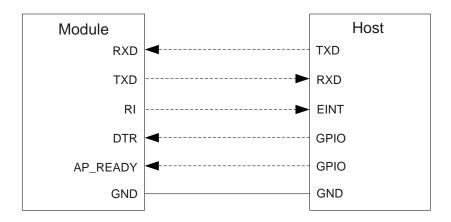

| Figure 3: Sleep Mode Application via UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 29                                                                                                                         |

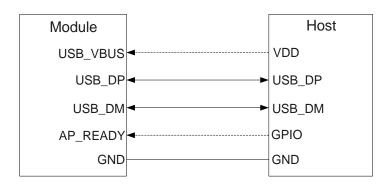

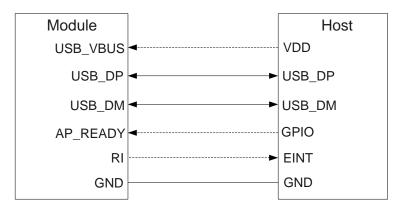

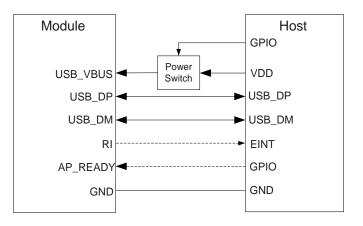

| Figure 4: Sleep Mode Application with USB Remote Wakeup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 29                                                                                                                         |

| Figure 5: Sleep Mode Application with RI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 30                                                                                                                         |

| Figure 6: Sleep Mode Application without Suspend Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 31                                                                                                                         |

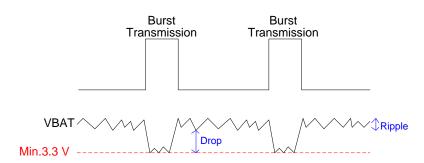

| Figure 7: Power Supply Limits during Burst Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 33                                                                                                                         |

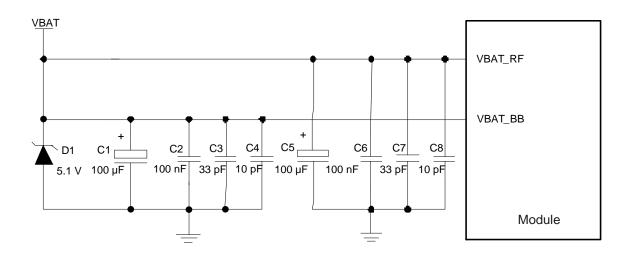

| Figure 8: Star Structure of the Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 33                                                                                                                         |

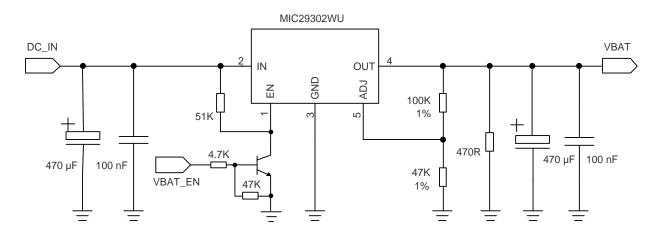

| Figure 9: Reference Circuit of Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 34                                                                                                                         |

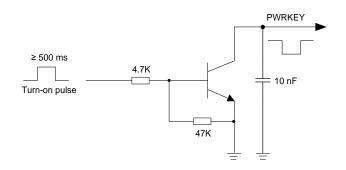

| Figure 10: Turn on the Module by Using Driving Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 35                                                                                                                         |

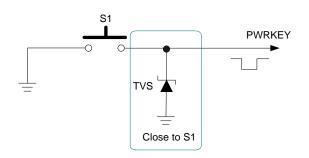

| Figure 11: Turn on the Module by Using Keystroke                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 35                                                                                                                         |

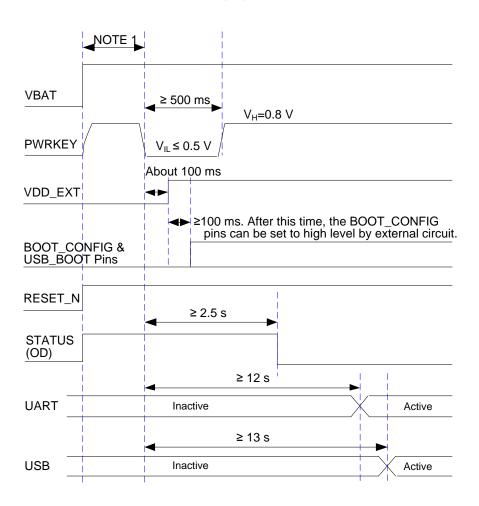

| Figure 12: Timing of Turning on Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 36                                                                                                                         |

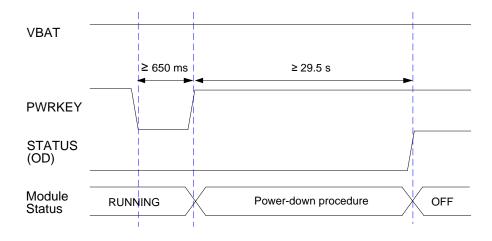

| Figure 13: Timing of Turning off Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 37                                                                                                                         |

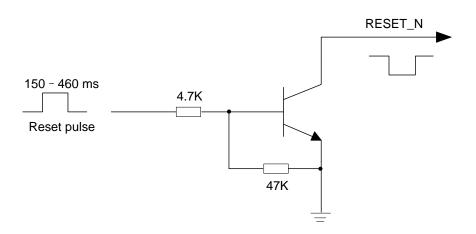

| Figure 14: Reference Circuit of RESET_N by Using Driving Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 38                                                                                                                         |

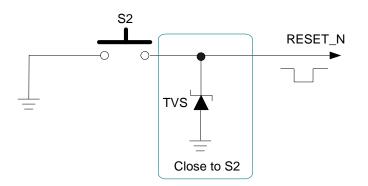

| Figure 15: Reference Circuit of RESET_N by Using Button                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 38                                                                                                                         |

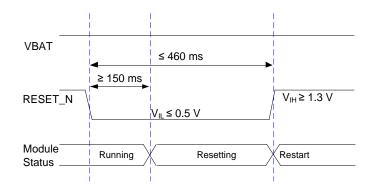

| Figure 16: Timing of Resetting Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 39                                                                                                                         |

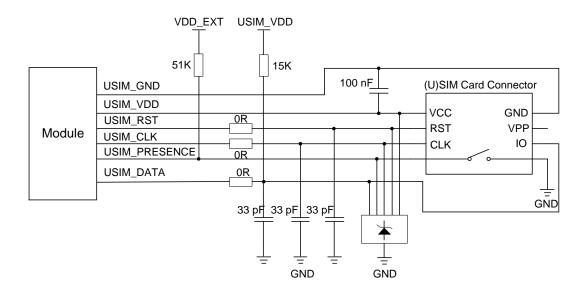

| Figure 17: Reference Circuit of (U)SIM Interface with an 8-pin (U)SIM Card Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 40                                                                                                                         |

| Figure 18: Reference Circuit of (U)SIM Interface with a 6-pin (U)SIM Card Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 40                                                                                                                         |

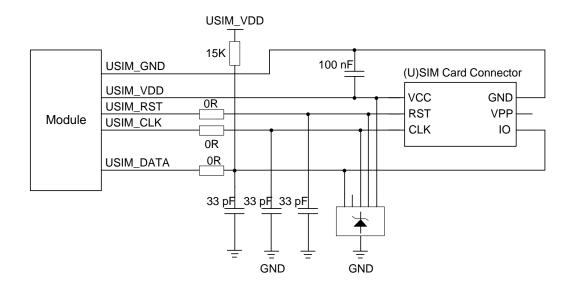

| Figure 19: Reference Circuit of USB Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 42                                                                                                                         |

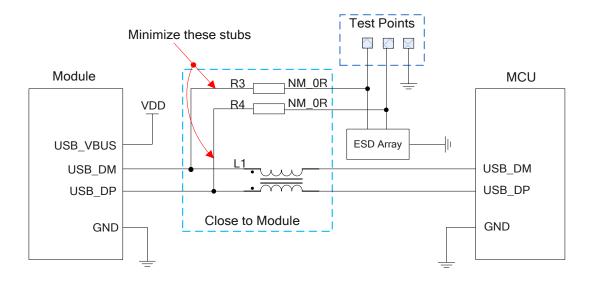

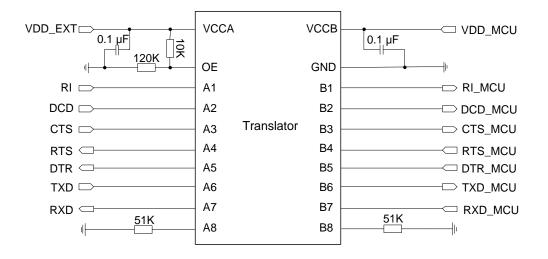

| Figure 20: Reference Circuit with Translator Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 44                                                                                                                         |

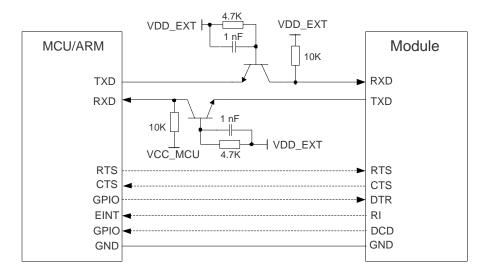

| Figure 21: Reference Circuit with Transistor Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 45                                                                                                                         |

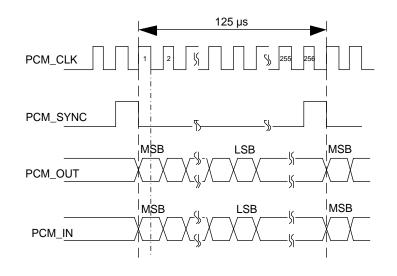

| Figure 22: Primary Mode Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 46                                                                                                                         |

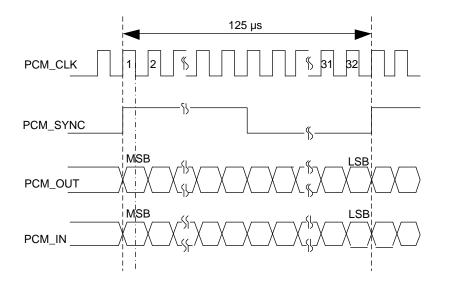

| Figure 23: Auxiliary Mode Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 40                                                                                                                         |

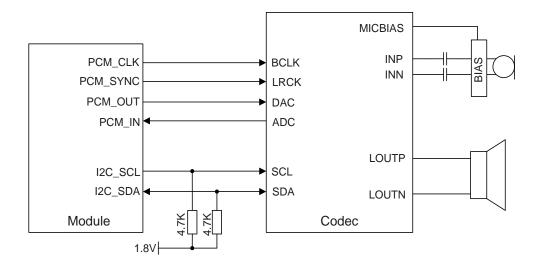

| Figure 24: Reference Circuit of PCM and I2C Application with Audio Codec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                              |

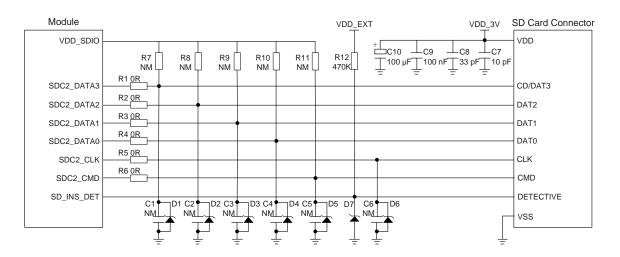

| Figure 24: Reference Circuit of PCM and I2C Application with Audio Codec<br>Figure 25: Reference Circuit of SD Card Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 47                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 47<br>. 48                                                                                                                 |

| Figure 25: Reference Circuit of SD Card Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 47<br>. 48<br>. 51                                                                                                         |

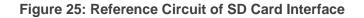

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 47<br>. 48<br>. 51<br>. 52                                                                                                 |

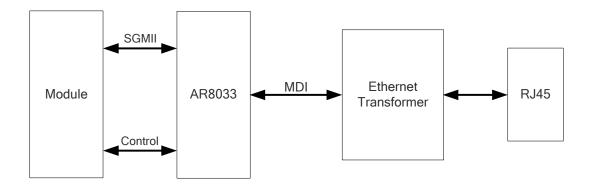

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application<br>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 47<br>. 48<br>. 51<br>. 52<br>. 53                                                                                         |

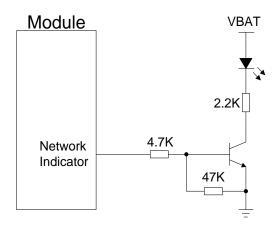

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application<br>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application<br>Figure 28: Reference Circuit of the Network Indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54                                                                                 |

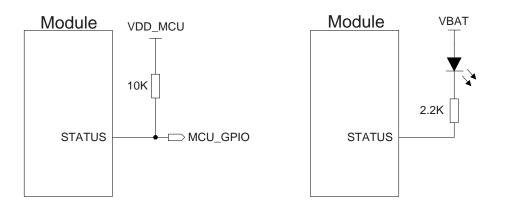

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application<br>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application<br>Figure 28: Reference Circuit of the Network Indicator<br>Figure 29: Reference Circuits of STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56                                                                         |

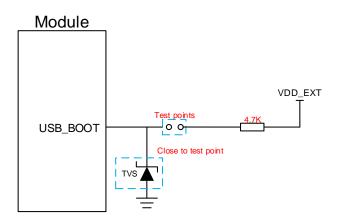

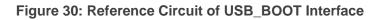

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application<br>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application<br>Figure 28: Reference Circuit of the Network Indicator<br>Figure 29: Reference Circuits of STATUS<br>Figure 30: Reference Circuit of USB_BOOT Interface                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 56                                                                 |

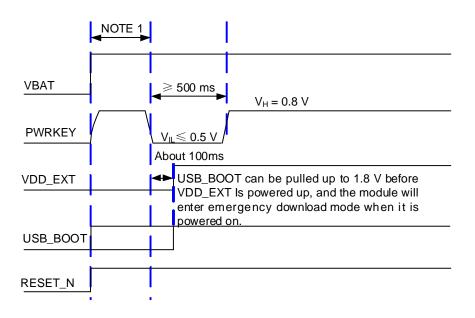

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application<br>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application<br>Figure 28: Reference Circuit of the Network Indicator<br>Figure 29: Reference Circuits of STATUS<br>Figure 30: Reference Circuit of USB_BOOT Interface<br>Figure 31: Timing Sequence for Entering Emergency Download Mode                                                                                                                                                                                                                                                                                                                                                                        | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 56<br>. 61                                                         |

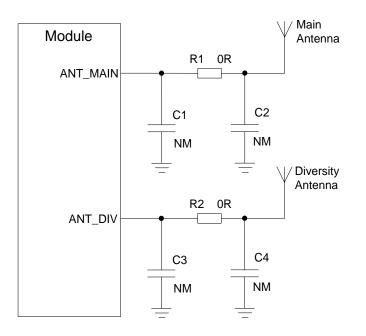

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application<br>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application<br>Figure 28: Reference Circuit of the Network Indicator<br>Figure 29: Reference Circuits of STATUS<br>Figure 30: Reference Circuit of USB_BOOT Interface<br>Figure 31: Timing Sequence for Entering Emergency Download Mode<br>Figure 32: Reference Circuit of RF Antenna Interface                                                                                                                                                                                                                                                                                                                | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 61<br>. 62                                                         |

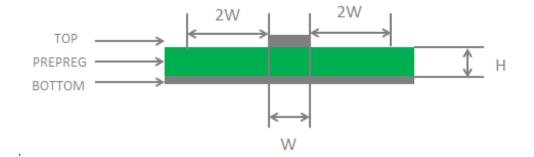

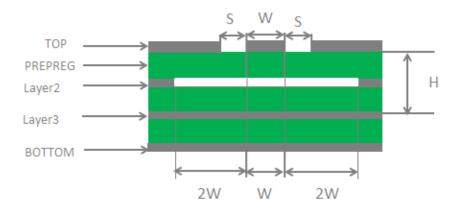

| <ul> <li>Figure 25: Reference Circuit of SD Card Interface</li> <li>Figure 26: Simplified Block Diagram for Ethernet Application</li> <li>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application</li> <li>Figure 28: Reference Circuit of the Network Indicator</li> <li>Figure 29: Reference Circuits of STATUS</li> <li>Figure 30: Reference Circuit of USB_BOOT Interface</li> <li>Figure 31: Timing Sequence for Entering Emergency Download Mode</li> <li>Figure 32: Reference Circuit of RF Antenna Interface</li> <li>Figure 33: Microstrip Design on a 2-layer PCB</li> </ul>                                                                                                                                                                                           | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 61<br>. 62<br>. 62                                                 |

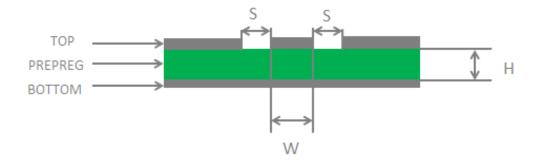

| <ul> <li>Figure 25: Reference Circuit of SD Card Interface</li> <li>Figure 26: Simplified Block Diagram for Ethernet Application</li> <li>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application</li> <li>Figure 28: Reference Circuit of the Network Indicator</li> <li>Figure 29: Reference Circuits of STATUS</li> <li>Figure 30: Reference Circuit of USB_BOOT Interface</li> <li>Figure 31: Timing Sequence for Entering Emergency Download Mode</li> <li>Figure 32: Reference Circuit of RF Antenna Interface</li> <li>Figure 33: Microstrip Design on a 2-layer PCB</li> <li>Figure 34: Coplanar Waveguide Design on a 2-layer PCB</li> </ul>                                                                                                                            | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 61<br>. 62<br>. 62<br>. 62                                         |

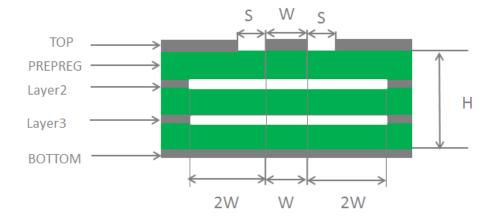

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application<br>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application<br>Figure 28: Reference Circuit of the Network Indicator<br>Figure 29: Reference Circuits of STATUS<br>Figure 30: Reference Circuit of USB_BOOT Interface<br>Figure 31: Timing Sequence for Entering Emergency Download Mode<br>Figure 32: Reference Circuit of RF Antenna Interface<br>Figure 33: Microstrip Design on a 2-layer PCB<br>Figure 34: Coplanar Waveguide Design on a 4-layer PCB (Layer 3 as Reference Ground)                                                                                                                                                                        | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 61<br>. 62<br>. 62<br>. 62<br>. 63                                 |

| <ul> <li>Figure 25: Reference Circuit of SD Card Interface</li> <li>Figure 26: Simplified Block Diagram for Ethernet Application</li> <li>Figure 27: Reference Circuit of SGMII Interface with PHY AR8033 Application</li> <li>Figure 28: Reference Circuit of the Network Indicator</li> <li>Figure 29: Reference Circuits of STATUS</li> <li>Figure 30: Reference Circuit of USB_BOOT Interface</li> <li>Figure 31: Timing Sequence for Entering Emergency Download Mode</li> <li>Figure 32: Reference Circuit of RF Antenna Interface</li> <li>Figure 33: Microstrip Design on a 2-layer PCB</li> <li>Figure 34: Coplanar Waveguide Design on a 2-layer PCB (Layer 3 as Reference Ground)</li> <li>Figure 36: Coplanar Waveguide Design on a 4-layer PCB (Layer 4 as Reference Ground)</li> </ul> | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 61<br>. 62<br>. 62<br>. 62<br>. 63<br>. 64                         |

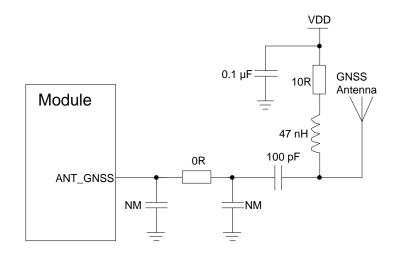

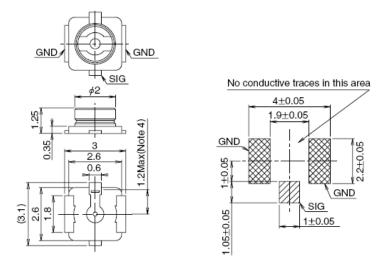

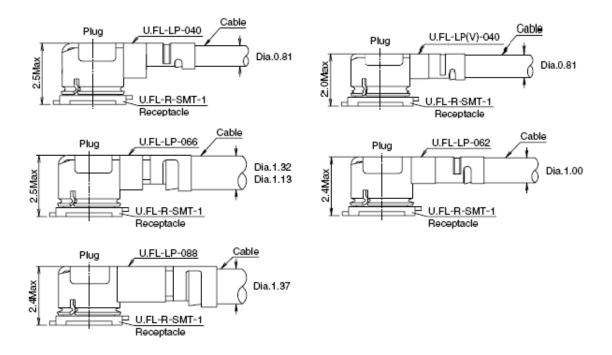

| Figure 25: Reference Circuit of SD Card Interface<br>Figure 26: Simplified Block Diagram for Ethernet Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 61<br>. 62<br>. 62<br>. 62<br>. 63<br>. 64<br>. 66                 |

| <ul> <li>Figure 25: Reference Circuit of SD Card Interface</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 47<br>. 48<br>. 51<br>. 52<br>. 53<br>. 54<br>. 56<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 64<br>. 66<br>. 66 |

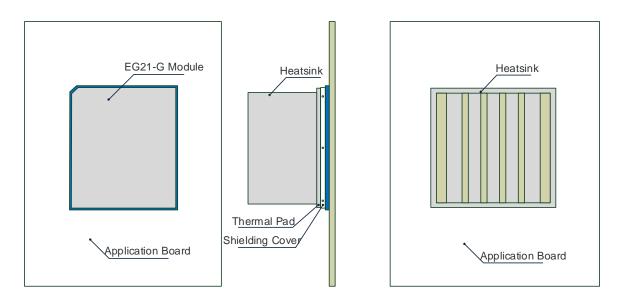

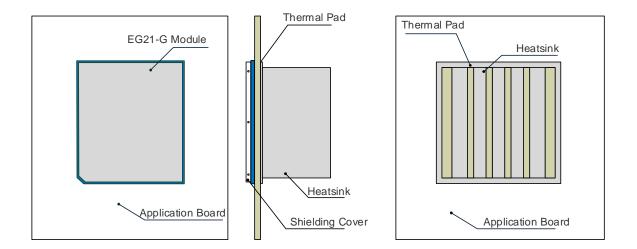

| Figure 42: Referenced Heatsink Design (Heatsink at the Backside of Customers' PCB) | 79 |

|------------------------------------------------------------------------------------|----|

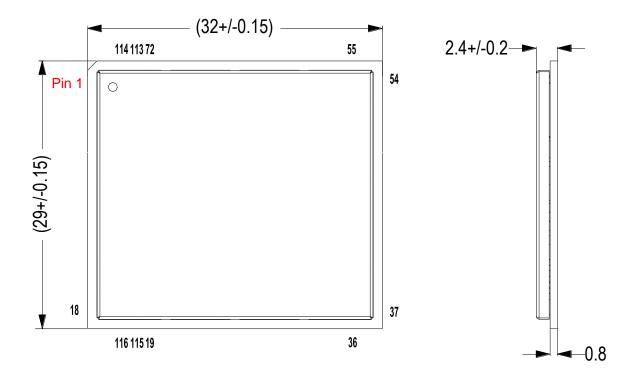

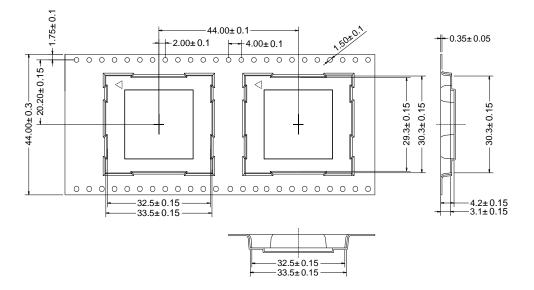

| Figure 43: Module Top and Side Dimensions                                          | 80 |

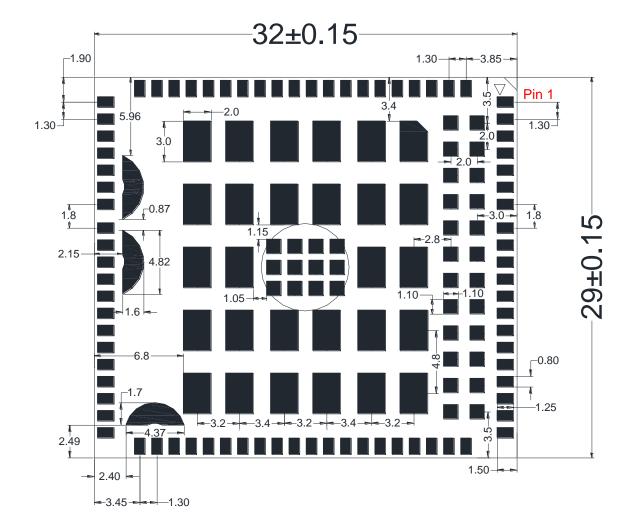

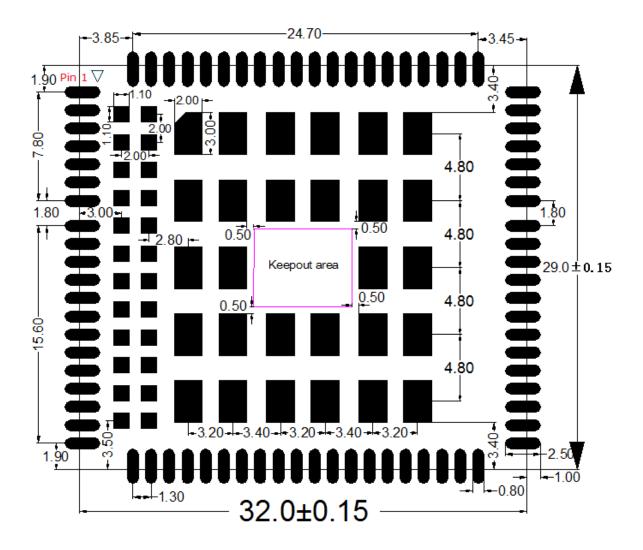

| Figure 44: Module Bottom Dimensions (Bottom View)                                  | 81 |

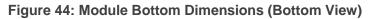

| Figure 45: Recommended Footprint (Top View)                                        | 82 |

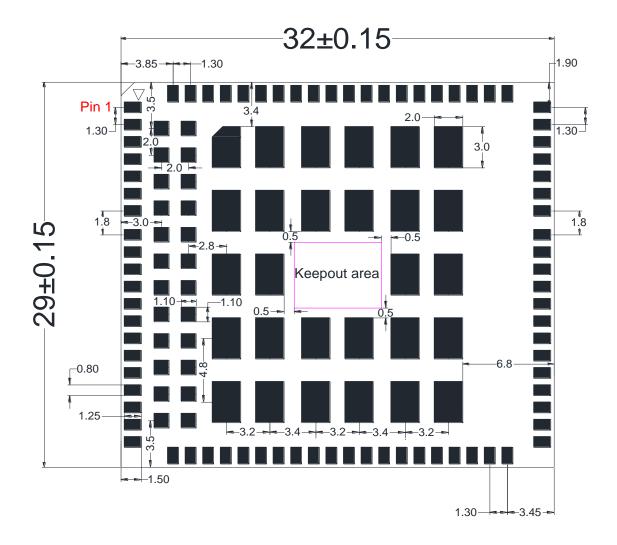

| Figure 46: Recommended Compatible Footprint (Top View)                             | 83 |

| Figure 47: Top View of the Module                                                  | 84 |

| Figure 48: Bottom View of the Module                                               | 84 |

| Figure 49: Reflow Soldering Thermal Profile                                        | 86 |

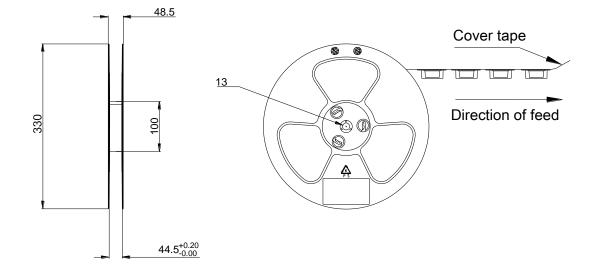

| Figure 50: Tape Specifications                                                     | 87 |

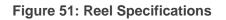

| Figure 51: Reel Specifications                                                     | 88 |

| Figure 52: Tape and Reel Directions                                                | 88 |

## **1** Introduction

This document defines EG21-G module, and describes its air interface and hardware interfaces which are connected with customers' applications.

This document can help customers quickly understand module interface specifications, electrical and mechanical details as well as other related information of EG21-G module. To facilitate its application in different fields, relevant reference design is also provided for customers' reference. Associated with application note and user guide, customers can use EG21-G module to design and set up mobile applications easily.

## 1.1. Safety Information

The following safety precautions must be observed during all phases of operation, such as usage, service or repair of any cellular terminal or mobile incorporating EG21-G module. Manufacturers of the cellular terminal should send the following safety information to users and operating personnel, and incorporate these guidelines into all manuals supplied with the product. If not so, Quectel assumes no liability for customers' failure to comply with these precautions.

|            | Full attention must be given to driving at all times in order to reduce the risk of an accident. Using a mobile while driving (even with a handsfree kit) causes distraction and can lead to an accident. Please comply with laws and regulations restricting the use of wireless devices while driving.                                                                                                                                             |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Switch off the cellular terminal or mobile before boarding an aircraft. The operation of wireless appliances in an aircraft is forbidden to prevent interference with communication systems. If the device offers an Airplane Mode, then it should be enabled prior to boarding an aircraft. Please consult the airline staff for more restrictions on the use of wireless devices on boarding the aircraft.                                         |

| •          | Wireless devices may cause interference on sensitive medical equipment, so please be aware of the restrictions on the use of wireless devices when in hospitals, clinics or other healthcare facilities.                                                                                                                                                                                                                                             |

| SOS        | Cellular terminals or mobiles operating over radio signals and cellular network cannot be guaranteed to connect in all possible conditions (for example, with unpaid bills or with an invalid (U)SIM card). When emergent help is needed in such conditions, please remember using emergency call. In order to make or receive a call, the cellular terminal or mobile must be switched on in a service area with adequate cellular signal strength. |

| The second | The cellular terminal or mobile contains a transmitter and receiver. When it is ON, it receives and transmits radio frequency signals. RF interference can occur if it is used close to TV set, radio, computer or other electric equipment.                                                                                                                                                                                                         |

|            | In locations with potentially explosive atmospheres, obey all posted signs to turn<br>off wireless devices such as your phone or other cellular terminals. Areas with<br>potentially explosive atmospheres include fuelling areas, below decks on boats,<br>fuel or chemical transfer or storage facilities, areas where the air contains<br>chemicals or particles such as grain, dust or metal powders, etc.                                       |

## **2** Product Concept

## 2.1. General Description

EG21-G is an LTE-FDD/LTE-TDD/WCDMA/GSM wireless communication module with receive diversity. It provides data connectivity on LTE-FDD, LTE-TDD, DC-HSDPA, HSPA+, HSDPA, HSUPA, UMTS, EDGE and GPRS networks. It also provides GNSS and voice functionality for customers' specific applications. The following table shows the supported frequency bands, GNSS and digital audio functions of EG21-G module.

| Frequency Bands/<br>GNSS Function/<br>Digital Audio | EG21-G                                               |

|-----------------------------------------------------|------------------------------------------------------|

| LTE-FDD<br>(with receive diversity)                 | B1/B2/B3/B4/B5/B7/B8/B12/B13/B18/B19/B20/B25/B26/B28 |

| LTE-TDD<br>(with receive diversity)                 | B38/B39/B40/B41                                      |

| WCDMA<br>(with receive diversity)                   | B1/B2/B4/B5/B6/B8/B19                                |

| GSM                                                 | 850/900/1800/1900 MHz                                |

| GNSS Function (Optional)                            | GPS, GLONASS, BeiDou (Compass), Galileo, QZSS        |

| Digital Audio (PCM)                                 | Supported                                            |

#### Table 1: Supported Frequency Bands and GNSS Function of EG21-G Module

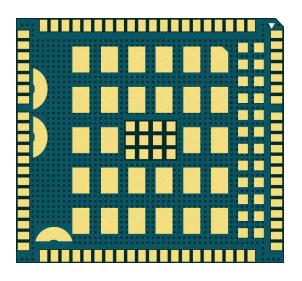

With a compact profile of 29.0 mm  $\times$  32.0 mm  $\times$  2.4 mm, EG21-G can meet almost all requirements for M2M applications such as automotive, smart metering, tracking system, security, router, wireless POS, mobile computing device, PDA phone, tablet PC, etc.

EG21-G is an SMD type module which can be embedded into applications through its 144-pin LGA <sup>1)</sup> pads.

NOTE

<sup>1)</sup> EG21-G includes LGA and LCC form factors. LGA is default, while LCC is recommended only in the compatible design with EC25 series/EC21 series/EC20 R2.1/EG25-G/UC200T modules.

## 2.2. Key Features

The following table describes the detailed features of EG21-G module.

| Table 2 | 2: Key | <b>Features</b> | of | EG21-G | Module |

|---------|--------|-----------------|----|--------|--------|

|---------|--------|-----------------|----|--------|--------|

| Features           | Description                                             |

|--------------------|---------------------------------------------------------|

| Power Supply       | Supply voltage: 3.3–4.3 V                               |

|                    | Typical supply voltage: 3.8 V                           |

|                    | Class 4 (33 dBm ±2 dB) for GSM850                       |

|                    | Class 4 (33 dBm ±2 dB) for EGSM900                      |

|                    | Class 1 (30 dBm ±2 dB) for DCS1800                      |

|                    | Class 1 (30 dBm ±2 dB) for PCS1900                      |

|                    | Class E2 (27 dBm ±3 dB) for GSM850 8-PSK                |

| Transmitting Power | Class E2 (27 dBm ±3 dB) for EGSM900 8-PSK               |

|                    | Class E2 (26 dBm ±3 dB) for DCS1800 8-PSK               |

|                    | Class E2 (26 dBm ±3 dB) for PCS1900 8-PSK               |

|                    | Class 3 (24 dBm +1/-3 dB) for WCDMA bands               |

|                    | Class 3 (23 dBm $\pm$ 2 dB) for LTE-FDD bands           |

|                    | Class 3 (23 dBm ±2 dB) for LTE-TDD bands                |

|                    | Support up to non-CA Cat 1 FDD and TDD                  |

|                    | Support 1.4/3/5/10/15/20 MHz RF bandwidth               |

| LTE Features       | Support MIMO in DL direction                            |

|                    | LTE-FDD: Max 10 Mbps (DL), Max 5 Mbps (UL)              |

|                    | LTE-TDD: Max 8.96 Mbps (DL), Max 3.1 Mbps (UL)          |

|                    | Support 3GPP R8 DC-HSDPA, HSPA+, HSDPA, HSUPA and WCDMA |

|                    | Support QPSK, 16-QAM and 64-QAM modulation              |

| UMTS Features      | DC-HSDPA: Max 42 Mbps (DL)                              |

|                    | HSUPA: Max 5.76 Mbps (UL)                               |

|                    | WCDMA: Max 384 kbps (DL), Max 384 kbps (UL)             |

|                    | GPRS:                                                   |

|                    | Support GPRS multi-slot class 33 (33 by default)        |

| GSM Features       | Coding scheme: CS-1, CS-2, CS-3 and CS-4                |

|                    | Max 107 kbps (DL), Max 85.6 kbps (UL)                   |

|                    | EDGE:                                                   |

|                               | Support EDGE multi-slot class 33 (33 by default)<br>Support GMSK and 8-PSK for different MCS (Modulation and Coding<br>Scheme)<br>Downlink coding schemes: CS 1-4 and MCS 1-9<br>Uplink coding schemes: CS 1-4 and MCS 1-9<br>Max 296 kbps (DL), Max 236.8 kbps (UL)                                                                                                    |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internet Protocol<br>Features | Support TCP/UDP/PPP/FTP/FTPS/HTTP/HTTPS/NTP/PING/QMI/NITZ/<br>SMTP/SSL/MQTT/CMUX/SMTPS/MMS*/FILE* protocols<br>Support PAP (Password Authentication Protocol) and CHAP (Challenge<br>Handshake Authentication Protocol) protocols which are usually used for<br>PPP connections                                                                                         |

| SMS                           | Text and PDU modes<br>Point-to-point MO and MT<br>SMS cell broadcast<br>SMS storage: ME by default                                                                                                                                                                                                                                                                      |

| (U)SIM Interface              | Support USIM/SIM card: 1.8 V, 3.0 V                                                                                                                                                                                                                                                                                                                                     |

| Audio Features                | Support one digital audio interface: PCM interface<br>GSM: HR/FR/EFR/AMR/AMR-WB<br>WCDMA: AMR/AMR-WB<br>LTE: AMR/AMR-WB<br>Support echo cancellation and noise suppression                                                                                                                                                                                              |

| PCM Interface                 | Used for audio function with external codec<br>Support 16-bit linear data format<br>Support long frame synchronization and short frame synchronization<br>Support master and slave modes, but must be the master in long frame<br>synchronization                                                                                                                       |

| USB Interface                 | Compliant with USB 2.0 specification (slave only); the data transfer rate can<br>reach up to 480 Mbps<br>Used for AT command communication, data transmission, GNSS NMEA<br>sentences output, software debugging, firmware upgrade and voice over<br>USB<br>Support USB serial drivers for: Windows 7/8/8.1/10, Linux 2.6–5.4, Android<br>4.x/5.x/6.x/7.x/8.x/9.x, etc. |

| UART Interfaces               | Main UART:<br>Used for AT command communication and data transmission<br>Baud rates reach up to 921600 bps, 115200 bps by default<br>Support RTS and CTS hardware flow control<br>Debug UART:<br>Used for Linux console and log output<br>115200bps baud rate                                                                                                           |

|                               |                                                                                                                                                                                                                                                                                                                                                                         |

| SD Card Interface             | Support SD 3.0 protocol                                                                                                                                                                                                                                                                                                                                                 |

|                           | Support maximum 150 Mbps (DL)/50 Mbps (UL) for 4G network           |  |  |  |  |

|---------------------------|---------------------------------------------------------------------|--|--|--|--|

| Rx-diversity              | Support LTE/WCDMA Rx-diversity                                      |  |  |  |  |

|                           | Gen8C Lite of Qualcomm                                              |  |  |  |  |

| GNSS Features             | Protocol: NMEA 0183                                                 |  |  |  |  |

|                           | Data update rate: 1 Hz by default                                   |  |  |  |  |

| AT Commands               | Compliant with 3GPP TS 27.007, 27.005 and Quectel enhanced AT       |  |  |  |  |

| AT Commanus               | commands                                                            |  |  |  |  |

| Network Indication        | Two pins including NET_MODE and NET_STATUS to indicate network      |  |  |  |  |

| Network Indication        | connectivity status                                                 |  |  |  |  |

| Antenna Interfaces        | Including main antenna interface (ANT_MAIN), Rx-diversity antenna   |  |  |  |  |

| Antenna Intenaces         | interface (ANT_DIV) and GNSS antenna interface (ANT_GNSS)           |  |  |  |  |

|                           | Size: (29.0 ±0.15) mm × (32.0 ±0.15) mm × (2.4 ±0.2) mm             |  |  |  |  |

| Physical Characteristics  | Package: LGA (default)                                              |  |  |  |  |

| Filysical Characteristics | LCC (compatible design)                                             |  |  |  |  |

|                           | Weight: approx. 4.9 g                                               |  |  |  |  |

|                           | Operation temperature range: -35 °C to +75 °C <sup>1)</sup>         |  |  |  |  |

| Temperature Range         | Extended temperature range: -40 °C to +85 °C <sup>2)</sup>          |  |  |  |  |

|                           | Storage temperature range: -40 °C to +90 °C                         |  |  |  |  |

| Firmware Upgrade          | USB interface or DFOTA                                              |  |  |  |  |

| RoHS                      | All hardware components are fully compliant with EU RoHS directive. |  |  |  |  |

## NOTES

- 1. <sup>1)</sup> Within operation temperature range, the module is 3GPP compliant.

- 2. <sup>2)</sup> Within extended temperature range, the module remains the ability to establish and maintain a voice, SMS, data transmission, emergency call\*, etc. There is no unrecoverable malfunction. There are also no effects on radio spectrum and no harm to radio network. Only one or more parameters like P<sub>out</sub> might reduce in their value and exceed the specified tolerances. When the temperature returns to normal operation temperature levels, the module will meet 3GPP specifications again.

- 3. "\*" means under development.

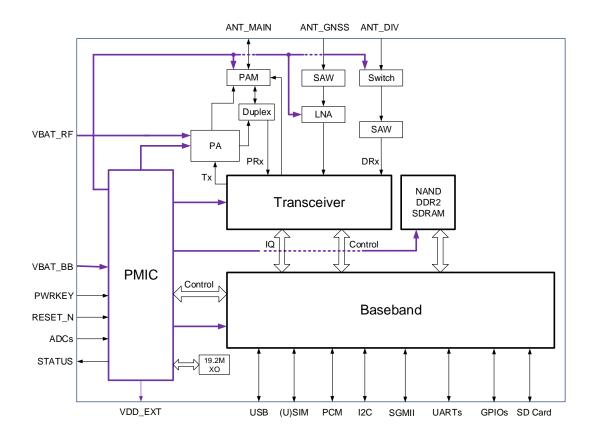

## 2.3. Functional Diagram

The following figure shows a block diagram of EG21-G and illustrates the major functional parts.

- Power management

- Baseband

- DDR+NAND flash

- Radio frequency

- Peripheral interfaces

Figure 1: Functional Diagram

## 2.4. Evaluation Board

In order to help customers develop applications with EG21-G, Quectel supplies an evaluation board (UMTS&LTE EVB), USB to RS-232 converter cable, earphone, antenna and other peripherals to control or test the module. For more details, please refer to *document [8]*.

# **3** Application Interfaces

## 3.1. General Description

EG21-G is equipped with 144 LGA pads that can be connected to cellular application platform. The subsequent chapters will provide detailed descriptions of the following functions/interfaces.

- Power supply

- (U)SIM interface

- USB interface

- UART interfaces

- PCM and I2C interfaces

- SD card interface

- ADC interfaces

- Status indication

- SGMII interface

- USB\_BOOT interface

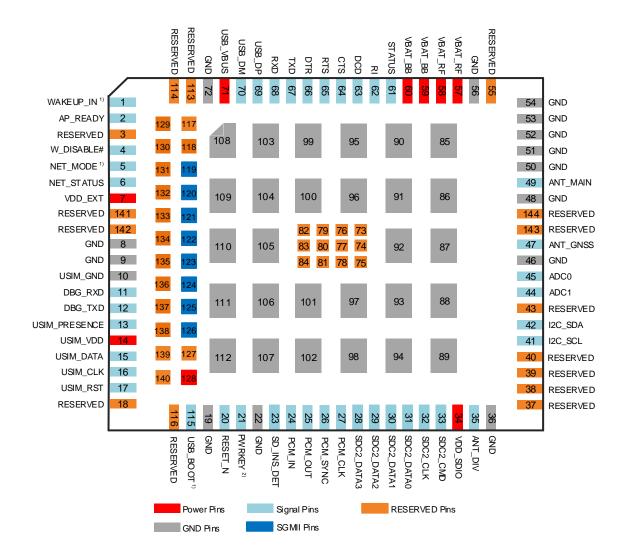

## 3.2. Pin Assignment

The following figure shows the pin assignment of EG21-G module.

Figure 2: Pin Assignment (Top View)

## NOTES

- 1. <sup>1)</sup> means pins WAKEUP\_IN, NET\_MODE and USB\_BOOT cannot be pulled up before startup.

- 2. <sup>2)</sup> PWRKEY output voltage is 0.8 V because of the diode drop in the Qualcomm chipset.

- 3. Pads 119–126 are SGMII function pins.

- 4. Keep all RESERVED pins and unused pins unconnected.

- 5. GND pins 85–112 should be connected to ground in the design. RESERVED pins 73–84 should not be designed in schematic and PCB decal, and these pins should be served as a keepout area.

## 3.3. Pin Description

The following tables show the pin definition of EG21-G modules.

Table 3: I/O Parameters Definition

| Туре | Description    |  |  |  |

|------|----------------|--|--|--|

| AI   | Analog Input   |  |  |  |

| AO   | Analog Output  |  |  |  |

| DI   | Digital Input  |  |  |  |

| DO   | Digital Output |  |  |  |

| 10   | Bidirectional  |  |  |  |

| OD   | Open Drain     |  |  |  |

| PI   | Power Input    |  |  |  |

| PO   | Power Output   |  |  |  |

## Table 4: Pin Description

| Power Supply |                                        |     |                                         |                                               |                                                                                           |

|--------------|----------------------------------------|-----|-----------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------|

| Pin Name     | Pin No.                                | I/O | Description                             | DC Characteristics                            | Comment                                                                                   |

| VBAT_BB      | 59, 60                                 | ΡI  | Power supply for module's baseband part | Vmax = 4.3 V<br>Vmin = 3.3 V<br>Vnorm = 3.8 V | It must be provided<br>with sufficient current<br>up to 0.8 A.                            |

| VBAT_RF      | 57, 58                                 | PI  | Power supply for module's RF part       | Vmax = 4.3 V<br>Vmin = 3.3 V<br>Vnorm = 3.8 V | It must be provided<br>with sufficient current<br>up to 1.8 A in a burst<br>transmission. |

| VDD_EXT      | 7                                      | PO  | Provide 1.8 V for external circuit      | Vnorm = 1.8 V<br>I <sub>o</sub> max = 50 mA   | Power supply for<br>external GPIO's pull up<br>circuits.<br>If unused, keep it open.      |

| GND          | 8, 9, 19,<br>22, 36, 46,<br>48, 50–54, |     | Ground                                  |                                               |                                                                                           |

56, 72, 85–112

Power-on/off

| Pin Name       | Pin No. | I/O | Description                                           | DC Characteristics                                                                        | Comment                                                                                                                    |

|----------------|---------|-----|-------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| PWRKEY         | 21      | DI  | Turn on/off the module                                | V <sub>H</sub> = 0.8 V                                                                    | The output voltage is<br>0.8V because of the<br>diode drop in the<br>Qualcomm chipset.                                     |

| RESET_N        | 20      | DI  | Reset signal of the module                            | V <sub>IH</sub> max = 2.1 V<br>V <sub>IH</sub> min = 1.3 V<br>V <sub>IL</sub> max = 0.5 V | lf unused, keep it<br>open.                                                                                                |

| Status Indicat | ion     |     |                                                       |                                                                                           |                                                                                                                            |

| Pin Name       | Pin No. | I/O | Description                                           | DC Characteristics                                                                        | Comment                                                                                                                    |

| STATUS         | 61      | OD  | Indicate the module operating status                  | The drive current<br>should be less than<br>0.9 mA.                                       | An external pull-up<br>resistor is required. If<br>unused, keep it open.                                                   |

| NET_MODE       | 5       | DO  | Indicate the<br>module's network<br>registration mode | V <sub>OH</sub> min = 1.35 V<br>V <sub>OL</sub> max = 0.45 V                              | <ul><li>1.8 V power domain.</li><li>Cannot be pulled up<br/>before startup.</li><li>If unused, keep it<br/>open.</li></ul> |

| NET_<br>STATUS | 6       | DO  | Indicate the<br>module's network<br>activity status   | V <sub>OH</sub> min = 1.35 V<br>V <sub>OL</sub> max = 0.45 V                              | 1.8 V power domain.<br>If unused, keep it<br>open.                                                                         |

| USB Interface  |         |     |                                                       |                                                                                           |                                                                                                                            |

| Pin Name       | Pin No. | I/O | Description                                           | DC Characteristics                                                                        | Comment                                                                                                                    |