## **STX 104 Reference Manual**

# STX104(-ND) Reference Manual Analog I/O with 16-Bit Resolution

Apex Embedded Systems LLC 116 Owen Road Monona, WI 53716 Phone 608.256.0767

www.apexembeddedsystems.com

customer.service@ap exembed ded systems.com

Copyright Notice

Copyright © 2003-2018 by Apex Embedded Systems LLC. All rights reserved.

## **Table of Contents**

| 1  |

|----|

| 3  |

| 5  |

| Ę  |

| 8  |

| g  |

| 11 |

| 13 |

| 15 |

| 15 |

| 15 |

| 15 |

| 15 |

| 15 |

| 17 |

| 17 |

| 18 |

| 18 |

| 19 |

| 22 |

| 22 |

| 23 |

|    |

| Continuous High Speed Sampling                 | 24 |

|------------------------------------------------|----|

| Start/Stop-Trigger Encased Frame Groups        | 25 |

| N-Sample Collection                            | 26 |

| Analog Input Sample Timing                     | 27 |

| Triggering Subsystem                           | 30 |

| Moving Average Filter                          | 32 |

| CPU Readout Methods                            | 32 |

| DMA Read                                       | 32 |

| Burst Read                                     | 33 |

| Single Read                                    | 33 |

| Analog Outputs                                 | 35 |

| Calibration                                    | 35 |

| Connectivity                                   | 35 |

| Hardware Configuration                         | 37 |

| Base Address Table                             | 37 |

| Compatibility Selection and Extended Functions | 38 |

| CPU Limitation Accommodations                  | 40 |

| PC104-DAS16jr/12                               | 40 |

| Register Set                                   | 43 |

| Summary                                        | 43 |

| Software Strobe (Offset=0)                     | 46 |

| ADC Data LSB (Offset=0)                        | 47 |

| ADC Data MSB (Offset=1)                        | 48 |

| ADC Data (Offset=0)                            | 48 |

| ADC Channel (Offset=2)                         | 54 |

| Digital Outputs (Offset=3)                     | 56 |

| Digital Inputs (Offset=3)                      | 57 |

| DAC Channel-A LSB (Offset=4)                             | 58 |

|----------------------------------------------------------|----|

| DAC Channel-A MSB (Offset=5)                             | 58 |

| DAC Channel-A (Offset=4)                                 | 58 |

| DAC Channel-B LSB (Offset=6)                             | 60 |

| DAC Channel-B MSB (Offset=7)                             | 61 |

| DAC Channel-B (Offset=6)                                 | 61 |

| Clear Interrupts (Offset=8)                              | 63 |

| ADC Status (Offset=8)                                    | 64 |

| ADC Control (Offset=9)                                   | 66 |

| Pacer Clock Control (Offset=10)                          | 68 |

| FIFO Status MSB (Offset=10)                              | 69 |

| ADC Configuration (Offset=11)                            | 72 |

| ADC Configuration PC104-DAS16Jr/12                       | 75 |

| 8254 CT0 Data (Offset=12, RB='0'. Index=68, RB='1')      | 77 |

| 8254 CT1 Data (Offset=13, RB='0'. Index=69, RB='1')      | 77 |

| 8254 CT2 Data (Offset=14, RB='0'. Index=70, RB='1')      | 77 |

| 8254 Configuration (Offset=15, RB='0'. Index=71, RB='1') | 77 |

| FIFO Status LSB (Offset=15)                              | 80 |

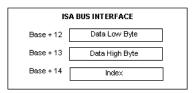

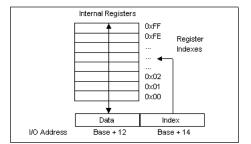

| Index Data LSB (Offset=12, RB='1')                       | 80 |

| Index Data MSB (Offset=13, RB='1')                       | 80 |

| Index Data (Offset=12, RB='1')                           | 81 |

| Index Pointer (Offset=14, RB='1')                        | 81 |

| Conversion Disable (Offset=1028; Index=64, RB='1')       | 84 |

| Burst Mode Enable (Offset=1029; Index=65, RB='1')        | 85 |

| Burst Function Enable (Offset=1030; Index=66, RB='1')    | 86 |

| Extended Status (Offset=1031; Index=67, RB='1')          | 86 |

| General Configuration (Index=0, RB='1')                  | 87 |

| Support Policy                                                  | 127 |

|-----------------------------------------------------------------|-----|

| Mechanicals                                                     | 125 |

| Connector Summary                                               | 121 |

| Interrupt Summary                                               | 119 |

| Power Supply                                                    | 117 |

| General Information (Index=252, RB='1')                         | 115 |

| Board ID (Index=250, RB='1')                                    | 114 |

| Scratch Pad (Index=248, RB='1')                                 | 113 |

| FIFO Configuration (Index=228, RB='1')                          | 112 |

| FIFO Data Available (Index=224, RB='1')                         | 111 |

| Miscellaneous Output Configuration Register (Index=208, RB='1') | 110 |

| Analog Input Frame Counter (Index=48, RB='1')                   | 109 |

| Analog Input Frame Maximum (Index=44, RB='1')                   | 108 |

| Analog Input Burst Timer (Index=40, RB='1')                     | 105 |

| Analog Input Frame Timer (Index=36, RB='1')                     | 104 |

| Analog Input Polarity (Index=33, RB='1')                        | 103 |

| Analog Input General Configuration (Index=32, RB='1')           | 100 |

| Trigger Start Delay (Index=20, RB='1')                          | 99  |

| Trigger Configuration (Index=16, RB='1')                        | 97  |

| Digital Input Configuration (Index=14, RB='1')                  | 96  |

| Digital Output Configuration (Index=12, RB='1')                 | 94  |

| Interrupt Threshold (Index=8, RB='1')                           | 92  |

| Interrupt Configuration (Index=4, RB='1')                       | 90  |

| Interrupt Source Select (Index=2, RB='1')                       | 89  |

| General Support Policy                             | 127 |

|----------------------------------------------------|-----|

| Recommended Sequence in Obtaining Customer Support | 127 |

| Need Custom Modifications?                         | 127 |

| Specifications                                     | 129 |

| STX104-1MFIFO-NODACS                               | 131 |

| STX104-1MFIFO-DAQ                                  | 131 |

| Valid Part Numbers                                 | 132 |

| Revision Information                               | 132 |

| Limited Warranty                                   | 135 |

| Index                                              | а   |

# STX104(-ND) Reference Manual

## 1 Welcome

Dear Valued Customer:

Thank you for your interest in our products and services.

Apex Embedded Systems "Continuous improvement" policy utilizes customer feedback to improve existing products and create new product offerings based on needs of our customers.

Continued Success,

Apex Embedded Systems

# 2 Legal Notice

Apex Embedded Systems' sole obligation for products that prove to be defective within 1 year from date of purchase will be for replacement or refund. Apex Embedded Systems gives no warranty, either expressed or implied, and specifically disclaims all other warranties, including warranties for merchantability and fitness. In no event shall Apex Embedded Systems' liability exceed the buyer's purchase price, nor shall Apex Embedded Systems be liable for any indirect or consequential damages.

This warranty does not apply to products which have been subject to misuse (including static discharge), neglect, accident or modification, or which have been soldered or altered during assembly and are not capable of being tested.

DO NOT USE PRODUCTS SOLD BY APEX EMBEDDED SYSTEMS AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS!

Products sold by Apex Embedded Systems are not authorized for use as critical components in life support devices or systems. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## 3 Benefits and Features

## 3.1 Executive Summary

What is the STX104? The STX104 is a 16-channel 16-bit analog input and 2-channel 16-bit analog output card. The STX104 incorporates a large one mega-sample FIFO.

### **Description**

What are the Benefits of using the STX104? The STX104 has the following benefits:

- One mega-sample FIFO data storage provides continuous data streaming from ADC to CPU with reduction in interrupt overhead and relaxation of interrupt latencies.

- 200,000 Samples per second aggregate for analog inputs

- · Analog input 16-Sample moving average filters for data noise reduction

- Compatible with DAS16jr/16 and DAS1602 for using existing 3rd party drivers

- 16-bit data read (ADC data) operations double effective PC/104 bus bandwidth

- 16-bit data write (DAC data) operations reduce software overhead

- Use REP INSW (286 or higher CPU) to read-in blocks of ADC data from FIFO further increasing bandwidth and reducing complexity.

- Burst mode with only one interrupt generated per complete scan, thus reducing interrupt overhead and increasing effective throughput.

- One interrupt per 512-samples is possible in FIFO mode

- On-board LED to indicate that the STX104 is being addressed. By observing the LED you can quickly determine system activity.

- Polarized locking I/O connector. This eliminates board failures due to incorrect connector orientation.

- Extremely low DC drift

- External trigger input (DIN0) is deglitched preventing unwanted ADC triggers. Minimum valid pulse width required is 200nS.

- Industrial temperature range from -40°C to +85°C

- No tantalum capacitors or electrolytic capacitors used in the design

- Single +5V supply operation

#### New Features as of February 14, 2008 (Revision 080407H)

• Supports both 8- and 16-bit PC/104 data busses

- Supports 10-bit or 16-bit I/O addressing via jumper using jumper M4. DAS1602 register set located at base\_address + 0x400 are also now relocated in an indexed register spaced within the 10-bit address space.

- Improved I/O wait states as well as wait state reduction supporting higher speed CPUs along with improved PC/104 bus throughput.

- New triggering subsystem ( see page 97)

- Trigger Start. 14 selectable events.

- Trigger Stop. 15 selectable events.

- Trigger Sync. Trigger Sync. 12 selectable events.

- Synchronization via external signal sources (i.e. 60Hz)

- Three possible triggering sequences.

- · Trigger delay timer.

- Interrupts ( see page 90)

- More IRQ lines supported including IRQ9, IRQ10, IRQ11, IRQ12, IRQ14 and IRQ15.

- Two additional interrupt sources. Each has 13 selectable events.

- Interrupt source status available at one location for faster interrupt service routines.

- Interrupt threshold counter ( see page 92) for multiple events per interrupt. 13 selectable events.

- Interrupts can be synchronized to trigger start event.

- Number of analog input data blocks per FIFO interrupt is now adjustable (two methods possible).

- Digital Outputs ( see page 94)

- · Polarity control.

- Digital Inputs ( see page 96)

- · Polarity control.

- Long (200 nSec) or short (100 nSec) deglitch filter.

- Analog Inputs

- Sampling sources ( see page 100). 11 selectable source (all legacy functions have been preserved).

- 32-bit intra-sample burst timer ( see page 105) with resolution to 25 nanoseconds for improved timing between samples in ADC-burst mode.

- Non-synchronization/synchronization with trigger start ( see page 100). In other words, sample timing can remain at fixed intervals regardless of triggering start event or be synchronized to the triggering start event, respectively.

- 32-bit frame timer (🗷 see page 104) with resolution 25 nanoseconds. ADC-Burst sample sequences or ADC-sampling can be controlled by this 32-bit timer.

- 32-bit burst (intra-sample) timer (☑ see page 105) with resolution to 25 nanoseconds. This timer is used to adjust the timing between ADC-samples during an ADC-Burst operation (i.e. one or more channels collected at a time).

- 32-bit maximum frame counter ( see page 108). This counter can be used to count the number of ADC-samples or ADC-bursts and when the count has reached a user defined limit, this event can be used to generate interrupts or trigger stop situations. Thus, it is now possible to collect N-number of samples into the large FIFO memory and stop collecting after a given interval of time with little software overhead.

- · Other improvements

- FIFO status (

see page 69) values are now properly latched and in addition, the block count will not incorrectly report

values.

- DIN3 and DIN1 (a see page 96) the user can reverse the swapped positions of these inputs.

- An additional high speed FIFO can be enabled ( see page 112) between STX104 main memory and the ISA bus, further

reducing and/or eliminating wait state (IOCHRDY) conditions.

- · All status registers are properly latched as well to prevent change in values during a bus read cycle.

- I/O Read line is digitally filtered to support noisy bus problems and eliminate the possibility of dropped analog input data.

- Indexed register array banked over the 8254 registers. This opens the door for many new functions as described above.

- Moving average filter has been corrected to present channel data in the proper order.

#### Update as of January 15, 2008 (Revision 090115H)

8254 Counter/Timer is also available within the indexed register set. This allows software access to all registers when the indexed register set is enabled.

#### Update as of March 28, 2012 (Revision 120328H)

- Analog Inputs Bit pattern encoding ( see page 103). This has been implemented to further reduce CPU post processing of data samples and provide maximum flexibility.

- Two's complement or straight binary ADC output encoding.

- Polarity (i.e. multiply by -1) of selected channels for both straight binary and two's complement encoding.

- Absolute value is possible using two's complement encoding scheme.

- Analog output update latency has been reduced from 5 uS to 2.6 uS.

#### Update as of March 28, 2012 (Revision 120328H)

Analog output update latency has been reduced from 5 uS to 2.6 uS.

#### Update as of October 23, 2016 (Revision 161023)

- · DMA features have been removed

- Moving Average filter has been improved

- · Status LED for CPLD

#### NEW REVISION INFORMATION (October 23, 2016 and beyond)

| Date             |     | PCB Date<br>Code | CPLD Date<br>Code | FPGA Date<br>Code | Description                                                                     |

|------------------|-----|------------------|-------------------|-------------------|---------------------------------------------------------------------------------|

| November<br>2016 | 2,  | 160923           | 161101            | 161102            | Original release of firmware                                                    |

| December<br>2016 | 21, | 160923           | 161221            | 161221            | Recompiled revision                                                             |

| March 7, 2017    | 7   | 161023           | 161219            | 170307            | FPGA has counter timer read back fixed                                          |

| March 7, 2017    | 7   | 161023           | 161219            | 170307            | FPGA has counter timer read back fixed                                          |

| November<br>2017 | 15, | 161023           | 161219            | 171115            | FPGA has index pointer read back issue fixed and also has valid LED blink fixed |

Copyright © 2003-2018 by Apex Embedded Systems LLC. All rights reserved.

**Please note** that all of the new registers are designed such that if they are not configured, everything defaults to the classic modes of operation. Thus, existing software will function without modification. Writing values to the new registers enhances operations.

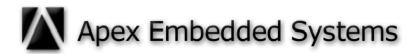

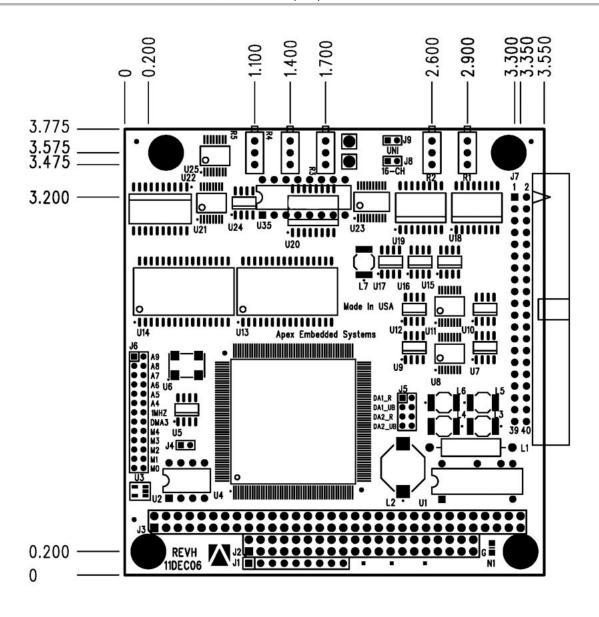

## 3.2 Photo

#### NOTES:

J1 is CPLD JTAG connector used during manufacturing only.

J10 is FPGA JTAG connector used during manufacturing only.

J11 is an optional alternate pin to wire I/O connector in 2mm format. Contact factory for further details.

## 4 Errata

Addresses known board related issues and includes methods to work around the issues.

### **Description**

When the STX104 is operating in DAS16Jr/16 or DAS1602 mode the ADC Status Register bit 5 reports back a 0 for 16 single ended and a 1 for differential mode. The original DAS16Jr/16 or DAS1602 boards report a 1 for single ended and 0 for differential mode.

--- end

## **5 ESD Caution**

A discharge of static electricity from your hands can seriously damage certain electrical components on any circuit board. Before handling any board, discharge static electricity from yourself by touching a grounded conductor such as your computer chassis (your computer must be turned off). Whenever you handle a board, hold it by the edges and avoid touching any board components or cable connectors.

# 6 PC/104 Insertion Caution

Before powering up the PC/104 stack...

and look for proper PC/104 connector alignment.

This simple step will prevent permanent board damage.

Helpful hint: During system prototyping install the spacers to help guide installation and provide another means of checking board alignment. We recommend having the bolt end of the spacer facing up to act as a guide or alignment pin.

## 7 Definitions

Definition of terms.

## 7.1 ADC-Sample

Analog Input sample or data from an individual analog input channel.

## 7.2 ADC-Burst

A group of analog input samples defined by the number of channels for a burst operation. When an ADC-burst is started, the timing between samples is controlled by the Analog Input Burst Timer ( see page 105) or in classic mode it is defined strictly as 5 microseconds.

## 7.3 Analog Input Sample Event

Analog Input Sample Event is a signal that causes either an analog input sample or analog input burst, depending on how the STX104 is set up.

## 7.4 Frame

A Frame is a generalized term. This is the record that is deposited per frame time into the FIFO memory. Currently, a frame is the equivalent to an ADC-Burst in terms of the amount of samples stored in the FIFO.

## 7.5 Intra-Sample

Intra-sample refers to time between analog input samples within an ADC-burst operation.

## See Also

Analog Input Burst Timer ( see page 105)

# 8 Analog Inputs

### 8.1 Calibration

### **Description**

Assumption: Using default legacy Straight-Binary data encoding (data format).

Perform the following procedure to adjust ADC input. We recommend averaging ADC values over at least 256 samples in order to provide the most accurate calibration possible, reference the Voltage Input Conversion section under the ADC Data Register ( see page 48) description. Full scale or gain calibration relies on the use of an external precision voltage source (or one can use a DAC output for this purpose as well).

- 1. Select the desired input mode by configuring J8 for differential or single-ended inputs.

- 2. Select the desired input range by configuring J9 for unipolar or bipolar inputs.

- 3. Calibration of potentiometer PGA\_OFF (R3), if present. If R3 is not present, then skip to step #4 below.

- 1. Short J7 pin 36 to J7 pin 37. In the case of differential inputs (J8 not stuffed), also short J7 pin 35 to J7 pin 37.

- 2. Using a voltmeter connected to the two test points VPGA and AGND, adjust R3 to obtain zero volts (+/- 1 LSB).

- 4. Set the desired gain by writing to the ADC Configuration Register (☐ see page 72) (base\_address + 11) to the desired ADC input gain.

- 5. Set the ADC Channel Register ( see page 54) (base\_address + 2) to zero so that we are observing input channel zero.

- 6. Offset Adjustment.

- In the case of single-ended inputs (jumper J8 installed), short J7 pin 36 to J7 pin 37; effectively connecting the single-ended input to analog ground. In the case of differential inputs (jumper J8 not installed), short J7 pin 35 and pin 36 to J7 pin 37; effectively connecting the differential input to analog ground.

- 2. While performing ADC conversions and reading the ADC value, adjust potentiometer ADC\_OFFSET (R4) until the nearest zero value can be achieved, typically within one ADC step or LSB.

- 7. Remove all jumpers from the I/O connector at J7.

- 8. Gain Adjustment.

- 1. In the case of single-ended inputs (jumper J8 installed), connect J7 pin 36 to the full scale voltage source. In the case of differential inputs (jumper J8 not installed), connect J7 pin 35 to J7 pin 37 and J7 pin 36 to the full scale voltage source. Adjust the DAC output for ADC full-scale input minus two LSB. Measure this value using a calibrated voltmeter to the accuracy you require.

- While performing ADC conversions and reading the ADC value, adjust potentiometer ADC\_GAIN (R5) until full scale minus two LSB is achieved. This can be achieved through averaging ADC values. Please reference ADC Conversion Register for software example on how to average data.

Copyright © 2003-2018 by Apex Embedded Systems LLC. All rights reserved.

- 9. Remove all jumpers from the I/O connector at J7.

- 10. Repeat steps 5 through 8 until the ADC input is calibration to within the accuracy you need or +/- 2 LSB.

## 8.2 Connectivity

## 8.2.1 Single-Ended

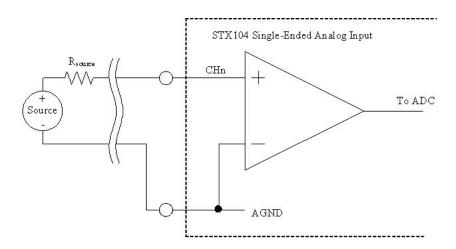

Single-ended analog inputs.

## **Description**

A single-ended input channel consists of one input. The output is the difference between the input and AGND (common).

#### **Jumper Setup**

J8 jumper must be installed for single-ended mode of operation. This also configures the STX104 card for sixteen analog input channels.

#### **Amplifier Bias Currents**

The primary path of amplifier bias currents is the AGND (or common) and since the source is tied to AGND amplifier bias currents flow through the sensor to AGND. Amplifier bias currents are typically on the order of tens of nano-amps.

#### **Source Resistance**

Source resistance Rsource along with cable and input parasitic capacitances must be taken into considered to determine minimum settling time. More details can be found here ( see page 105).

#### **Input Ranges**

The input ranges for single-ended inputs.

| SINGLE-ENDED INPUT RANGE ( CHn) | RESOLUTION | UNIPOLAR/BIPOLAR (J9) | ACFG.ADBU | ACFG.G1 | ACFG.G0 |

|---------------------------------|------------|-----------------------|-----------|---------|---------|

| +/- 10 V                        | 305 uV     | J9 not installed      | 0         | 0       | 0       |

| +/- 5 V                         | 153 uV     | J9 not installed      | 0         | 0       | 1       |

| +/- 2.50 V                      | 76 uV      | J9 not installed      | 0         | 1       | 0       |

| +/- 1.25 V                      | 38 uV      | J9 not installed      | 0         | 1       | 1       |

| 0 to +10 V                      | 153 uV     | J9 installed          | 1         | 0       | 0       |

| 0 to +5 V                       | 76 uV      | J9 installed          | 1         | 0       | 1       |

| 0 to +2.5 V                     | 38 uV      | J9 installed          | 1         | 1       | 0       |

| 0 to +1.25 V                    | 19 uV      | J9 installed          | 1         | 1       | 1       |

NOTE: Analog Configuration Register (ACFG) ( see page 72)

#### **Advantages**

- · More analog input channels available

- · Less wiring and lower cost

#### **Disadvantages**

• Since all inputs are referred to AGND (i.e. common) the possibility exists for ground loops or voltage drops along common connections which will add to noise or measurement errors.

### 8.2.2 Differential

Full differential analog inputs.

### **Description**

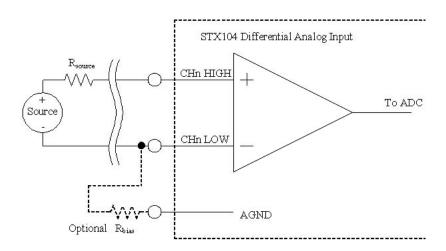

A differential analog input channel consists of two inputs, high side (positive) and low side (negative). The output measured is the difference between the two inputs, thus rejecting signals that are common to both inputs. In many situations this offers additional noise immunity to the signal of interest. The image below illustrates how to interface a sensor to a differential input channel.

Copyright © 2003-2018 by Apex Embedded Systems LLC. All rights reserved.

#### **Jumper Setup**

J8 jumper must be removed for differential mode of operation. This also configures the STX104 card for eight analog input channels.

#### **Optional Rbias**

All analog inputs require a small amount of bias current, on the order of tens of nano-amps. If the sensor or signal source is not referenced to the STX104 AGND or system power supply then a resistor must be tied from one of the differential leads to AGND. The resistor value range is typically 100K ohms down to 100 ohms, depending on the application and the actual input bias current required. In most cases a 10K ohm resistor will do and will add less than +/-50uV of common-mode due to the bias current. Actually, the R<sub>bias</sub> value could be as low as zero ohms, but using zero ohms you are reverting to single-ended behavior.

#### **Source Resistance**

Source resistance Rsource along with cable and input parasitic capacitances must be taken into considered to determine minimum settling time. More details can be found here ( see page 105).

#### **Input Ranges**

The input ranges for each half of the differential input along with the full differential input range.

| DIFFERENTIAL INPUT<br>RANGE<br>( (CHn High) - (CHn<br>Low) ) | RESOLUTION | UNIPOLAR/BIPOLAR<br>(J9)   | ACFG.ADBU | ACFG.G1 | ACFG.G0 | CHn<br>HIGH<br>RANGE | CHn<br>LOW<br>RANGE |

|--------------------------------------------------------------|------------|----------------------------|-----------|---------|---------|----------------------|---------------------|

| +/- 10 V                                                     | 305 uV     | J9 not installed (bipolar) | 0         | 0       | 0       | +/- 10 V             | +/- 10 V            |

| +/- 5 V                                                      | 153 uV     | J9 not installed (bipolar) | 0         | 0       | 1       | +/- 5 V              | +/- 5 V             |

| +/- 2.50 V                                                   | 76 uV      | J9 not installed (bipolar) | 0         | 1       | 0       | +/- 2.5<br>V         | +/- 2.5<br>V        |

| +/- 1.25 V   | 38 uV  | J9 not installed (bipolar) | 0 | 1 | 1 | +/-<br>1.25 V | +/-<br>1.25 V |

|--------------|--------|----------------------------|---|---|---|---------------|---------------|

| 0 to +10 V   | 153 uV | J9 installed (unipolar)    | 1 | 0 | 0 | 0 - 10 V      | 0 - 10 V      |

| 0 to +5 V    | 76 uV  | J9 installed (unipolar)    | 1 | 0 | 1 | 0 - 5 V       | 0 - 5 V       |

| 0 to +2.50 V | 38 uV  | J9 installed (unipolar)    | 1 | 1 | 0 | 0 - 2.5<br>V  | 0 - 2.5<br>V  |

| 0 to +1.25 V | 19 uV  | J9 installed (unipolar)    | 1 | 1 | 1 | 0 -<br>1.25 V | 0 -<br>1.25 V |

NOTE: Analog Configuration Register (ACFG) ( see page 72)

#### **Input Total Range**

Need some images or graph to illustrate more clearly what is happening. Need to illustrate how the unipolar 0-5V can slide up and down the -10V to +10V region and so on. How to illustrate this sliding around business. Maybe a CHn\_High vs CHn\_Low vs ADC value. Perhaps a 3-D plot where X=CHn\_HIGH, Y=CHn\_LOW, Z=ADC

$$ADC = (VH - VL);$$

#### **Example Applications**

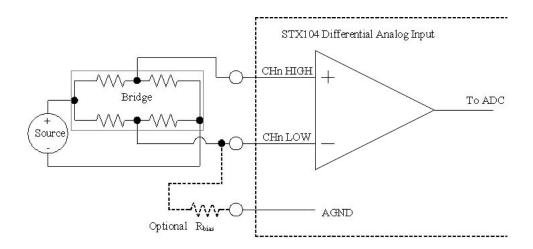

To measure the output of a bridge network as shown in the diagram below. When the bridge is balanced, the common mode voltage at both the positive and negative inputs of the differential input are the same. Thus, the STX104 will report zero volts output (0x8000 in straight binary). Note that the voltage driving the bridge will be ratiometric at the outputs and thus nulled at the output.

Copyright © 2003-2018 by Apex Embedded Systems LLC. All rights reserved.

If the negative side of the source driving the bridge is tied to the system supply that supplies power to the STX104, then the R<sub>bias</sub> is not required because input bias currents have a complete DC path. If you are not sure whether your signal source is referenced to the STX104 AGND, power down the system, and using an ohmmeter measure the resistance between STX104 AGND and the common side of your signal source, you will want the resistance to be less than 10K ohms.

#### **Advantages**

- · Common mode rejection

- Signals can be extracted even though there is a common mode voltage

- typically improves noise immunity

- · Can perform ratiometric measurements

#### **Disadvantages**

- · More wiring

- · Fewer channels available

## 8.3 Data Acquisition Modes

## **Description**

The following functions are available for each of the data acquisition modes:

- The timing between samples and frames (i.e. ADC-burst) are adjustable to 25 nanosecond resolution via 32-bit timers.

- Analog Input Frame ( see page 15) timing can be selected from a variety of sources including:

- External digital input (i.e. GPS pulses or other precision synchronizing timing sources)

- Triggering subsystem. Triggering starts and stops can originate from internal or external events.

- Interrupt subsystem. Variety of interrupts can be generated based on both internal and external events.

- · Moving average filter.

### 8.3.1 Classic DAS16jr/16

- · Single ADC-sample per analog input sample event.

- Analog input sampling events enhanced from 3 to 13 possible sources.

- Supports DMA (see note).

### **Description**

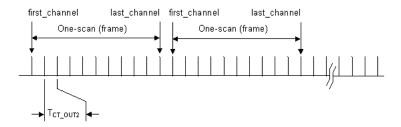

The DAS16jr/16 mode is the simplest of all STX104 modes, and this mode is compatible with many other cards. In this case, as seen by the illustration below, sampling is equally spaced. If phase delay between channels is not important, this mode offers maximum settling time between channels.

#### NOTES:

- (1) T<sub>CT\_OUT2</sub> = Intra-sample timing set by the 8254 Counter 1 and Counter 2. Minimum

- sample timing allowed is 5 microseconds.

- (2) One scan or frame time will be the number of channels times T<sub>CT\_OUT2</sub>.

- (3) Sample timing can be gated by GCTRL bit in the Pacer Clock Control Register along with the ALSS[1:0] bits found in the ADC Control Register.

This mode typically uses the 8254 timer to set the sampling rate, however, other sampling sources can now be configured via the Analog Input General Configuration Register ( see page 100). The frame counter ( see page 109) will actually count samples rather than frames, and the Analog Input Frame Timer ( see page 104) will produce the timing for each sample rather than each frame.

### 8.3.2 Classic DAS1602

- · ADC-sample per analog input sample event.

- ADC-burst (one or more channels collected) per analog input sample event. Timing between ADC-samples within a burst are adjustable from 5 microseconds to 53 seconds to 25 nanosecond resolution.

- Analog input sampling events enhanced from 3 to 13 possible sources.

- · Large FIFO depth allows for greater interrupt latency or readout latency.

- · Supports DMA (see note).

### Description

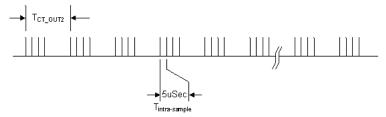

The DAS1602 mode is a step up from the DAS16jr/16 mode in that this mode additionally supports ADC-bursting. In other words, one sample strobe will produce and ADC-burst or one complete scan from the *first\_channel* ( see page 54) to the *last\_channel* ( see page 54).

NOTES:

- (1) TCT\_OUT2 = frame (adc-burst) time set by the 8254 Counter 1 and Counter 2.

- (2) Tintra-sample = fixed to 5 microseconds only.

- (3) One scan or frame time will be T<sub>CT\_OUT2</sub> or the number of channels times 5uSec which ever is largest.

- (4) Sample timing can be gated by GCTRL bit in the Pacer Clock Control Register along with the ALSS[1:0] bits found in the ADC Control Register.

This mode typically uses the 8254 timer to set the sampling rate, however, other sampling sources can now be configured via the Analog Input General Configuration Register ( see page 100). The frame counter ( see page 109) will actually count samples rather than frames, and the Analog Input Frame Timer ( see page 104) will produce the timing for each sample rather than each frame.

### See Also

Conversion Disable ( see page 84)

Burst Mode Enable ( see page 85)

Burst Function Enable ( see page 86)

Extended Status ( see page 86)

Analog Input Burst Timer ( see page 105)

## 8.3.3 Continuous High Speed Sampling

- · CPU read-out N-blocks of data per unit of time (i.e. CPU-burst reads)

- Sample timing and intra-sample timing in ADC-burst modes adjustable to 25 nanosecond resolution.

- FIFO interrupt generated interrupts and events are very flexible and support optimal CPU bursting (ultimately dependent on other CPU overhead or rhythmic behavior such as flash drives).

- Data fragment buffer reduces PC/104 generated IOCHRDY or wait conditions, further enhancing PC/104 data bus throughput.

- Large FIFO depth enhances the time decoupling between CPU activities and precise sample timing.

### **Description**

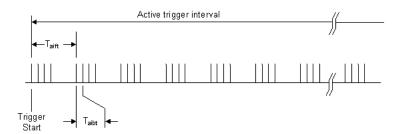

NOTES:

- (1) T<sub>aint</sub> = frame (adc-burst) time set by the Analog Input Frame Timer Register

(2) T<sub>aibt</sub> = intra-sample time set by the Analog Input Burst Timer Register

(3) In this illustration the Analog Input Frame Maximum is set to 4 frames (i.e. ADC-bursts).

(3) Trigger start selected by STS[3:0] bits in the Trigger Configuration Register.

(4) Trigger stop selected by ETS[3:0] bits in the Trigger Configuration Register. In this illustration, trigger stop is selected to be the Analog Input Frame Maximum.

- (5) It is possible to delay sampling after trigger start by introducing Trigger Delay.

(6) In this illustration the Analog Input Frame Timer and the Analog Input Frame Counter are synchronized to the trigger start (SAIFTTS='1' and SAIFCTS='1' in the Analog Input General Configuration Register).

### See Also

FIFO Status MSB ( see page 69)

Interrupt Configuration ( see page 90)

## 8.3.4 Start/Stop-Trigger Encased Frame Groups

- Start-Trigger to begin sampling, then Stop-Trigger to stop sampling. Repeat sequence.

- · Large FIFO depth offers ability to collect large groups of data with a post-readout scheme.

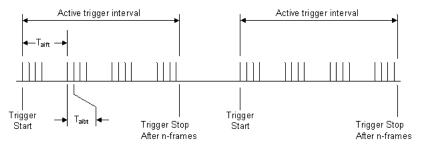

## **Description**

The most generalized sampling scheme is illustrated below.

- NOTES:

(1) T<sub>aint</sub> = frame (adc-burst) time set by the Analog Input Frame Timer Register

(2) T<sub>aint</sub> = intra-sample time set by the Analog Input Burst Timer Register

(3) In this illustration the Analog Input Frame Maximum is set to 4 frames (i.e. ADC-bursts).

(3) Trigger start selected by STS[3:0] bits in the Trigger Configuration Register.

(4) Trigger stop selected by ETS[3:0] bits in the Trigger Configuration Register.

In this illustration, trigger stop is selected to be the Analog Input Frame Maximum.

(5) It is possible to delay sampling after trigger start by introducing Trigger Delay.

- (6) In this illustration the Analog Input Frame Timer and the Analog Input Frame Counter are synchronized to the trigger start (SAIFTTS='1' and SAIFCTS='1' in the Analog Input

### See Also

Trigger Configuration ( see page 97)

Analog Input Frame Maximum ( see page 108)

### 8.3.5 N-Sample Collection

- Start-Trigger to begin sampling, stop sampling when N-samples/-Frames reached (i.e. Stop-Trigger event).

- · Large FIFO depth offers set it and forget it methodology, thus drastically reducing CPU software monitoring overhead.

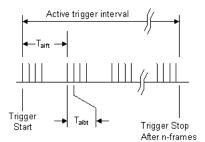

### **Description**

- (1) Taift = frame (adc-burst) time set by the Analog Input Frame Timer Register

- (2) Tabt = intra-sample time set by the Analog Input Burst Timer Register

(3) In this illustration the Analog Input Frame Maximum is set to 4 frames (i.e. ADC-bursts).

(3) Trigger start selected by STS[3:0] bits in the Trigger Configuration Register.

(4) Trigger stop selected by ETS[3:0] bits in the Trigger Configuration Register.

In this illustration, trigger stop is selected to be the Analog Input Frame Maximum.

(5) It is possible to delay sampling after trigger start by introducing Trigger Delay.

- (5) It is possible to delay sampling after trigger start by introducing Trigger Delay. (6) In this illustration the Analog Input Frame Timer and the Analog Input Frame Counter are synchronized to the trigger start (SAIFTTS='1' and SAIFCTS='1' in the Analog Input

#### See Also

Analog Input Frame Maximum ( see page 108)

## 8.4 Analog Input Sample Timing

### **Description**

The example below illustrates various methods of setting up analog input sample timing. There are two primary parameters needed to setup timing: time between frames, and time between samples (i.e. ADC-burst timing).

One must call the STX104\_AI\_Time\_Settling\_Minimum() function to determine the minimum timing possible between samples or the intra-sample timing or minimum ADC-burst timing.

The functions within the example code below will compute and configure the proper analog input timing registers based on firmware revision level. If only 8254 timers are used, then resolution is fixed to 1uSec. In the case of using the Analog Input Frame Timer ( see page 104) and the Analog Input Burst Timer ( see page 105), resolution is improved to 25 nanoseconds.

When using the triggering subsystem, to synchronize analog input sampling to the trigger-start event, set the SAIFTTS bit in the Analog Input General Configuration ( see page 100) Register.

Method for configuring the Analog Input Frame Timer ( see page 104) and the Analog Input Burst Timer ( see page 105) registers.

- a) Our assumption is that ADC-burst mode will always be enabled, and is acceptable for all situations.

- b) First calculate the time between samples (i.e. intra-sample time) in the the ADC-burst mode. The timing can be as short as 5uSec or longer. The timing is based on multiplexer settling time.

If you have a sensor with a source resistance of 10Kohms and a cable with a total capacitance of 100pF, then the minimum time between samples will be approximately 11 \* 10Kohms \* 100pF = 11,000 nSec. In other words, the minimum settling time is eleven RC time constants.

```

ai\_time\_intra\_sample\_ns = AIBT\_Register\_Value * ( 25 nSec ) + ( 5000 nSec ).

```

```

AIBT_Register_Value = ( ai_time_intra_sample_ns / ( 25 nSec ) ) - 200

```

c) The minimum frame time will be:

```

minimum_ai_time_frame_ns = ( last_channel - first_channel + 1 ) * ai_time_intra_sample_ns.

```

d) The frame time can now be computed:

```

ai_time_frame_ns = ( AIFT_Register_Value + 1 ) * ( 25 nSec )

```

```

AIFT_Register_Value = ai_time_frame_ns * ( 25 nSec ) - 1

```

The above example is a summary of the example source code below.

### **Example**

```

#define STX104_INTRA_SAMPLE_TIMING 5000 /* nanoseconds */

#define STX104_TIME_RESOLUTION 25 /* nanoseconds */

#define STX104_REVISION_080214 0x1008

#define STX104_REVISION_080407 0x1008

#define STX104_REVISION_090115 0x1009

```

```

ANALOG INPUT TIMING FUNCTIONS

*/

*******************

ANALOG INPUT MINIMUM SETTLING TIME

*/

static unsigned long STX104_AI_Time_Settling_Minimum( float ai_capacitance_pf, float

ai resistance ohms )

unsigned long settle_time_ns;

//settle_time = ai_resistance_ohms * ai_capacitance_pf * pow10(-12) * 16 * ln(2) * pow10(9)

settle_time_ns = (unsigned long) ( ai_resistance_ohms * ai_capacitance_pf * pow10(-3) * 16

* log(2) );

return( settle_time_ns );

/***********************

ANALOG INPUT 8254 TIMING

static void STX104_AI_Timing_8254_Set( int board, long time_interval_ns )

long high_count;

long low_count;

unsigned int octet;

STX104_Set_Bank( board, 0 );

/* assumes 10MHz clock (i.e. no 1MHz jumper) */

low_count = 10L; /* 1 microsecond intervals */

high_count = time_interval_ns / 1000;

while ( high_count > 65536L )

high_count = high_count >> 1;

low_count = low_count << 1;</pre>

while ( high_count < 2L )</pre>

high_count = high_count << 1;

low_count = low_count >> 1;

/* set counter/timer 2 */

outportb( stx104_base_address[board] + STX104_CT_CONFIGURATION, 0xB4 );

octet = ((unsigned int) high_count) & 0x00FF;

outp( stx104_base_address[board] + STX104_CT2_DATA, octet );

octet = ((unsigned int) high_count) >> 8;

outp( stx104_base_address[board] + STX104_CT2_DATA, octet );

/* set counter/timer 1 */

outportb( stx104_base_address[board] + STX104_CT_CONFIGURATION, 0x74 );

octet = ((unsigned int) low_count) & 0x00FF;

outp( stx104_base_address[board] + STX104_CT1_DATA, octet );

octet = ((unsigned int) low_count) >> 8;

outp( stx104_base_address[board] + STX104_CT1_DATA, octet );

/*************************

ANALOG INPUT GENERAL TIMING

static void STX104_AI_Timing_Set( int board, unsigned long ai_time_frame_ns, unsigned long

ai_time_intra_sample_ns )

unsigned int adc_burst_channel_count;

```

```

switch ( stx104_revision[board] )

case STX104_REVISION_080214:

/* same as version 080407 */

case STX104_REVISION_090115:

STX104_Set_Bank( board, 1 );

STX104_Write_Indexed_Data_Byte( board, STX104_BURST_FUNCTION_ENABLE_INDEXED, 0x40

);

STX104_Write_Indexed_Data_Byte( board, STX104_BURST_MODE_ENABLE_INDEXED,

0x40

);

STX104_Write_Indexed_Data_Byte( board, STX104_CONVERSION_DISABLE_INDEXED,

0x00

);

adc_burst_channel_count = (unsigned char)( 0x0F & ( stx104_ai_channel_last[board]

- stx104_ai_channel_first[board] ) );

adc_burst_channel_count = adc_burst_channel_count << 4;</pre>

outp( stx104_base_address[board] + STX104_PACER_CLOCK_CONTROL,

adc_burst_channel_count );

/* the following registers require the number of 25nSec intervals to achieve the

selected timing */

STX104_Write_Indexed_Data_Dword( board, STX104_ANALOG_INPUT_FRAME_TIMER, (

ai_time_frame_ns/STX104_TIME_RESOLUTION ) );

STX104_Write_Indexed_Data_Dword( board, STX104_ANALOG_INPUT_BURST_TIMER, (

(ai_time_intra_sample_ns - STX104_INTRA_SAMPLE_TIMING) / STX104_TIME_RESOLUTION ) );

break;

default:

if ( ai_time_intra_sample_ns > STX104_INTRA_SAMPLE_TIMING /*nS*/ )

cannot use adc-burst mode */

STX104_AI_Timing_8254_Set( board, ai_time_intra_sample_ns );

outp( stx104_base_address[board] + STX104_BURST_FUNCTION,

0x00);

0x00);

outp( stx104_base_address[board] + STX104_BURST_MODE_ENABLE,

outp( stx104_base_address[board] + STX104_CONVERSION_DISABLE,

0x00);

else

/* utilize adc-burst mode */

STX104_AI_Timing_8254_Set( board, ai_time_frame_ns );

outp( stx104_base_address[board] + STX104_BURST_FUNCTION,

0x40 );

outp( stx104_base_address[board] + STX104_BURST_MODE_ENABLE,

0x40 );

outp( stx104_base_address[board] + STX104_CONVERSION_DISABLE,

0x00);

adc_burst_channel_count = (unsigned char)( 0x0F & (

stx104_ai_channel_last[board] - stx104_ai_channel_first[board] ) );

adc_burst_channel_count = adc_burst_channel_count << 4;</pre>

outp( stx104_base_address[board] + STX104_PACER_CLOCK_CONTROL,

adc_burst_channel_count );

```

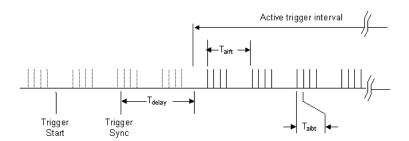

## 8.5 Triggering Subsystem

### **Description**

The triggering subsystem is used to start and stop analog input sampling. This is a new generalized triggering system. Please refer to Trigger Configuration (as see page 97) and Trigger Start Delay (as see page 99) Registers for further details.

The Analog Input General Configuration ( see page 100) Register bit nSGATE is used to enable triggering subsystem use. The

nSGATE bit is required in order to support classic modes without special configuration.

Further, the triggering subsystem must be enabled in order for it to function.

There are three start triggering sequences:

- 1. Start trigger source --> Analog Input Sampling Begins

- 2. Start trigger source --> Trigger Delay --> Analog Input Sampling Begins

- 3. Start trigger source --> Start Trigger Synchronization source --> Trigger Delay -- > Analog Input Sampling Begins.

Analog input sampling is stopped upon a valid End/Stop Trigger Source event.

What is the purpose of the triggering subsystem? It allows precise control as to when analog input sampling can occur. It is possible to synchronize sampling to 60Hz line source or whatever is chosen. It is possible to configure the STX104 to trigger on an event and accumulate N-samples and then stop sampling.

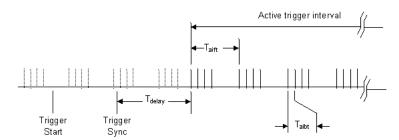

#### Synchronization of Analog Input Frame Timer to Trigger Start (SAIFTTS)

The diagrams below illustrate how sample timing is affected by the SAIFTTS bit found in the Analog Input General Configuration Register.

#### NOTES:

- (1) SAIFTTS='1' which means that the analog input frame timer is synchronized to the beginning of the active trigger. of triggering. The triggering acts essentially as a mechanism to gate the analog input frame timer.

- (2) The greyed sampling shows the timing from the previously triggered sampling interval and how the timing is affected.

NOTES:

- (1) SAIFTTS='0' which means that the frame timer runs independent of triggering. The triggering acts essentially as a mechanism to gate the analog input frame timer.

- (2) The grayed sampling shows the timing from the previously triggered sampling interval and how frame timing is maintained independent of the trigger.

#### See Also

Trigger Configuration ( see page 97)

## 8.6 Moving Average Filter

### **Description**

Installing jumper M3 enables the 16-sample moving average filter for all channels. The filter can be reset (or cleared) by writing to the Channel Register. The moving average filter is enabled for all channels and operates completely transparent to ADC acquisition modes. The ADC values read out will be the current sample plus the last fifteen samples summed together and divided by sixteen (average of sixteen ADC samples). It is important to recognize that after the filter is reset or at the beginning of data sampling that it may require at least 16-data samples per channel be taken until the data becomes current. In other words, there is an inherent 16-sample delay in the ADC data that is read out of the ADC Data Register.

## 8.7 CPU Readout Methods

### 8.7.1 DMA Read

Analog input data is read from the FIFO memory via Direct Memory Access (DMA). This section only applies to Revision 120328 and prior, Revision 161023 and after does NOT support DMA.

### **Description**

8.7 CPU Readout Methods

We strongly encourage you to use the REP INSW instruction (or Insw() function in Linux) as it performs better than DMA and is substantially simpler to set up and use. Note that DMA performs I/O to memory transfers a byte at a time (DMA 1 and DMA 3 are byte wide transfers) while REP INSW performs I/O to memory transfers a word at a time. If you are designing a real-time system, you will have better timing control over your system by using REP INSW instruction over DMA. Since processor generated I/O cycles are faster than DMA generated cycles (typically 350ns versus 800ns), data transfer can take place faster than DMA. Note that 8-bit bus transactions (including DMA) are typically at least twice as long as 16-bit bus transactions; this alone is reason enough to avoid DMA.

When DMA is enabled, the 1 mega-sample FIFO is used.

In DMA mode, receiving a terminal count from the CPU will generate an interrupt, if the interrupt is enabled. If you are in DAS1602 mode (jumper M0 is installed), receiving a terminal count will set the Conversion Disable bit to false, thus disabling any additional ADC sampling. Writing 0x00 to the Conversion Disable Register ( see page 84) will allow ADC sampling to continue.

In order to use DMA, you must set up the computer's DMA controller and page registers before enabling DMA on the STX104 board.

We consider DMA a deprecated function and in the future should be avoided; it just no longer makes any sense to use.

## 8.7.2 Burst Read

Reading multiple samples one after the other reading out blocks or frames (i.e. ADC-burst) of data in a short interval of time. This is typically done using the REP INSW or Insw() type functions. Refer to the ADC Data Register ( see page 48) for an example.

## 8.7.3 Single Read

Reading an individual sample using either an 8- or 16-bit read cycle. Refer to the the ADC Data Register (2 see page 48) for examples.

## 9 Analog Outputs

## 9.1 Calibration

## **Description**

Hardware configuration:

- 1. Select the desired output range by adjusting jumper settings at J5.

- 2. Install jumper M2 as required for the application (this jumper selects 16-bit versus 12-bit resolution).

Calibration of DAC Channel-A:

- 1. Write 65535 (0xFFFF) to Register DAC Channel-A ( see page 58).

- 2. Adjust potentiometer DA1\_G (R2) until the desired full scale is reached.

Calibration of DAC Channel-B:

- 1. Write 65535 (0xFFFF) to Register DAC Channel-B ( see page 61).

- 2. Adjust potentiometer DA2\_G (R1) until the desired full scale is reached.

## 9.2 Connectivity

## **Description**

Each DAC channel is a single-ended type output. We suggest wiring the return path back to one of the AGND pins at connector J7.

## 10 Hardware Configuration

## 10.1 Base Address Table

Card Base Address set via installing jumpers at J6 positions A9, A8, A7, A6, A5 and A4. Installing jumper M4 will reduce address I/O decode from a full 16-bits to 10-bits, this provides compatibility with CPU cards that only offer 10-address bits for I/O transactions.

### **Description**

| BASE ADDRESS Full 16-bit Address Decode M4 Jumper *not* Installed | BASE ADDRESS<br>10-bit Address Decode<br>M4 Jumper Installed | A9 | A8 | A7 | A6 | A5 | A4 |

|-------------------------------------------------------------------|--------------------------------------------------------------|----|----|----|----|----|----|

| 0x0220                                                            | 0x220                                                        | 1  | 0  | 0  | 0  | 1  | 0  |

| 0x0240                                                            | 0x240                                                        | 1  | 0  | 0  | 1  | 0  | 0  |

| 0x0250                                                            | 0x250                                                        | 1  | 0  | 0  | 1  | 0  | 1  |

| 0x0260                                                            | 0x260                                                        | 1  | 0  | 0  | 1  | 1  | 0  |

| 0x0280                                                            | 0x280                                                        | 1  | 0  | 1  | 0  | 0  | 0  |

| 0x0290                                                            | 0x290                                                        | 1  | 0  | 1  | 0  | 0  | 1  |

| 0x02A0                                                            | 0x2A0                                                        | 1  | 0  | 1  | 0  | 1  | 0  |

| 0x02B0                                                            | 0x2B0                                                        | 1  | 0  | 1  | 0  | 1  | 1  |

| 0x02C0                                                            | 0x2C0                                                        | 1  | 0  | 1  | 1  | 0  | 0  |

| 0x02D0                                                            | 0x2D0                                                        | 1  | 0  | 1  | 1  | 0  | 1  |

| 0x02E0                                                            | 0x2E0                                                        | 1  | 0  | 1  | 1  | 1  | 0  |

| 0x02F0                                                            | 0x2F0                                                        | 1  | 0  | 1  | 1  | 1  | 1  |

| 0x0300*                                                           | 0x300*                                                       | 1  | 1  | 0  | 0  | 0  | 0  |

| 0x0310                                                            | 0x310                                                        | 1  | 1  | 0  | 0  | 0  | 1  |

| 0x0320                                                            | 0x320                                                        | 1  | 1  | 0  | 0  | 1  | 0  |

| 0x0330                                                            | 0x330                                                        | 1  | 1  | 0  | 0  | 1  | 1  |

| 0x0340                                                            | 0x340                                                        | 1  | 1  | 0  | 1  | 0  | 0  |

| 0x0350                                                            | 0x350                                                        | 1  | 1  | 0  | 1  | 0  | 1  |

| 0x0360                                                            | 0x360                                                        | 1  | 1  | 0  | 1  | 1  | 0  |

| 0x0370                                                            | 0x370                                                        | 1  | 1  | 0  | 1  | 1  | 1  |

| 0x0380                                                            | 0x380                                                        | 1  | 1  | 1  | 0  | 0  | 0  |

| 0x0390                                                            | 0x390                                                        | 1  | 1  | 1  | 0  | 0  | 1  |

| 0x03A0 | 0x3A0 | 1 | 1 | 1 | 0 | 1 | 0 |

|--------|-------|---|---|---|---|---|---|

| 0x03B0 | 0x3B0 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0x03C0 | 0x3C0 | 1 | 1 | 1 | 1 | 0 | 0 |

| 0x03D0 | 0x3D0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0x03E0 | 0x3E0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0x03F0 | 0x3F0 | 1 | 1 | 1 | 1 | 1 | 1 |

Notes: 1 = Jumper installed, 0 = Jumper not installed.

# 10.2 Compatibility Selection and Extended Functions

### **Description**

#### **10-BIT ADDRESS DECODE**

The STX104 now supports CPU cards which only present the first 10 address lines. Normally, the STX104 will decode all 11 address bits in order to fully decode an I/O command. For 10-bit address decode, the upper 6 address bits are ignored. A 10-bit address decode provides a typical I/O address space from 0x000 to 0x3FF. The DAS1602 burst registers are now alternatively available through indexed register array access.

#### DAS16jr/16 and DAS1602 LEGACY COMPATIBILITY

The STX104 is compatible with DAS16jr/16 and the DAS1602. The DAS16jr/16 mode supports 8-bit or 16-bit systems (XT or AT, respectively). The enhanced register set now supports redirection of the DAS1602 extended burst registers to the indexed array register set thus allowing more addressing and data width options including both XT and AT compatibility. Jumper position M0 selects one of these compatibility modes.

The DAS1602 compatibility offers ADC-sample ( see page 15) and ADC-bursting ( see page 15).

#### DAS16jr/12 LEGACY COMPATIBILITY

The STX104 is compatible with DAS16jr/12. The DAS16jr/12 mode supports 8-bit or 16-bit systems (XT or AT, respectively). To achieve this configuration place a Mode Jumper on M5 and remove mode jumpers from M1 and M0. Do not place a jumper on J9

<sup>\*</sup> Factory Default

#### **FIFO SUPERSET**

Data FIFO superset functionality can be selected for either the DAS16jr/16 or the DAS1602 compatibility modes. The FIFO superset functionality is very similar to other cards on the market. Stuffing jumper position M1 enables FIFO superset functionality. Note that for the DAS1602 compatibility mode, the 1 mega-sample FIFO is enabled, however to maintain register compatibility the FIFO status registers are only visible once the M1 jumper is installed.

The HSFIFOEN bit found in the FIFO Configuration ( see page 112) register can be used to enable a 2048 sample high speed pre-queueing FIFO buffer between STX104 main memory and the ISA bus. In general, this will reduce/eliminate IOCHRDY wait states and improve average system throughput.

#### 12-/16-BIT DAC MODE

The 16-bit DAC mode allows the DAC registers to provide 12-bit legacy functionality as well as full 16-bit DAC functionality. Installing jumper M2 allows for full 16-bit DAC operation.

#### **ADC 16-SAMPLE MOVING AVERAGE FILTER**

Installing jumper M3 enables the 16-sample moving average filter for all channels. The filter can be reset (or cleared) by writing to the Channel Register. The moving average filter is enabled for all channels and operates completely transparent to ADC acquisition modes. The ADC values read out will be the current sample plus the last fifteen samples summed together and divided by sixteen (average of sixteen ADC samples). It is important to recognize that after the filter is reset or at the beginning of data sampling that it may require at least 16-data samples per channel be taken until the data becomes current. In other words, there is an inherent 16-sample delay in the ADC data that is read out of the ADC Data Register.

| MODE                                                                                                                                                                                                                   | М5 | M4 | М3 | M2 | M1 | MO |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|

| 10-Bit Address Decode (A0 through A9 are decoded while A10 to A15 ignored. DAS1602 burst registers available in the indexed register array). If jumper is removed A0 through A10 are decoded while A11 to A15 ignored. |    |    | X  | X  | X  | X  |

| DAS16jr/16 + DAC02 Compatibility                                                                                                                                                                                       | 0  | Х  | Х  | Х  | 0  | 0  |

| DAS1602 Compatibility w/1MegaSample FIFO (Single interrupt per sample during ADC-burst)                                                                                                                                | 0  | X  | X  | X  | 0  | 1  |

| DAS1602 Compatibility and FIFO Status Registers Visible (Single interrupt per ADC-burst completion)                                                                                                                    | 0  | Х  | Х  | Х  | 1  | 1  |

| Enable FIFO Superset Functionality                                                                                                                                                                                     | 0  | Х  | Х  | Х  | 1  | Х  |

| 16-bit DAC Registers                                                                                                                                                                                                   | Х  | Х  | Х  | 1  | Х  | Х  |

| 16-Sample moving average filter for all 8 or 16 ADC channels                                                                                                                                                           |    |    |    | Х  | Х  | Х  |

| DAS16jr/12                                                                                                                                                                                                             | 1  | Х  | Х  | Х  | 0  | 0  |

Note: 1 = Jumper installed, 0 = Jumper not installed.

## 10.3 CPU Limitation Accommodations

### **Description**

The STX104 can support the following CPU card variations:

- 10- or 11-bit Address decoding

- 8- or 16-bit PC/104 data bus (without or with 40-pin connector, respectively).

## 10.4 PC104-DAS16jr/12

### **Description**

Differences Between STX104 and PC104-DAS16Jr/12

- 1. The STX104 has no DMA functions.

- 2. The STX104 has the 40 pin connector rotated with pin 1 being away from the PC104 Connector and away from the card edge. The PC104-DAS16jr/12 cards have pin 1 being near the PC104 Connector and close to the card edge.

- 3. The STX104 supplies -5V on pin 15 of the 40 pin connector where the PC104-DAS16jr/12 has this pin as a no connect.

- 4. The STX104 allows 16 bit bus transactions

- 5. The STX104 channel register(offset 2) has the default value set as 0x00 and the current channel is set to 0 as the default. If the channel low bits are set to a higher value then the channel high bits, the STX104 does not wrap around. If set the channel register(offset 2) is set to 0x03, it will only sample channel 3.

The PC104-DAS16Jr/12 channel register(offset 2) has the default set as 0x03. When this register is written to, the value located in bits 0-3 is set as the current channel. The exception is the default value. Since this value is not set by the user, channel 3 is not set as the current channel and instead the current channel is 0. For this card, when the channel low is set to a lower channel higher then the channel high, it wraps around. For the default value, the channels sample in the following order: 0,3,4,5,6,7,8,9,10,11,12,13,14,15. If the user had written the value 0x03 to the channel register (offset 2), then the channels sample in the following order 3,4,5,6,7,8,9,10,11,12,13,14,15,0.

- 6. The PC104-DAS16Jr/12 has a 512 sample FIFO, while the STX104 has 1 Million sample FIFO.

- 7. The ADC sample limit of the STX104 200K samples per second. The PC104-DAS16Jr/12 can sample at 330K samples per second.

- 8. When changing the gains on the STX104 should be followed by rewriting or updating the channel register. This resets everything and allows the correct data to flow. If this is not done, the first sample of adc data might be sampled in the previous

gain setting. When setting gains on the STX104, we recommend allowing a few hundred mircoseconds for the board to complete this change, if this is not done then the first few samples might have skewed data.

- 9. On the STX104 the CNV goes active while the ADC is busy but it also goes active when writing to the channel register (offset 2). The PC104-DAS16Jr/12 only goes active while the ADC is busy.

- 10. On the STX104, the digital outputs and Counter Timer outputs only go to 3.3 volts. When unprogrammed, the Counter Timer outputs on the STX104 are low. The outputs on the PC104-DAS16Jr/12 are high.

- 11.Upon a bus reset the STX104 8254 timer will reset. The PC104-DAS16Jr/12 8254 does not reset.

## 11 Register Set

## 11.1 Summary

Overview of the STX104 register set.

## **Description**

| Register Name                      | NOTE   | Mnemonic | Size | Direction | Offset | Index | Bank<br>(acr.rb) |

|------------------------------------|--------|----------|------|-----------|--------|-------|------------------|

| Software Strobe ( see page 46)     | (3)(4) | ssr      | BYTE | w         | 0      | -     | X                |

| ADC Data LSB ( see page 47)        |        | adl      | BYTE | r         | 0      | -     | Х                |

| ADC Data MSB ( see page 48)        |        | adh      | BYTE | r         | 1      | -     | Х                |

| ADC Data ( see page 48)            |        | ad       | WORD | r         | 0      | -     | Х                |

| ADC Channel ( see page 54)         |        | achan    | BYTE | rw        | 2      | -     | Х                |

| Digital Outputs (☐ see page 56)    |        | do       | BYTE | w         | 3      | -     | Х                |

| Digital Inputs (≥ see page 57)     |        | di       | BYTE | r         | 3      | -     | Х                |

| DAC Channel-A LSB ( see page 58)   |        | dacal    | BYTE | w         | 4      | -     | Х                |

| DAC Channel-B MSB ( see page 61)   |        | dacah    | BYTE | w         | 5      | -     | Х                |

| DAC Channel-A ( see page 58)       |        | daca     | WORD | w         | 4      | -     | Х                |

| DAC Channel-B LSB ( see page 60)   |        | dacbl    | BYTE | w         | 6      | -     | Х                |

| DAC Channel-B MSB ( see page 61)   |        | dacbh    | BYTE | w         | 7      | -     | Х                |

| DAC Channel-B ( see page 61)       |        | dacb     | WORD | w         | 6      | -     | Х                |

| Clear Interrupts (≥ see page 63)   |        | cir      | BYTE | w         | 8      | -     | Х                |

| ADC Status ( see page 64)          | (4)    | asr      | BYTE | r         | 8      | -     | Х                |

| ADC Control ( see page 66)         | (4)    | acr      | BYTE | rw        | 9      | -     | Х                |

| Pacer Clock Control ( see page 68) |        | pccr     | BYTE | w         | 10     | -     | Х                |

| FIFO Status MSB ( see page 69)     | (2)(4) | fsh      | BYTE | r         | 10     | -     | Х                |

| ADC Configuration (2 see page 72)  | (4)    | acfg     | BYTE | rw        | 11     | -     | Х                |

| 8254 CT0 Data (团 see page 77)      |        | ct0d     | BYTE | rw        | 12     | -     | 0                |

| 8254 CT1 Data ( see page 77)       |        | ct1d     | BYTE | rw        | 13     | -     | 0                |

| 8254 CT2 Data (团 see page 77)      |        | ct2d     | BYTE | rw        | 14     | -     | 0                |

| 8254 Configuration ( see page 77)  |        | ctcfg    | BYTE | w         | 15     | -     | 0                |

| FIFO Status LSB ( see page 80)     | (2)    | fsl      | BYTE | r         | 15     | -     | Х                |

| Index Data LSB ( see page 80)                                            | (5)    | idl    | BYTE  | rw | 12   | -  | 1 |

|--------------------------------------------------------------------------|--------|--------|-------|----|------|----|---|

| Index Data MSB (☑ see page 80)                                           | (5)    | idh    | BYTE  | rw | 13   | -  | 1 |

| Index Data (₂ see page 81)                                               | (5)    | data   | WORD  | rw | 12   | -  | 1 |

| Index Pointer (☑ see page 81)                                            | (5)    | index  | BYTE  | rw | 14   | -  | 1 |

| :::::::: DAS1602 Registers Section :::::::::                             |        |        |       |    |      |    |   |

| Conversion Disable ( see page 84)                                        | (1)    | cdr    | BYTE  | w  | 1028 | -  | Х |

| Burst Mode Enable ( see page 85)                                         | (1)    | bmer   | BYTE  | w  | 1029 | -  | Х |

| Burst Function Enable ( see page 86)                                     | (1)    | bfer   | BYTE  | w  | 1030 | -  | Х |

| Extended Status ( see page 86)                                           | (1)    | esr    | BYTE  | r  | 1031 | -  | Х |

| ::::::::::::::::::: General Section :::::::::::::::::::::::::::::::::::: |        |        |       |    |      |    |   |

| General Configuration (園 see page 87)                                    | (5)    | gcfg   | BYTE  | rw | -    | 0  | 1 |

| Interrupt Source Select ( see page 89)                                   | (5)    | iss    | BYTE  | rw | -    | 2  | 1 |

| Interrupt Configuration (⋑ see page 90)                                  | (5)    | icfg   | WORD  | rw | -    | 4  | 1 |

| Interrupt Threshold ( see page 92)                                       | (5)    | ith    | DWORD | rw | -    | 8  | 1 |

| Digital Output Configuration (Is see page 94)                            | (5)(7) | doc    | WORD  | rw | -    | 12 | 1 |

| Digital Input Configuration (☐ see page 96)                              | (5)    | dic    | BYTE  | rw | -    | 14 | 1 |

| ::::::::::::Triggering Section :::::::::::                               |        |        |       |    |      |    |   |

| Trigger Configuration ( see page 97)                                     | (5)    | tcfg   | WORD  | rw | -    | 16 | 1 |

| Trigger Start Delay (ℤ see page 99)                                      | (5)    | tsd    | DWORD | rw | -    | 20 | 1 |

| ::::::::::::::::: Analog Input Section ::::::::::::::                    |        |        |       |    |      |    |   |

| Analog Input General Configuration (☐ see page 100)                      | (5)(7) | aigc   | WORD  | rw | -    | 32 | 1 |

| Analog Input Polarity ( see page 103)                                    | (7)    | aipol  | WORD  | rw | -    | 34 | 1 |

| Analog Input Frame Timer ( see page 104)                                 | (5)    | aift   | DWORD | rw | -    | 36 | 1 |

| Analog Input Burst Timer ( see page 105)                                 | (5)    | aibt   | DWORD | rw | -    | 40 | 1 |

| Analog Input Frame Maximum (☐ see page 108)                              | (5)    | aifm   | DWORD | rw | -    | 44 | 1 |

| Analog Input Frame Counter (☐ see page 109)                              | (5)    | aifc   | DWORD | r  | -    | 48 | 1 |

| ::::: DAS1602 Redirected Registers Section :::::                         |        |        |       |    |      |    |   |

| Conversion Disable ( see page 84)                                        | (1)(5) | icdr   | BYTE  | w  | -    | 64 | 1 |

| Burst Mode Enable ( see page 85)                                         | (1)(5) | ibmer  | BYTE  | w  | -    | 65 | 1 |

| Burst Function Enable ( see page 86)                                     | (1)(5) | ibfer  | BYTE  | w  | -    | 66 | 1 |

| Extended Status ( see page 86)                                           | (1)(5) | iesr   | BYTE  | r  | -    | 67 | 1 |

| :::::::: 8254 Redirected Registers Section ::::::::                      |        |        |       |    |      |    |   |

| 8254 CT0 Data ( see page 77)                                             | (6)    | ict0d  | BYTE  | rw | -    | 68 | 1 |

| 8254 CT1 Data ( see page 77)                                             | (6)    | ict1d  | BYTE  | rw | -    | 69 | 1 |

| 8254 CT2 Data (2 see page 77)                                            | (6)    | ict2d  | BYTE  | rw | -    | 70 | 1 |

| 8254 Configuration ( see page 77)                                        | (6)    | ictcfg | BYTE  | W  | -    | 72 | 1 |

| :::::::: SPI Master Module Section ::::::::                              |        |        |       |    |      |    |   |

| SPI Configuration                                   | (7) | spicfg  | WORD  | rw | - | 80  | 1 |

|-----------------------------------------------------|-----|---------|-------|----|---|-----|---|

| SPI Half Clock Interval                             | (7) | spihclk | WORD  | rw | - | 82  | 1 |

| SPI Receive FIFO Data                               | (7) | spirx   | BYTE  | r  | - | 84  | 1 |

| SPI Transmit FIFO Data                              | (7) | spitx   | BYTE  | W  | - | 84  | 1 |

| SPI Status                                          | (7) | spistat | BYTE  | r  | - | 85  | 1 |

| SPI Software Chip Select ( see page 43)             | (7) | spics   | BYTE  | W  | - | 85  | 1 |

| ::::::::::::::::::::::::::::::::::::::              |     |         |       |    |   |     |   |

| Miscellaneous Output Configuration (  see page 110) |     | mocr    | BYTE  | rw | - | 208 | 1 |

| FIFO Data Available ( see page 111)                 | (5) | fda     | DWORD | r  | - | 224 | 1 |

| FIFO Configuration (☑ see page 112)                 | (5) | fcfg    | BYTE  | rw | - | 228 | 1 |

| Reserved                                            | -   | -       | BYTE  | rw | - | 240 | 1 |

| Reserved                                            | -   | -       | DWORD | rw | - | 244 | 1 |

| Reserved                                            |     | -       | BYTE  | rw | - | 242 | 1 |

| Scratch Pad (溷 see page 113)                        |     | scr     | WORD  | rw | - | 248 | 1 |

| Board ID (᠌ see page 114)                           | (5) | bid     | WORD  | r  | - | 250 | 1 |

| Reserved                                            |     | -       | DWORD | -  | - | 252 | 1 |

- (1) Available only when jumper M0 is installed.

- (2) Available only when jumper M1 is installed.

- (3) Renamed register to reflect generalizations.

- (4) Additional functionality added

- (5) New register as of February 14, 2008

- (6) New register as of January 15, 2009

- (7) New register or functionality added as of October 21, 2011

### **Example**

```

/* STX104 Register Set Definitions */

#define STX104_SOFTWARE_STROBE

0

/* offset (to be added to the

base address) */

#define STX104_ADC_DATA_LSB

0

#define STX104_ADC_DATA_MSB

1

#define STX104_ADC_DATA

0

#define STX104_CHANNEL

2

#define STX104_DIGITAL_OUTPUTS

3

3

#define STX104_DIGITAL_INPUTS

#define STX104_DAC_CHANA_LSB

#define STX104_DAC_CHANA_MSB

5

#define STX104_DAC_CHANA

#define STX104_DAC_CHANB_LSB

#define STX104_DAC_CHANB_MSB

7

#define STX104_DAC_CHANB, DACB

6

#define STX104_CLEAR_INTERRUPTS

8

#define STX104_ADC_STATUS

8

9

#define STX104_ADC_CONTROL

#define STX104_PACER_CLOCK_CONTROL

10

```

```

#define STX104_FIFO_FLAGS

10

#define STX104_ADC_CONFIGURATION

11

#define STX104_CT0_DATA

12

#define STX104_CT1_DATA

13

#define STX104_CT2_DATA

14

#define STX104_CT_CONFIGURATION

15

#define STX104_FIFO_DATA_STATUS

15

#define STX104_CONVERSION_DISABLE

1028

#define STX104 BURST MODE ENABLE

1029

#define STX104_BURST_FUNCTION

1030

#define STX104_EXTENDED_STATUS

1031

/* Applicable to Firmware Revision 080214H and beyond

/* offset (to be added to the

12

#define STX104_INDEXED_DATA_LSB

base address) */

#define STX104_INDEXED_DATA_MSB

13

#define STX104_INDEX_DATA

12

#define STX104_INDEX_POINTER

14

// indexed register array

#define STX104_GENERAL_CONFIGURATION

/* index */

2

#define STX104_INTERRUPT_SOURCE_SELECT

#define STX104_INTERRUPT_CONFIGURATION

#define STX104_INTERRUPT_THRESHOLD

#define STX104_DIGITAL_OUTPUT_CONFIGURATION

12

#define STX104_DIGITAL_INPUT_CONFIGURATION

#define STX104_TRIGGER_CONFIGURATION

16

#define STX104_TRIGGER_START_DELAY

20

#define STX104_ANALOG_INPUT_GENERAL_CONFIG

32

#define STX104_ANALOG_INPUT_FRAME_TIMER

36

#define STX104_ANALOG_INPUT_BURST_TIMER

#define STX104_ANALOG_INPUT_FRAME_MAX

44

#define STX104_ANALOG_INPUT_FRAME_COUNT

48

#define STX104_CONVERSION_DISABLE_INDEXED

64

#define STX104_BURST_MODE_ENABLE_INDEXED

65

#define STX104_BURST_FUNCTION_ENABLE_INDEXED

67

#define STX104_EXTENDED_STATUS_INDEXED

#define STX104_CT0_DATA_INDEXED

68

#define STX104_CT1_DATA_INDEXED

69

70

#define STX104_CT2_DATA_INDEXED

#define STX104_CT_CONFIGURATION_INDEXED

71

#define STX104_MISCELLANEOUS_OUTPUT_CONFIG

208

#define STX104_FIFO_DATA_AVAILABLE

224

#define STX104_FIFO_CONFIGURATION

228

#define STX104_SCRATCH_PAD

248

#define STX104_BOARD_ID

```

## 11.2 Software Strobe (Offset=0)

Software Strobe Register. Expanded version of the ADC Software Trigger Register.

### **Register Layout**

Offset = 0.

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|

| SSR7 | SSR6 | SSR5 | SSR4 | SSR3 | SSR2 | SSR1 | SSR0 |

#### **Bit Definitions**

| NAME     | DIRECTION | DEFAULT | DESCRIPTION              |

|----------|-----------|---------|--------------------------|

| SSR[7:0] | w         | -       | Software Strobe Register |

### **Description**

if triggering is disabled (TEN='0') then any value written to the Software Strobe Register will cause a ADC-sample or ADC-burst can occur depending on configuration.

if triggering is enabled (TEN='1') then specific values written to the Software Stobe Register will cause either an ADC-sample or ADC-burst or trigger signalling as shown below.